Резервированное запоминающее устройство

Иллюстрации

Показать всеРеферат

РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее блоки памяти, мажоритарный блок, первый и второй компараторы, причем одни входы блоков памяти являются адресными, а другие - управляющими входами устройства, выходы блоков памяти соединены с входамимажоритарного блока, выходы первого и второго блоков памяти подк.лючены к первым входам первого и второго компараторов, выход мажоритарного блока является информационным выходом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит третий компаратор, элемент И, формирователь импульсов и элемент задержки, причем выход третьего блока памяти соединс ; с первым входом третьего компаратора, выход мажоритарного блока подключен к вторым входам компараторов, выходы которых соединены с входами элемента И, выход которого подключен входу формирователя импульсов, выход которого подключен к второму входу элемента задержки, первый I вход которого соединен с другими входами блоков памяти, выход эле.мента задержки (Л является контрольным выходом устройства. IN5 СО С5 сд

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1129657

G 11 С 2900

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /

Н А ВТОРСНОМ,Ф СВИДЕТЕЛЬСТВУ ч 5

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3632994/24-24 (22) 10.08.83 (46) 15.12.84. Бюл. № 46 (72) Е. Ф. Колесник, В, Б. Масленников, Л. А. Альшанский и И. А. Насибуллин (53) 681.327.66(088.8) (56) 1. Авторское свидетельство СССР № 589623, кл. G 11 С 29/00, 1978.

2. Авторское свидетельство СССР № 710076, кл. G 11 С 17/00, 1980 (прототип), (54) (57) РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮ1ЦЕЕ УСТРОИСТВО, содержащее блоки памяти, мажоритарный блок, первый и второй компараторы, причем одни входы блоков памяти являются адресными, а другие — управляющими входами устройства, выходы блоков памяти соединены с входами. мажоритарного блока, выходы первого и второго блоков памяти подключены к первым входам первого и второго компараторов, выход мажоритарного блока является информационным выходом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит третий компаратор, элемент И, формирователь импульсов и элемент задержки, причем выход третьего блока памяти соединс; с первым входом третьего компаратора, выход мажоритарного блока подключен к вторым входам компараторов, выходы которых соединены с входами лемента И, выход которого подключен;. входу формировате |я импульсов, выход которого подключен к второму входу элемента задl ржки, первый вход которого соединен с другими входами блоков памяти, выход элемента задержки является контрольным выходом устройства.

1129657

5с

Изобретение относится к цифровой вычислительной технике и предназначено для использования в устройствах повышенной надежности, в частности в специализированных вычислительных машинах.

Известно резервированное запоминающее устройство, содержащее накопители, блок управления, входные и выходные коммутаторы, блоки свертки по модулю два, блок поразрядного сравнения, коммутатор, причем входы устройства соединены с соответствующими входами входных коммутаторов, выходы которых соединены с входами накопителей, их выходы через выходные коммутаторы соединены с входами соответствующих блоков свертки по модулю два, входами блока поразрядного сравнения и входами коммутатора,.выход которого является выходом устройства. Выходы блоков свертки по модулю два и блока поразрядного сравнения соединены с входами блока управления, выходы которого соединены с управляющими входами коммутатора, входных и выходных коммутаторов. Устройство позволяет осуществлять исправную работу даже при наличии отказов в накопителях. Это происходит за счет поразрядного сравнения информации, поступающей из накопителей, и в случае несовпадения, выявления неисправного накопителя — за счет осуществления свертки по модулю два поступающей информации (1) .

Недостаток такого устройства — сложность, обусловленная большим числом различных коммутаторов, необходимых для реализации требуемого алгоритма контроля и исправления информации.

Наиболее близко по технической сущности и достигаемому эффекту к изобретению резервированное запоминающее устройство, содержащее блоки памяти, хранящие идентичную информацию, причем выходы первого и второго непосредственно, а входы третьего через блок регенерации соединены с адресной шиной и шиной обращения. Выходы блоков соединены с входами мажоритарного элемента, кроме того, выходы первого и третьего блоков памяти соединены с первыми входами первого и второго компараторов соответственно, а выход второго блока памяти — с вторыми входами компараторов, которые производят поразрядное сравнение поступающей информации. Выход первого компаратора соединен с шиной «Останов» блоком контроля, блоком регенерации и управляющим входом ключа, предназначенного для подключения третьего блока памяти к шине питания при обнаружении несоответствия информации, поступающей из первого и второго блоков памяти. Блок регенерации предназначен для возобновления и и поддержания на входе третьего блока памяти информации, поступающей на входы первого и второго блоков, на время, необходимое для завершения переходных процессов в третьем блоке, вызванном его подключением к шине питания. Одновременно по шине останова в ЦВМ поступает сигнал с первого коммутатора, который блокирует информацию на всех регистрах ЦВМ на время ввода в работу третьего блока (2).

Недостатком прототипа является низкое быстродействие устройства, обусловленное (в случае исправной работы) временем, необходимым для гарантированного завершения переходных процессов в устройстве после подачи сигнала обращения от ЦВМ. Это время определяется с запасом на самые неблагоприятные сочетания внешних воздействий и параметров элементов, меняющихся от партии к партии от элемента к элементу, тогда как реальное время окончания переходных процессов при реальных условиях в реальном сочетании параметров элементов может оказаться значительно ниже расчетного. Кроме того, при обнаружении неисправности производится дополнительный останов ЦВМ для гарантированного завершения переходных процессов, вызванных подключением третьего блока к шине питания с учетом всех перечисленных факторов.

Цель изобретения — повышение быстродействия устройства.

Указанная цель достигается тем, что в резервированное запоминающее устройство, содержащее блоки памяти, мажоритарный блок, первый и второй компараторы, причем одни входы блоков памяти являются адресными, а другие — управляющими входами устройства, выходы блоков памяти соединены с входами мажоритарного блока, выходы первого и второго блоков памяти подключены к первым входам первого и второго компараторов, выход мажоритарного блока является информационным выходом устройства, введены третий компаратор, элемент И формирователь импульсов и элемент задержки, причем выход третьего блока памяти соединен с первым входом третьего компаратора, выход мажоритарного блока подключен к вторым входам компараторов, выходы которых соединены с входами элемента И, выход которого подключен к входу формирователя импульсов, выход которого подключен ко второму входу элемента задержки, первый вход которого соединен с другими входами блоков памяти, выход элемента задержки является контрольным выходом устройства.

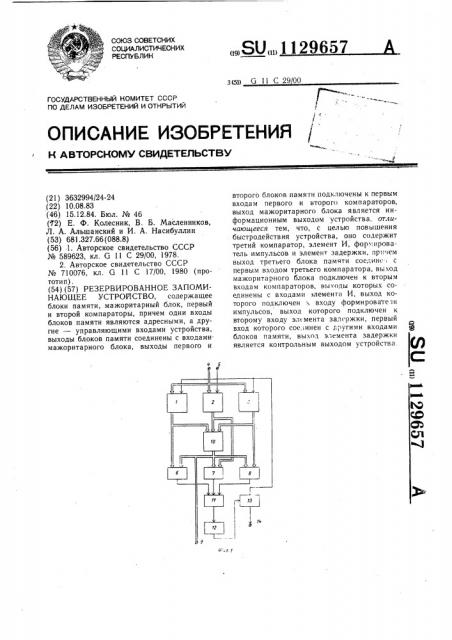

На фиг. 1 представлена структуоная схема предлагаемого устройства; на фиг. 2— временные диаграммы его работы.

Устройство содержит первый 1, второй 2 и третий 3 блоки памяти, входы которых сое1129657 динены с адресной шиной 4 и шиной 5 управления (обращения), а выходы — с первыми входами первого 6, второго 7 и третьего 8 компараторов соответственно, вторые входы которых соединены с шиной данных 9 и входом мажоритарного блока 10, входы которого соединены с выходами блоков 1, 2 и 3 памяти. Выходы компараторов 6, 7 и 8 соединены с входами элемента И 11, выход которого через формирователь 12 импульсов соединен с управляющим входом элемента

1О задержки 13, вход которого соединен с шиной 5 обращения, а выход — с шиной 14 готовности.

Устройство работает следующим образом

Сигналы, поступающие на адресную шину 4 и шину 5 обращения, запускают процессы выборки информации в блоках 1, 2 и 3 памяти. Переходным процессом, протекающим в этих блоках, соответствует появление случайной информации на выходах. По окончании переходных процессов на выходах всех блоков

20 памяти 1, 2 и 3 установится одинаковая информация, такая же информация установится и на выходе мажоритарного блока 10, а следовательно, и на вторых входах компараторов 6, 7 и 8 на выходах которых поя- 25 вится сигнал логической «1», соответствующий совпадению информации на входах компаратора. После того, как на выходах всех трех компараторов 6, 7 и 8 установится сигнал логической «1», с помощью элемента

И 11 производится сброс элемента задержки

13, который был запущен в режим выработки задержанного сигнала от шины 5 обращения.

Появление сигнала на шине 14 готовности свидетельствует о том, что переходные процессы в запоминающем устройстве закон- З5 чены и информация с шины данных 9 может считываться внешней средой. В случае неисправности в одном из блоков 1, 2 и 3 памяти, компаратор, соединенный с выходом неисправного блока, не выработает сигнал логической «1». после окончания переходных процессов, так как на второй вход этого компаратора поступает истинная информация, восстановленная с помощью мажоритарного блока 10, и совпадения информации на входах этого компаратора не будет 45

Следовательно, не будет выработан сигнал логической «1» элементом И 11 и не будет произведен сброс элемента задержки 13.

Сигнал, поступивший на лину 5 обращения в момент обращения к запоминающему устройству, возбуждает элемент задержки 13 и, через время, выбранное с учетом гарантированного окончания переходных процессов при самом неблагоприятном сочетании внешних воздействий и сочетаний параметров элементов, элемент задержки 13 вырабатывает задержанный сигнал, который поступит на шину 13 готовности, т.е. быстродействие запоминающего устройства при наличии неисправности в одном из блоков памяти будет не ниже быстродействия прототипа при исправной работе блоков памяти.

На фиг. 2 приняты следующие обозначения: а — сигнал обращения, поступивший из внешней среды на шину 5 обращения; б — информационные сигналы с выходов блоков 1, 2 и 3 памяти; в — сигнал с выхода элемента И 11; г — сигнал с выхода формирователя 12 импульсов; д — сигнал с выхо-, да элемента 13 задержки по шине готовности

14 во внешнюю среду.

Период времени t — t< соответствует невыбранному состоянию ЗУ. При этом выходы блоков 1, 2 и 3 памяти находятся, например, в состоянии с высоким выходным сопротивлением, что воспринимается мажоритарным блоком 10 и компараторами 6, 7 и 8 например, как коды, состоящие из логических «1».

Выход элемента И 11 находится в состоянии

«1», выход элемента задержки 13 находится в исходном состоянии (логическая «!»).

Сигналом обращения элемент 13 задержки переводится в возбужденное состояние (логический «О»), из которого он возвращается в исходное состояние либо по истечении определенного промежутка времени, либо принудительно, по сигналу, поступившему на его управляющий вход.

Период времени t1 — t соответствует переходному процессу выборки информации из блоков 1, 2 и 3 памяти, информация на их выходах случайна и неодинакова.

Момент времени t, соответствует установлению истинной информации, что фиксируется с помощью компараторов 6, 7 и 8, при этом элемент И 11 переходит из состояния логического «О» в состояние логической «1» (фиг. 2в). Передний фронт этого сигнала поступает на формирователь 12 импульсов, который вырабатывает импульс сброса (фиг. 2г) на управляющий вход элемента 13 задержки, который сбрасывается в исходное состояние (логическая «1», фиг.

2д). Переход из состояния логического «О» в состояние логической «!» на шине 14 готовности при наличии сигнала обращения на шине 5 обращения соответствует завершению переходных процессов в запоминающем устройстве в режиме выборки.

Использовав информацию с шины 9, снимает сигнал обращения с шины 5 обращения (момент t, фиг. 2а). В период времени t t < блоки 1, 2 и 3 памяти возвращаются к невыбранному состоянию. В этот период выход элемента И 11 соответствует значению логического «О», а элемент 13 задержки вновь переведен в возбужденное состояние теперь уже задним фронтом импульса обращения. Момент времени t „соответствует переходу всех блоков 1, 2 и 3 памяти в невыбранное состояние, что фиксируется компаратором 6, 7 и 8 и элементом И 11, а фор1129657

1 !

Рыг, Составитель О. Kiлаков

Редактор М. Келемеш Те ред И. Верес Корректор А. Тяско

Заказ 8975/41 Тираж 574 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5 филиал ППП «Патент», r. Ужгород, ул. Проектная, 4 мирователь 12 импульсов формирует сигнал сброса в исходное состояние элемента 13 задержки. Этот переход элемента 13 задержки при отсутствии сигнала обращения соответствует тому, что запоминающее устройство готово к новому обращению. В момент времени ts приходит сигнал нового .обращения. Информация, выбираемая из блоков

1, 2 и 3 памяти, например, соответствует информации, находящейся на выходах блоков при невыбранном состоянии (коды, состоящие из логических «1») и компараторы

6, 7 и 8 не фиксируют переходной процесс, формирователь 12 импульсов не формирует сигнал сброса и управляемый элемент 13 задержки, который был установлен в возбужденное состояние передним фронтом импульса обращения, возвратится в исходное состояние. Аналогично происходит возврат запоминающего устройства в невыбранное состояние (период времени tq — -t >), Г1ри наличии отказов в одном из блоков памяти процесс выдачи сигнала на шину 14 готовности производится аналогично, с той лишь разницей, что выход элемента И 11 во все время действия сигнала обращения находится в состоянии логического «0»..

Технико-экономическое преимущество предлагаемого устройства в сравнении с прототипом заключается в более высоком бы15 стродействи и.