Устройство для деления

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ, содержащее коммутатор, счетчик делимого , многодекадный счетчик делителя , блок фиксации окончания деления , блок задания кода делителя, счетчик частного, причем информационный вход KOMMytaTopa соединен с тактовым входом устройства, а выходы соединены с входами разрядов счет-, чика делимого, выход которого подключен к входу блока фиксации окончания деления, отличающееся тем, что, с целью упрощения устройства, вычитающие входы декад многодекадного счетчика делителя подключены к выходам коммутатора, а установочные входы декгщ многодекадного счетчика делителя подключены к выходам блока задания кода делителя, поразрядные выходы многодекадного счетчика делителя подключены к управляющим входам ком3 мутатора, выход старшего разряда многодекадного счетчика делителя соединен с входом разрешения записи многодекадного счетчика делителя -и с входом счетчика частного.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК ае ш) А

З(51) С 06 Р 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

J (I

ГОСУДАРСТВЕННЫЙ НОМИТЕТ "СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ н aBTOpCKOMV СВ ЩатВЪстви (21) 3647241/24-24 (22) 28.09.83 (46) ?3.1?.84. Бюл. № 47 (72) Т.Е.Замора и Г.В.Лукьянец (71) Специальное конструкторскотехнологическое бюро Физико-механического института AH Украинской CCP (53) 681.3(088.8) (56) 1. Авторское свидетельство СССР №- 903867, кл. G 06 F 7/52, 1982. 2. Авторское свидетельство СССР

¹ 809176, кл. G 06 F 7/52, 1981 (протбтип). (54)(57) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ, содержащее коммутатор, счетчик делимого, многодекадный счетчик делителя, блок фиксации окончания деления, блок задания кода делителя, счетчик частного, причем информационный вход коммутатора соединен с тактовым входом устройства, а выходы соединены с входами разрядов счет-, чика делимого, выход которого подключен к входу блока фиксации окончания деления, о т л и ч а ю щ ее с я тем, что, с целью упрощения устройства, вычитающие входы декад многодекадного счетчика делителя подключены к выходам коммутатора, а установочные входы декад многодекадного счетчика делителя подключены к выходам блока задания кода делителя, поразрядные выходы многодекадного счетчика делителя подключены к управляющим входам коммутатора, выход старшего разряда многодекадного счетчика делителя соединен с входом разрешения записи многодекадного счетчика делителя .и с входом счетчика частного.

S 11308

Изобретение относится к вычислительной технике .и может быть использовано в цифровых приборах для обработки результатов измерений, например, в составе автоматических систем 5 управления и контроля.

Известно устройство для деления, содержащее регистр делимого, регистр делителя, буферный регистр, ключ, входы которого подключены к первым выходам регистра делителя и буферного регистра соответственно, выход ключа подключен к входу счетчика частного и счетному входу триггера, блок фиксации окончания деления, 1У вход которого подключен к выходу регистра делимого, распределитель импульсов, элемент ИЛИ и две группы поразрядных элементов И, последовательно соединенных один с другим 111.20

Недостатками такого устройства . являются малое быстродействие и низкая точность,.связанная с возникновением сбоев при наличии в делителе нескольких находящихся рядом нулей.

Наиболее, близким по технической сущности к изобретению является устройство для деления, .которое содержит коммутатор тактовых импульсов, счетчик делимого, блок фиксации окончания деления, счетчик делителя, блок задания кода делителя, счетчик частного и блок сравнения, состоящий из поразрядных узлов сравнения Г2).

Известное устройство обладает более высоким быстродействием, что достигается уменьшением числа счетных импульсов, необходимых для вы- 4О полнения одного цикла вычитания, равного суммарному времени задержки распространения сигналов в устройстве, определяющегося временной задержкой сигналов в блоке сравнения, обладающем наинизшим быстродействием, по сравнению с другими структурными элементами устройства. Поэтому быстродействие известного устройства для деления ограничивается инерцион- 5О ностью входящего в него блока сравнения.

Цель изобретения — упрощение устройства и повьппение его быстродействия 55

Поставленная цель достигается тем, что в устройстве для деления, содержащем коммутатор, счетчик дели60 2 мого, блок фиксации окончания деления, блок задания. кода делителя, многодекадный счетчик делителя, счетчик частного, причем информационный вход коммутатора соединен с тактовым входом устройства, а выходы соединены с входами разрядов счетчика деI лимого, выход которого подключен к входу блока фиксации окончания деления, вычитающие входы декад много-. декадного счетчика делителя подключены к выходам коммутатора, установочные входы декад многодекадного счетчика делителя подключены к выходам блока задания кода делителя, поразрядные выходы многодекадного счетчика делителя подключены к управляющим входам коммутатора, выход старшего разряда многодекадного счетчика делителя соединен с входом разрешения записи многодекадного счетчика делителя и с входом счетчика частного.

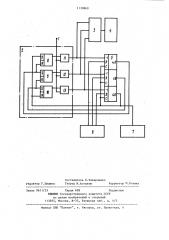

На чертеже приведена функциональная схема устройства.

Устройство для деления содержит тактовый вход 1, коммутатор 2, счет-, чик 3 делимого, блок 4 фиксации окончания деления, многодекадный счетчик

5 делителя, блок 6 задания кода делителя и счетчик 7 частного.

Коммутатор 2 состоит из нескольких, по числу разрядов, PS-триггеров 8-10 и стольких же элементов И

11-13, причем вход R первого (младшего) триггера 8 соединен с: входом

5 второго триггера 9, вход К второго триггера 9 — с входом Я третьего и так далее, а вход 2 последнего (старшего) триггера соединен с входом 5 первого триггера. Выходы триггеров подключены к первым входам элементов И, вторые входы которых объединены и являются входом коммутатора, а К-входы триггеров являются управляющими входами коммутатора 2, которые подключены к поразрядным выходам " 0" многодекадного счетчика

5 делителя. Выход счетчика 3 подключен к блоку 4 фиксации окончания деления. Установочные входы многодекадного счетчика 5 соединены с блоком 6 задания кода делителя. Старший поразрядный выход " 0" многодекадиого счетчика 5 делителя подключен к входу разрешения записи этого же счетчика и к входу счетчика 7 частного, с которого снимается результат деления.

Устройство работает следующим образом.

В момент запуска устройства в счетчик 5 записывается код делителя с блока 6 задания кода делителя.

Тактовые импульсы с входа 1 поступают на поразрядные входы счетчика.3 делимого и многодекадного счетчика 5 делителя через коммутатор 2.

При этом тактовые импульсы проходят на выход того элемента И 11-13, со-. ответствующий которому триггер 8-10 находится в состоянии логической "1", Например, тактовые импульсы поступают с выхода элемента 11 на входы первых разрядов счетчиков 3 и 5, которые работают в режиме вычитания., Процесс продолжается до обнуления первого разряда счетчика 5. В этот момент на первом выходе счетчика 5 появится сигнал, переключающий триггер 9 в состояние "0-, а триггер 10. в состояние "1". После этого такто> вые импульсы проходят на вторые входы счетчиков 3 и 5. Так. устройство работает до тех пор, пока старший разряд счетчика 5 не будет равен

"0". По сигналу с выхода старшего разряда счетчика 5 коммутатор вновь подключает к тактовому входу 1 первые разряды счетчиков 3 и 5, в счетчик 5 еще раз переписывается код делителя из блока задания кода делителя, и в счетчик 7 частного записывается "1". На этом один цикл вычитания операции деления заканчивается,. и начинается второй аналогичный цикл. Операция деления заканчивается после того, как счетчик

3 делимого достигает состояния "0", которое фиксируется блоком 4.

В случае, когда один из разрядов делителя равен нулю, устройство

30860 4 работает следующим образом. После обнуления предыдущего, не равного нулю разряда счетчика делителя, триггер следующего разряда, напри-5 мер 10, переключается в состояние

"1". Соответствующий этому триггеру элемент И 13 пропускает фронт тактового импульса с входа 1 на вход счетчика 5. Поскольку соответствующий разряд счетчика 5 равен нулю, то на его выходе "< 0" одновременно с фронтом тактового импульса (если пренебречь временем распространения) появляется сигнал, который переклю15 чает триггер 10 в состояние "0", а триггер 11 — в состояние "1 . Если и следующий разряд кода делителя равен нулю, то триггер 11 возвращается в состояние "0".. При этом счет20. чик 3 не должен срабатывать от импульсов, длительность которых меньше длительности тактовых импульсов.

Предлагаемое устройство позволяет производить операцию деления в

25 произвольной форме счисления: шестнадцатиричной, десятичной и другие в зависимости от конструкции применяемых блоков.

Многодекадный счетчик делителя

30 используется в режиме вычитания и в нем задействованы входы параллель- ной записи информации и выходы пере полнения " 0". Это существенно упрощает устройство и значительно уменьшает время задержки распространения тактовых импульсов от такто-, I ного входы устройства до управляющих входов коммутатора.

Таким образом, предлагаемое уст4О ройство является более простым по сравнению с известными устройствами и обладает более высоким быстродействием.

1130860

Составитель F..Çàõàð÷åíêo

Техред И.Асталош Корректор М.Розман

Редактор Г.Цицика

Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 9611/35

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4