Вычислительное устройство

Иллюстрации

Показать всеРеферат

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее счетчик и сумматор, о т личающеес-я тем, что, с целью расширения области применения путем обеспечения возможности выполнения операций умножения, в него введены коммутатор, регистр, элемент НЕ, I элемент ИЛИ, элемент 2И-ИЛИ, первый вход которого соединен с первым информационным входом устройства и первьпч входом элемента ИЛИ, второй вход которого соединен с вторым информационным входом устройства и вторым входом элемента 2И-ИЛИ, третий вход которого соединен с входом выбора режима устройства, четвертый вход элемента 2И-ИЛИ объединен со своим первым входом, выход элемента 2И-ИЛИ соединен со счетным входом счеТчика, первым управляющим входом коммутатора и входом элемента НЕ, выход которого соединен с вторым управляющим входом коммутатора, первая группа информационных входов которого соединена с разрядными выходами счетчика соответственно, вторая группа информационных входов коммутатора соединена с разрядными выходами счетчика со сдвигом на один разряд в сторону старших разрядов, причем вход старшего разряда первой группы.информационных входов коммутатора соединен с шиной логического О, вход младшего разряда второй группы информационных входов коммутатора соединен с шиной логической 1, выходы коммутатора (Л соединены с входами (п+1) младших разрядов первого слагаемого сумматора , входы первого слагаемого (п-1) старших разрядов которого соединены с шиной логического О (где п - разрядность счетчика), разрядные выходы сумматора соединены соответствен00 О X 3d но с информационными входами регистра , разрядные вьпсоды которого соединены соответственно с входами второго слагаемого сумматора, тактовый вход регистра соединен с выходом мента ИЛИ.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1130862 зШ G 06 F 7/544 с ."

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМ У СВИДЕТЕЛЬСТВУ

Ссс,с, с с, 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 36441 75/24-24 (22) 22.09.83 (46) 23.12.84 Бюл. Ф 47 (72) А.А.Филимонов и И.Г.Цмоць (53) 681. 325 (088. 8) (56) 1. Мельников А.А. и др. Обработка частотных и временных импульсных сигналов. М., "Энергия", 1976, с. 88.

2. Авторское свидетельство СССР

9. 769537, кл. С 06 F 7/552, 1980 (прототип). (54)(57) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее счетчик и сумматор, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения путем обеспечения возможности выполнения операций умножения, в него введены коммутатор, регистр, элемент НЕ,, элемент ИЛИ, элемент 2И-ИЛИ, первый вход которого соединен с первым информационным входом устройства и первым входом элемента ИЛИ, второй вход которого соединен с вторым информационным входом устройства и вторым входом элемента 2И-ИЛИ, третий вход которого соединен с входом выбора режима устройства, четвертый вход элемента 2И-ИЛИ объединен со своим первым входом, выход элемента 2И-ИЛИ соединен со счетным входом счетчика, первым управляющим входом коммутатора и входом элемента НЕ, выход которого соединен с вторым управляющим входом коммутатора, первая группа информационных входов которого соединена с разрядными выходами счетчика соответственно, вторач группа информационных входов коммутатора соединена с разрядными выходами счетчика со сдвигом на один разряд в сторону старших разрядов, причем вход старшего разряда первой группы.информационных входов коммутатора соединен с шиной логического 0", вход младшего разряда второй группы информационных входов коммутатора соединен с шиной логической " 1", выходы коммутатора соединены с входами (п+1) мпадших разрядов первого слагаемого сумматора, входы первого слагаемого (n-1) старших разрядов которого соединены с шиной логического "0" (где n — разрядность счетчика), разрядные выходы сумматора соединены соответственно с информационными входами регистра разрядные выходы которого соединены соответственно с входами второго слагаемого сумматора, тактовый вход регистра соединен с выходом элемента ИЛИ.

4 11308

Изобретение относится к вычислительной технике и может быть исполь-,; зовано в цифровых измерительных приборах, а также для обработки информации, представленной число-импульсным кодом.

Известен квадратор, содержащий двоичный счетчик, линию задержки, триггер, сумматор и элементы И Ц .

Недостатками такого квадратора яв- 10 ляются сложность схемой реализации и ограниченные функциональные возможности.

Наиболее близким по технической сущности к предлагаемому является 15 устройство, содержащее двоичный счетчик, разрядные выходы которого соединены с первыми входами элементов И, выходы которых соединены с разрядными входами сумматора, информацион- 20 ный .вход квадратора соединен со счетным входом триггера второго разряда двоичного счетчика и вторыми входами элементов И (2g.

Недостатком устройства является 25 невозможность выполнения операции умножения.

Цель изобретения — расширение области применения путем обеспечения возможности выполнения операций воз- gp ведения в квадрат и умножения.

Поставленная цель достигается тем, что в вычислительное устройство, содержащее счетчик и сумматор, дополнительно введены коммутатор, регистр,З5 элемент. HE элемент ИЛИ, элемент

2И-ИЛИ, первый вход которого соединен с первым информационным входом устройства и первым входом элемента

ИЛИ, второй вход которого соединен 40 с вторым информационным входом устройства и вторым входом элемента 2ИИЛИ, третий вход которого соединен. с входом выбора режима устройства, четвертый вход элемента 2И-ИЛИ объе- 45 динен со своим первым входом, выход элемента 2И-ИЛИ соединен .со счетным входом счетчика, первым управляющим входом коммутатора и входом элемента НЕ, выход которого соединен с вторым управляющим входом коммутатора, первая группа информационных входов которого соединена с разрядными выходами счетчика соответственно, вторая группа информационных входов 55 коммутатора соединена с разрядными выходами счетчика со сдвигом на один разряд в сторону старших разрядов, 62 2 причем вход старшего разряда первой группы информационных входов комму- . татора соединен с шиной логического

"0", вход младшего разряда второй группы информационных входов коммутатора соединен с шиной логической

"1", выходы коммутатора соединены с входами (и+1) младших разрядов первого слагаемого сумматора, входы первого слагаемого Ь -1) старших разрядов которого соединены с шиной логического "0" (где n — - разрядность счетчика), разрядные выходы сумматора соединены соответственно с информационными входами регистра, разрядные выходы которого соединены соответственно с входами второго слагаемого сумматора, тактовый вход регистра соединен с выходом элемента ИЛИ.

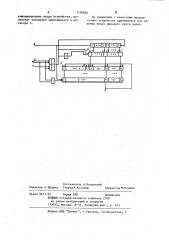

На чертеже показана блок-схема вычислительного устройства.

Квадратор содержит счетчик 1, коммутатор 2, элемент НЕ 3, сумматор 4, регистр 5, элемент 2И-ИЛИ 6, элемент

ИЛИ 7, вход 8 сброса устройства, первый и второй информационные входы

9 и 10 устройства соответственно, вход 11 задания режима.

Работа устройства при выполнении операции возведения в квадрат основана на реализации зависимости

4+3+i++(Z -

° Работа устройства при выполнении операции умножения сводится к выполнению операции возведения в квадрат меньшего из перемножаемых чисел, и прибавлению к полученному результату этого меньшего числа такое количество раз, которое равно разности между перемножаемыми числами ф + rn (K - и, и Ри < к;

Ф К=

К + К (-К), пЕи ИЧ>К, где m u k — перемножаемые числа.

Перед началом работы устройства на выход 8 сброса устройства подает) ся импульс отрицательной полярности, который производит установку счетчика 1 и регистра 5 в нулевое состояние .

Для выполнения устройством операции возведения в квадрат на вход 11 . выбора режима необходимо подать потенциал логической " 1". Число, возводимое в квадрат, поступает по первому информационному входу 9 импульсами положительной полярности. На второй информационный вход 10 устрой30862 4 положительной полярности, равный по длительности импульсам на информационных входах устройства. Первый импульс с выхода элемента 2И-.ИЛИ 6 поступает на второй управляющий вход коммутатора 2 и разрешает прохождение информации с вторых информационных входов на входы первого слагаемого сумматора 4. На последнем

10 происходит суммирование информации с выхода коммутатора 2 (...0001) с содержимым регистра 5 (...0000).

Задним фронтом первбго импульса, поступившего на тактовый вход регистра 5, в него записывается результат суммирования ...0001, а задним фрон.том первого импульса, приходящего на счетный вход счетчика 1, его состояние изменяется с ...0000 на

gp ...0001.

Дальнейшая работа устройства до момента прекращения импульсов на одном из информационных входов проходит аналогично.

25 Когда на одном из информационных входов устройства прекратятся импуль сы, значит по этому входу поступало меньшее число, и этот информационный вход устройства до конца умножения находится. в нуле. Наличие нуля на одном из информационных входов устройства устанавливает выход элемента 2И-ИЛИ6 в нуль, который, проходя через элемент НЕ 3, инвертируется, поступает на первый управляющий вход

35 коммутатора 2 и разрешает прохождение информации с первых информационных входов на входы первого слагаемого сумматора 4.

45

При выполнении устройством операции умножения. на вход 11 выбора режима необходимо подать потенциал логического "О . Перемножаемые числа 50 поступают в квадратор синхронно импульсами положительной полярности и одинаковой длительности по первому

9 и второму 10 информационным входам.

По приходу первых импульсов перемно- 55 жаемых чисел на.первый и второй входы элементов 2И-ИЛИб и ИЛИ7 на выходах этих элементов получают импульс

3 11 ства при этом подается потенциал логического "0". Первый импульс числа с первого информационного входа 9 квадратора, проходя через элемент

ИЛИ 7, поступает на счетный вход счетчика 1 и на второй управляющий вход коммутатора 2. Этот же импульс, проходя через элемент HJIH 7, поступает на тактовый вход регистра 5. Единица на втором управляющем входе коммутатора 2 разрешает прохождение на его выход информации с вторых информационных входов (в данном случае ...0001). Данная информация на выходе коммутатора 2 находится в тече;ние длительности импульса, за это время она просуммируется .с содержи- мым регистра 5(fP<53=...000). Задним фронтом (перепадом уровня с "1" в . "0") первого импульса, поступившего на тактовый вход регистра 5, происходит запись. резулЬтата суммирования (...0001) в регистр 5.

Задним фронтом первого импульса, поступившего на счетный вход счетчика 1,.его содержимое увеличивается на 1 и равняется ...0001.

С приходом второго импульса на вход 9 в течение длительности этого импульса на выход коммутатора 2 поступает информация с вторых информационных входов (...011), которая суммируется с содержимым регистра 5 ((Pg5)=...0001). Результат суммирования (...0100) записывается в регистр

5 задним фронтом второго импульса, поступившего на его тактовый вход.

Задним фронтом второго импульса, поступившего на счетный вход счетчика, его содержимое увеличивается на 1 и равняется ...0010.

Дальнейшая работа устройства при выполнении операции возведения в квадрат проходит аналогично.

Результат возведения в квадрат хранится в регистре 5.

Следующий импульс большего из перемножаемых чисел, поступивший в квадратор, проходит через элемент

ИЛИ7 и задним фронтом записывает в регистр 5 результат суммирования содержимого регистра 5 (квадрат меньше.

ro числа) с информацией на выходах коммутатора 2 (меньшее число).

Дальнейший процесс умножения проходит аналогично, т.е. по каждому заднему фронту поступившего импульса в регистр 5 записывается результат суммирования содержимого регистра 5 с информацией на выходах коммутатора

2 (меньшее число) °

Процесс умножения заканчивается па прекращению прихода импульсов на. 1130862

Составитель А.Казанский

Редактор P.Цицика ТехредИ.Асталош Корректор М.Розман

Заказ 9611/35 Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", .r.Óæãoðîä, ул.Проектная, 4 информационные входы устройства, ре1 зультат умножения записывается в регистре 5.

По сравнению с известным предла гаемое устройство применяется для решения более широкого круга задач.