Распределитель

Иллюстрации

Показать всеРеферат

РАСПРЕДЕЛИТЕЛЬ, содержащий многоустойчивый пересчетный блок с п выходами и N элементов И-НЕ (где N - число выходов распределителя, а 1 1 п i N ), причем i -и выход многоустойчивого пересчетного блока подключен к первым входам элементов И-НЕ с номерами к ri+t(, 1,2, ..., (Vh-l), входы сброса и сдвига многоустойчивогсг пересчетного блока являются соответствующими входами распределителя , а выходы элементов И-НЕ являются выходами распределителя, отличающийся тем, что, с целью упрощения распределителя, в него введены N/(n-1) ячеек памяти по одной на каждые из h-1 элементов И-НЕ, составляющих группы, причем каждая ячейка памяти состоит из двухи трехвходового элементов И-НЕ с перекрестными связями, причем выход трехвходового элемента И-НЕ первой ячейки памяти и выходы двухвходовых элементов И-НЕ других ячеек памяти соединены с вторыми входами элементов И-НЕ соответствукйщх групп, вторые входы трехвходовых элементов И-НЕ ячеек памяти подключены к входу сброса многоустойчивого пересчетного блока, выход (n-l)-ro элемента И-НЕ р-й группы (n-1)-1 соединен t вторым входом двухвходового элемента И-НЕ (р+1)-й ячейки памяти, а выход последнего элемента И-НЕ последней группы соединен с третьим входом трехвходового элемента И-НЕ первой ячейки памяти, выход первого элемента И-НЕ -й группы З t{,N/(п -1)3 соединен с третьим входом грехвходового элемента И-НЕ ()-й ячейки памяти, выход первого элемента И-НЕ второй группы соеСО динен свтор1 в входом двухвходового элемента И-НЕ первой ячейки памяти, со а выход первого элемента И-НЕ первой группы - с третьим входом трехвходового элемента И-НЕ последней ячейки |Памяти.

„,Я0.„1130901

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3619791/24-24 (22) 13.07 ° 83 (46) 23. 12 . 84 . Бюл. У 47 (72) Л.П.Петренко (53) 681.3?7.66(088.8) (56) 1. Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств.

И., "Советское радио", 1975, с. 285, рис. 6. 19.

2. Там же, с. 285, рис. 6, 18(прототип}. (54) (57) РАСПРЕДЕЛИТЕЛЬ, содержащий многоустойчивый пересчетный блок с и выходами и М элементов И-НЕ (где

М вЂ” число выходов распределителя, а 1 (n (М), причем j -й выход многоустойчивого пересчетного блока подключен к первым входам элементов

И-НЕ с номерами к +«.(1(=0, 1,2,..., М//n-1), входы сброса и сдвига многоустойчивого пересчетного блока являются соответствующими входами распределителя, а вьиоды элементов И-НЕ являются выходами распределителя, отличающийся тем, что, с целью упрощения распределителя, в него введены Й/(п-1) ячеек памяти по одной на каждые из п-1 элементов

И-НЕ, составляющих группы, причем з«5в С 11 С 19/00; Н 03 К 27/00 каждая ячейка памяти состоит иэ двухи трехвходового элементов И-НЕ с перекрестными связями, причем выход трехвходового элемента И-НЕ первой ячейки памяти и выходы двухвходовых элементов И-НЕ других ячеек памяти соединены с вторыми входами элементов И-НЕ соответствующих групп, вторые входы трехвходовых элементов

И-НЕ ячеек памяти подключены к входу сброса многоустойчивого пересчетного блока, выход (и-1)-ro элемента И-НЕ р-й группы (1 рай/(n -1)-1) соединен с вторым входом двухвходового элемента И-НЕ (р+1)-й ячейки памяти, а выход последнего элемента I

И-НЕ последней группы соединен с третьим входом трехвходового элемента И-НЕ первой ячекки памяти, выход первого элемента И-НЕ О.-й группы (34ф <М/(n-1)3 соединен с третьим вхо- а дом трехвходового элемента И-НЕ (g-1)-й ячейки памяти, выход перво0иий го элемента И-НЕ второй группы соединен с вторым входом двухвходового М элемента И-НЕ первой ячейки памяти, 4 а выход первого элемента И-НЕ первой «© группы — с третьим входом трехвходо- «,", ) вого элемента И-НЕ последней ячейки lama

«памяти.

1 1130

Изобретение относится к вычислительной технике и может быть использовано пои построении распределителей.

Известен распределитель, выполненный на многостабильном триггере и регистре (1).

Недостатком распределителя является большая аппаратурная избыточность при его реализации.

Известен также распределитель, содержащий первый и второй многоустойчивые пересчетные блоки, входы которых подключены к входу сдвига, а выходы соединены с соответствующими шинами матричного дешифратора, выполненного на элементах И L2.1, Недостатком известного распределителя является большая аппаратурная избыточность, поскольку требуются два многоустойчивых пересчетнык блока.

Цель изобретения — упрощение распределителя.

Поставленная цель. достигается тем, что в распределитель, содержащий многоустойчивый пересчетный блок с и выходами и И элементов И-НЕ (где М— число выходов распределителя, а

1<в<И), причем i-й выход многоустойчивого пересчетного блока подключен к первым входам элементов И-НЕ

30 с номерами к n+ l(k0, 1,2,...,И/п-1), входы сброса и сдвига многоустойчивого пересчетного блока являются соответствующими входами распределителя, а выходы элементов И-НЕ являются выходами распределителя, введены H/(n -1) ячеек памяти по одной на каждые из п-1 элементов И-НЕ, состав.» ляющих группы, причем каждая ячейка памяти состоит из двух- и трехвходо- 4О вого элементов И-НЕ с перекрестными связями, выход трехвходового элемента И-НЕ первой ячейки памяти и выходы двухвходовых элементов И-НЕ других ячеек памяти соединены с вторы- 4> ми входами элементов И-НЕ соответствующих групп, вторые входы трехвходовых элементов И-НЕ ячеек памяти подключены к входу сброса многоустойчивого пересчетного блока, выход (и -1)- о го элемента И-НЕ р-й группы (1<р<й/(n-1)-1) соединен с вторым входом двухвходового элемента И-НЕ (р+t)-й ячейки памяти, а выход последнего элемента И-НЕ последней груп- 55 пы соединен с третьим входом трехвходового элемента И-HE первой ячейки памяти, выход первого элемента

901 2

И-НЕ j-й группы (3gg<й/(ь-1) соединен с третьим входом трехвходового элемента И-НЕ (q-1)-й ячейки памяти, выход первого элемента И-НЕ второй группы соединен с вторым входом двухвходового элемента И-НЕ первой ячейки памяти, а выход первого элемента

И-НЕ первой группы — с третьим входом трехвходового элемента И-НЕ ,последней ячейки памяти.

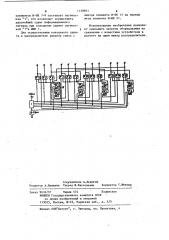

На чертеже изображена принципиальная электрическая схема распределителя.

Распределитель содержит многоустойчивый пересчетный блок (МПБ) 1, имеющий входы "Сдвиг" 2 и "Сброс" 3, И элементов И-НЕ 4-15, p/(n-1) ячеек 16 памяти, которые состоят из двухвходовых элементов И-НЕ 17-20 и трехвходовых элементов И-НЕ 21-24.

Работа распределителя заключается в следующем.

При подаче на вход "Сброс" 3 управляющего сигнала на первом выходе

ИПБ 1 устанавливается единичный сигнал. Одновременно на выходе трехвходового элемента И-НЕ 21 первой ячейки 16 памяти устанавливается логическая единица, которая поступает на второй вход двухвходового элемента

И-НЕ 17 этой же ячейки 16 памяти и на вторые входы элементов И-НЕ 4-6 первой группы. При этом на выходах двухвходовых элементов И-НЕ 18-20 остальных ячеек памяти устанавливается логический "О", в результате на выходах элементов И-НЕ 5-15 устанавливается логическая "1", а на выходе элемента

И-НЕ 4 — логический "0" (информационный).

При подаче сигнала на вход "Сдвиг"

2.единичный сигнал с первого выхода

МПБ 1 переключается на второй выход, в результате на первом входе элемента

И-НЕ 5 появляется логическая "1", а на его выходе устанавливается информационный "0".

При подаче очередного импульса на вход "Сдвиг" 2 с третьего выхода МПБ 1 на первый вход элемента

И-НЕ 6 поступает единичный сигнал, что приводит к появлению информационного сигнала на его выходе. Одновременно с выхода элемента И-НЕ 6 логический "0" поступает на второй вход двухвходового элемента И-НЕ 18 второй ячейки памяти. В результате чего на вторые входы второй rруппы

Сос,уавитель А.Дерюгин

Редактор А.Шишкина Техред Ж.Кастелевич Корректор C..Шекмар

Заказ 9616/37 Тираж 574 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, .Ж-35, Раушская наб,, д. 4/5

Филиал ППП"Патент", г. Ужгород, ул. Проектная, 4

3 1 элементов И-HE 7-9 поступает логичес1! \ I кая 1, что позволяет осуществить дальнейший сдвиг информационного сигнала при кольцевом сдвиге логической "1 "в ИНБ 1.

Для осуществления кольцевого сдвига в распределителе введена связь с

13090 1 4 выхода элемента И-НЕ 15 на третий вход элемента И-НЕ 21.

Использование изобретения позволяет уменьшить затраты оборудования по сравнению с известным устройством в расчете на один выход распределителя.