Ячейка памяти

Иллюстрации

Показать всеРеферат

ЯЧЕЙКА ПАМЯТИ, содержащая ,два триггера с непосредственными свя-зями , выполненные на первом и втором, . третьем и четвертом транзисторах типап-р-h, пятый, шестой и блокировочный транзисторы типа п -рп, токозадаюпц1й и опорный транзисторы типа р -п-р и пять транзисторов связи типар-п-р, эмиттеры первого, второго , третьего, четвертого, пятогоj шестого и блокировочного транзисторов , базы токозадающего и опорного транзисторов и базы транзисторов связи соед 1нены с шиной нулевого потенциала , блокировочного .и эмиттер токозадающего транзисторов - с тактовой шиной, соответствую1ций коллектор блокировочного транзистора - с входной шиной, соответствующие коллекторы токозаданицего транзистора - с ба- , зами первого , второго, третьего и четвертого.транзисторов, эмиттер опорного транзистора - с шиной питания , эмиттеры первого, второго и третьего транзисторов связи - с соответствующими коллекторами блокировочного и опорного транзисторов, коллекторы первого и третьегб транзисторов связи - соответственно с базами первого и третьего транзисторов, отличающаяся тем, что, с целью увеличения точности и уменьшения потребляемой мощности, соответствующий коллектор первого, второго , третьего и четвертого, пятого и шестого транзисторов соединен с собственной базой, дополнительные коллекторы первого и третьего транзисторовсоединены с выходной шиной, дополнительный коллектор второго транзистора и коллектор пятого транзистора связи - с базой пятого транзистора ,дополнительный коллектор кото:о рого - с базой третьего транзистора,эмит hO 9 4: lib теры четвертого и пятого транзисторов связи - с соответствующими коллекторами опорного и блокировочного транзисторов , коллекторы второго и четвертого транзисторов связи - с базами второго и четвертого тр,анзисторов , соответствующие дополнительные коллекторы шестого транзистора - с базами первого и третьего транзисто ров, а его база - с входной шиной.

ае 01) COOS COBETCHHX

РЕСПУБЛИН з(ю Н 03 К 3/29

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

OllHCAHHE ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ (2 I) 3636537/24-21

:(22) 26.08.83 (46) 30.12.84. Бюл. Р 48 (72) А.В.Ерохин и Ю.И.Рогозов (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (53) 621.375.083(088.8) (56) 1. Dao Т.Т., Ме.Cluskey E.J.

Russell L.Ê. Multivalued Integrated

Injection Loguc — "IEEE Transacation

on Computers", vol. С-26, Ф 12, 1977, .р. 1240, Е1я. 15.

2. Авторское свидетельство СССР

В 705523, кл. G 11 С 19/40, 1977 (прототип). (54) (5?) ЯЧЕЙКА ПАМЯТИ, содержащая ,два триггера с непосредственными свя зями, выполненные на первом и втором, третьем и четвертом транзисторах типа.П -p- h, пятый, шестой и блокировочный транзисторы типа n --р- 0, токозадающий и опорный транзисторы типа p --h-р и пять транзисторов связи типа р -h-p, эмиттеры первого, второго, третьего, четвертого, пятого, шестого и блокировочного транзисторов, базы токозадающего и опорного транзисторов и базы транзисторов связи соединены с шиной нулевого потенциала, база блокировочного и эмиттер токозадающего транзисторов — с тактовой шиной, соответствующий коллектор блокировочного транзистора — с входной шиной, соответствующие коллекторы токоэадающего транзистора — с базами первого, второго, третьего и четвертого. транзисторов, эмиттер опорного транзистора — с шиной питания, эмиттеры первого, второго и третьего транзисторов связи — с соответствующими коллекторами блокировочного и опорного транзисторов, коллекторы первого и третьего транзисторов связи — соответственно с базами первого и третьего транзисторов, отличающаяся тем, что, с целью увеличения точности и уменьшения потребляемой мощности, соответствующий коллектор первого, второго, третьего и четвертого, пятого и шестого транзисторов соединен с собственной базой, дополнительные коллекторы первого и третьего транзисторов соединены с выходной шиной, дополнительный коллектор второго транзистора и коллектор пятого транзистора связи — с базой пятого тран- зистора,дополнительныйколлектор которого — с базой третьего транзистора,эмиттеры четвертого и пятого транзисторов .связи — с соответствующими коллекторами опорного и блокировочного транзисторов, коллекторы второго и четвертого транзисторов связи - с базами второго и четвертого транзисторов, соответствующие дополнительные коллекторы шестого транзистора — с базами первого и третьего транзисто ров, а его база — с входной шиной.

1132344

Изобретение относится к микроэлектронике и предназначено для построения И Л многоуровневых БИС обработки и хранения информации.

Известен четырехуровневый 3 -триггер, содержащий квантиэатор, в цепи обратной связи которого стоит токовый повторитель, и схему управления f1), Недостатками его является слож- 10 ность.и большая потребляемая мощность.

Наиболее близким к изобретению по технической сущности является ячейка памяти, содержащая три триг- 15 гера с непосредственными связями, выполненные на шести транзисторах типа n --p-n, блокировочный транзистор типа и --р-п, токозадающий и опорный транзисторы типа р -и-р и 20 шесть транзисторов связи типа p-n-p, эмиттеры транзисторов и блокировочного транзистора, базы токозадающего и опорного транзисторов и базы транзисторов связи соединены с шиной 25 нулевого потенциала, база блокировочного и эмиттер токозадающего транзистора — с тактовой шиной, соответствующий коллектор блокировочного транзистора — с входной шиной, соответствующие коллекторы токозадающего транзистора — с обозами транзисторов, эмиттер опорного транзистора— с шиной питания, эмиттеры первого, второго и третьего транзисторов связи — с соответствующими колле- -. кторами блокировочного и опорного транзисторов, коллекторы первого и третьего транзисторов связи — соответственно с базами первого и третье-40 го трайзисторов, коллекторы четвертого, пятого и шестого транзисторов связи — с выходом ячейки.

Недостатками этой ячейки памяти являются малая точность преобразова- 45 ния, вызванная гистерезисом триггеров — компараторов, и большая потребляемая мощность в режиме хранения °

Цель изобретения — увеличение точности преобразования и уменьшение

50 потребляемой мощности в режиме хранения.

Поставленная цель достигается, тем, что в ячейке памяти, содержащей два триггера с непосредственнычи . 55 связями, выполненные на нервом и втором, третьем и четвертом транзисторах типа и -Р-п, пятый, шестой и блокировочный транэистооы типа н -р-п, токозадающий и опорный транзисторы типа р -n- р и пять транзисторов свя- зи типа p --n-p, эмиттеры первого, второго, третьего, четвертого, пятого, шестого и блокировочного транзисторов, базы токозадающего и опорного транзисторов и базы транзисторов связи соединены с шиной нулевого потенциала, база блокировочного и эмиттер токозадающего транзисторов — с тактовой шиной, коллектор блокировочного транзистора — с входной шиной, соответсвующие коллекторы токозадающего транзистора — с базами первого, второго, третьего и четвертого транзисторов, эмиттер опорного транзистора с шиной питания, эмиттеры первого, второго и третьего транэисторбв связи — с соответствующими коллекторами блокировочного и опорного транзисторов, коллекторы первого и третьего транзисторов связи — соответственно с базами первого и третьего транзисторов, соответствующий коллектор первого, второго, третьего, четвертого, пятого и шестого транзисторов соединен с собственной базой, дополнительные коллекторы первого и третьего транзисторов — с выходной шиной, дополнительный коллектор второго транзистора и коллектор пятого транзистора связи — с базой пятого транзистора, дополнительный коллектор которого — с базой третьего транзистора, эмиттеры четвертого и пятого транзисторов связи — с соответствующими коллекторами опорного.и блокировочного транзисторов, коллекторы второго и четвертого транзисторов связи — с базами второго

I и четвертого транзисторов, соответствующие дополнительные коллекторы шестого транзистора — с базами первого и третьего транзисторов, à его база — с входной шиной.

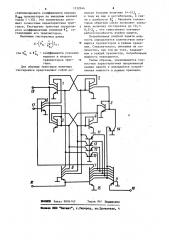

На чертеже представлена принципиальная схема предложенной ячейки,памяти.

Ячейка памяти содержит два триггера с непосредственными связями, выполненные на первом и втором, третьем и четвертом транэисторах—

1-4, пятый, шестой и блокировочный транзисторы 5-7 типа 11 -)-h, токозадающий и опорный транзисторы 8 и 9 и пять транзисторов 10-14 типа p --h-f), эмиттеры первого, второго, третьего, 4 4

3 113234 четвертого, пятого и шестого и блокировочного транзисторов 1-7, базы токозадающего и опорного транзисторов 8 и 9 и базы транзисторов связи

10-14 соединены с шиной нулевого потенциала !5, база блокировочного и эмиттер токозадающего транзисторов

7 и 8 — с тактовой шиной 16, коллек-. тор блокировочного транзистора 7— с входной шиной !7, соответствующие 1О коллекторы токозадающего транзистора 8 — с базами первого, второго, третьего и четвертого транзисторов

1-4, эмиттер опорного транзистора 9— с шиной питания 18, эмиттеры первого, 15 второго и третьего транзисторов связи 10 — 12 с соответствующими колле-.;торами блокировочного и опорного транзисторов 7 и 9, коллекторы первого и третьего транзисторов свя- 20 зи 10 и 12 — соответственно с базами первого и третьего транзисторов 1 и 3, соответствующий коллектор первого, второго, третьего, четвертого, пятого и шестого транзисторов 1-6 соединен с собственной базой, дополнительные коллекторы первого и третьего транзисторов 1 и 3 — с выходной шиной 19, дополнительный коллектор второго транзистора 2 и коллектор пятого транзистора связи 14 с базой пятого тРанзистора 5, дополнительный коллектор которого — с ба-зой третьего транзистора З,эмиттеры четвертого и пятого транзисторов связи 13 и 14 — с соответствующими

35 коллекторами опорного и блокировочного транзисторов 9 и 7, коллекторы второго и четвертого транзисторов связи 11 и 13 — с базами второго и четвертого транзисторов 2 и 4, дополнительные соответствующие коллекторы шестого транзистора 6 — с базами первого и третьего транзисторов 1 и 3, а его база — с входной шиной 17.4

Транзисторы 9, 11, 13, 12, 10 и 14 являются управляемыми источника ми взвешенных токов, величины которых для транзисторов 1-5 составляют соответственно 1,5, 0,5 2, 0,5 50 и 0,5 уровней тока д ..

Для получения стабильного коэффициента передачи транзисторов 1-5 в них введены коллекторы обратной связи. Соотношением площадей коллек- 55 торных областей транзисторов 1-5 обеспечиваются необходимые коэффициенты передач Вз по каждому выходному коллектору. Для коллекторов, об-, разующих триггерные связи,B ++=1,051,1, для коллекторов, соединенных с шиной 19, транзисторов 1 и 3 — 1 и 0,5 соответственно, для коллектора транзистора 5 -Sq --2, для коллекторов транзистора 6"В,, =0,5.

Работает ячейка памяти следующим образом.

Во время тактового импульса транзистор 7 открыт, шунтирует вход ячейки памяти и транзисторы 10-14, а транзистор 8 задает ток в транзисторы 1-4.

Это режим хранения. При отсутствии тактового импульса ячейка памяти в режиме записи.

Если во входной шине 17 нулевой уровень тока, транзистор 6 закрыт,. в транзисторы 1 и 3 задается ток 1,5 и 3О, т.е. больше, чем в транзисторы 2 и 4 (по 0,5). Триггеры устанавливаются в первое состояние, транзисторы 1 и 3 открыты.

При уровне входного тока о 3 с 23о транзистор 6 отводит через каждый коллектор ток, равный половине этого тока, в результате в базу транзистора 3 задается ток меньше, чем в базу транзистора 4, второй триггер переключается. Теперь транзистор 3 выключен, а транзистор 1 включен.

При уровне входного тока 23c)c3l ток, задаваемый в базу транзистора 1, меньше 0,5 3, что приводит к выключению последнего и включению транзистора 2, который отводит ток базы транзистора 5, последний выключается.

В реэульФате в базу транзистора 3 задается больший ток, равный разнице задаваемого транзистором 10 и отводи- мого транзистором 6. Величина этого тока больше 0,53 . Поэтому транзистор

3 включится. Таким образом, в этом состоянии транзистор 1 выключен, а транзистор 3 включен. При уровне входного тока больше 3 до транзистор

3 выключается.

С приходом тактового импульса транзистор 7 шунтирует входную шину

17 и транзисторы 10-14, а транзистор

8 своим током сохраняет состояние триггеров до прихода следующего тактового импульса. При этом, в зависимости от хранимой информации, с выходной шины 19 транзисторы 1 и 3 отводят О, 1, 2 или 3 уровня тока.

Использование коллекторов обратной связи позволяет существенно

11323

br= 6„- „ I нт

ВНИИПИ Заказ 9804/43

Тираж 861 Подписное

Фаяваа ППВ "Ватеий", е.Уил ород, ул.Нроектиаа, 4

3 стабилизировать коэффициенты передач

5э, транзисторов по выходным коллек торам (ЗХ) . Это значительно улучшает точностные характеристики триггеров. Гистерезис триггера определяется коэффициентами усиления В „ сои ставляющих его транзисторов.

Величина гистереэиса равна

n n где В> и 6 < — коэффициенты усиления

1 Я первого и второго транзисторов триг- 15 гера.

Для обычных триггеров величина гистерезиса представляет собой довольно большую величину (4-5) 3 к тому же еще и нестабильную, в связи с разбросом 8 . Введение коллекtl торов обратной связи позволяет уменьшить величину гистерезиса до (0,1—

0,2) 3д, что существенно улучшает работоспособность ячейки памяти.

Потребляемая ячейкой памяти мощ-. ность определяется количеством питающихся транзисторов в режиме хранения. Следовательно, уменьшая их количество, при том же токе, задаваемом в каждый транзистор, потребляемая мощность уменьшается.

Таким образом, увеличиваются точностные характеристики предложенной ячейки памяти и уменьшается потребляемая мощность в режиме хранения.