Устройство для формирования трапецеидальных импульсов

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТРАПЕЦЕИДАЛЬНЫХ ИМПУЛЬСОВ по авт. св. 620013, отличающеес я тем, что, с целью повышения стабильности работы устройства, в ,иего введены первый интегратор, источник управлямого тока заряда, первый элемент совпадения, второй элемент совпадения, второй и третий интеграторы , компаратор верхнего уровня и компаратор нижнего уровня, уп-. равляемые входы котррых подключены к выходу первого интегратора, вход которого соединен с выходом устройства , а выходы компараторов верхнего и нижнего уровня подключены к первым входам соответственно первого и второго элементов совпадения, вторые входы которых соединены с первой и второй шинами синхроимпульсов эталонной длительности, причем выход первого элемента совпадения подклю« чен ко входу второго интегратора, выход которого соединен с управляющим входом источника управляемого тока заряда, который включен между первой шиной питания и эмиттером транзистора первого ключа, коллектор которого соединен со входом первого интегратора, при этом выход второго элемента совпадения соединен с управлякицим входом третьего интегратора , который включен между первой шиной питания и входом делителя напряжения .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) фиг.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕ

Н ABTOPCKOMV СВИДЕТЕЛЬСТВУ (61) 620013 (21) 3467018/24-21 (22) 23.04.82

° ° ° ° °

46) 30..12.84. Бюл, 9 48

72) В.A.Àâäååâ и P.Â.Áoäíàð (53) 621.373 (088.8) (56) 1.Авторское свидетельство СССР

9 620013, кл. Н 03 К 4/94, 27.12 76. (54) (57) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

ТРАПЕЦЕИДАЛЬНЫХ ИМПУЛЬСОВ по авт. св. 9 620013, отличающее с я тем, что, с целью .повышения стабильности работы устройства, в ,него введены первый интегратор, источник управлямого тока заряда, первый элемент совпадения,: второй элемент совпадения, второй и третий интеграторы, компаратор верхнего уровня и компаратор нижнего уровня, уп-. равляемые входы которых подключены к выходу первого интегратора, вход которого соединен с выходом устройства, а выходы компараторов верхнего и нижнего уровня подключены к первым входам соответственно первого и второго элементов совпадения, вторые входы которых соединены с первой и второй шинами синхроимпульсов эталонной длительности, причем выход первого элемента совпадения подклю» чен ко входу второго интегратора, выход которого соединен с управляющим входом источника управляемого тока заряда, который включен между первой шиной питания и. эмиттером транзистора первого ключа, коллектор которого соединен со входом первого интегратора, при этом выход второго щ

C элемента совпадения соединен с управляющим входом третьего интегратора, который включен между первой шиной питания и входом делителя напряжения.

1132350

Изобретение относится к импульс,ной технике и может быть использовано, например, для формирования видеоимпульсов заданной формы.

Ila основному..авт. св. Р 620013, известно устройство для формирования трапецеидальных импульсов, содержащее два ключа на транзисторах с разным типом проводимости, эмиттер транзистора первого иэ которых подключен к первой шине питания, допол- 10 нительный транзистор, коллекторноэмиттерный переход которого подключен между .эмиттером второго транзистора второго ключа и второй шиной питания, а база подключена к движку по- 15 тенциометра, включенного между первой:и второй шйнами питания,-при этом коллекторы транзисторов обоих ключей объединены и являются выходом устройства (1).. 20

Недостатком устройства является его низкая стабильность, так как оно не позволяет формировать импульсы трапецеидальной формы с высокой стабильностью амплитуды, фронта, спада 25 в области малых времен, в широком диапазоне изменения климатических условий.

Бель изобретения — повышение стабильности работы устройства. 30

Поставленная цель достигается тем, что в устройство для формирова ния трапецеидальных импульсов введены первый интегратор, источник уп.— равляемого тока заряда, первый элемент совпадения, второй элемент совпадения, второй и третий интеграторы, компаратор верхнего уровня и компаратор нижнего уровня, управляемые входы которь;х подключены к выходу первого интегратора, вход которого соединен с выходом устройства,а выходы компараторов верхнего и нижнего уровня подключены к первым входам соответственно первого и второго элементов совпадения, вторые входы которых соеди- 45 нены с первой и второй шинами синхроимпульсов эталонной длительности, причем выход первого элемента совпадения подключен ко входу второго интегратора, выход которого соединен 50 с управляющим входом источника уп- ° равляемого тока заряда, который вклю. чен.между первой шиной литания и эмиттером транзистора первого ключа, коллектор которого соединен со вхо- у дом первого интегратора, при этом выход второго элемента совпадения соединен с управляющим входом третьего интегратора, который включен между первой шиной питания и входом 60 делителя напряжения.

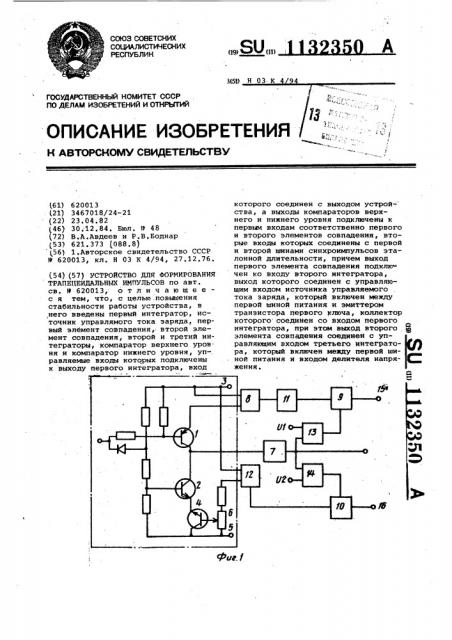

На фиг.1 приведена структурная электрическая схема устройства», на фиг.2 — эпюры, поясняющие работу устройства. - 6S устройство содержит два ключа на транзисторах 1 и 2 с разным типом проводимости, эмиттер транзистора 1 первого из которых подключен к первой шине 3 питания, дополнительный транзистор. 4„ коллекторно-эмиттерный переход которого подключен между эмиттером второго транзистора 2 второго ключа и второй шиной 5 питания, а база подключена к. движку потенциометра 6, включенного между первой и второй шинами 3 и 5 питания, при этом коллекторы транзисторов 1 и 2 обоих ключей объединены и являются выходом устройства, первый интегратор 7, источник 8 управляемого тока заряда,.первый элемент 9 совпадения, второй элемент 10 совпадения, второй интегратор 11, третий интегратор 12, компаратор 13 верхнего уровня и компаратор 14 нижнего уровня, управляемые входы которых подключены к выходу первого интегратора 7, своим входом соединенным с выходом устройства, а выходы компараторов 13 и 14 верхнего и нижнего уровней подключены к первым входам соответственно первого и второго элементов совпадения, вторые входы которых соединены с первой и второй шинами 15 и 16 синхроимпульсов эталонной длительности, причем выход первого элемента совпадения подключен ко входу второго интегратора 11,,выход которого соединен с управляющим входом источника 8 управляемого тока заряда, который включен между первой шиной 3 питания и эмнттером транзистора 1 первого ключа, коллектор которого соединен со входом первого интегратора, при этом выход второго элемента .10 совпадения соединен с управляннцим входом третьего интегратора 12, который включен между первой шиной 3 питания и входом делителя напряжения.

Устройство работает следующим образом.

К входу устройства подводится последовательность прямоугольных импульсов "gx(t) {фиг,2ц) с периодом повторения Г ..лфи отрицательном перепаде входного импульса диод и тран; зистор 1 открыты, а транзистор 2 заперт. Ток от источника 8 управляе. мого тока заряда через транзистор 1 поступает на вход интегратора 7 и заряжает времязадающий конденсатор.

На выходе интегратора 7 формируется фронт трапецеидального импульса (фиг,2lj При положительном перепаде,входного импульса диод и транзистор 1 заперты, а транзистор 2 открыт. Происходит разряд времязадаю. щего конденсатора интегратора 7 через транзисторы 2 и 4. На выходе уст. ройства формируется спад трапецеи1132350 дального импульса (*иг.22), длительность которого зависит от величины смещения подводимого к транзистору 4 с потенциометра 6, так как величина сопротивления транзистора 4, а вместе с ним постоянная времени времязадающей цепи разряда зависят от величины напряжения смещения, подводимого к базе транзистора 4. Применение интегратора 7 в устройстве обеспечивает высокую линейность фронта и спа- 10 да трапецеидальных импульсов на выходе устройства в широком диапазоне скоростей нарастания и спада выходного напряжения. Скорость нарастания выходного напряжения линейно зависит 15 от величины зарядного тока. При достижении линейно нарастающим напряжением фронта трапецеидального импульса величины опорного напряжения компа -атора 13, последний вырабатывает импульс конца формирования линейно нарастающего напряжения фиг.24), который подается на первый вход элемента 9 совпадения, на вто рой вход которого с шины 15 подаются импульсы эталонной длительности.

Элемент совпадения на выходе Формирует импульсы рассогласования фиг,2e}. Длительность импульсов рассогласования обратно пропорциональна разности времени прихода на вход эле мента совпадения импульсов эталонной длительности и конца формирования линейно нарастающего напряжения. Импульсы рассогласования, проинтегрированные и усиленные интегратором 11, управляют источником тока заряда 8.

Управление производится так, что при увеличении длительности импульсов на выходе элемента 9 совпадения напряжение на выходе интегратора 11 увеличивается, а ток на выходе источника заряда уменьшается,идлительность линейно нарастающего напряженияна выходе интегратора уменьшается.

При уменьшении .длительности импульсов (фиг.25) напряжение на выходе интегратора 11 уменьшается, а ток на выходе источника тока заряда увеличивается. Этот процесс продолжается до тех пор, пока не установится на выходе элемента совпадения длительность импульсов, равная оптималь ной, и таким образом сформируется требуемая длительность и скорость нарастания выходного пилообразного напряжения ° Аналогично работает цепь формирования спада выходного напряжения (фиг.3а, 6,2, Яс и y )

Таким образом, на выходе устройства, блоки которого построены на относительно нестабильных элементах, формируются импульсы с высокой стабильностью по длительности фронта и спада амплитуды. Устройство, решая ту же техническую задачу, что и устройство-прототип, обходится беэ высокостабильных элементов, и в то же время по точностным характеристикам генерируемых импульсов значительно превосходит устройство-прототип.

1132350 и

Составитель А.Горбачев

Техред С. Легеза Корректор А.Обручар

Редактор Т.Кблб

Филиал ПЦП "Патент", r. Ужгород, ул. Проектная, 4

° Заказ 9805/44 Тираж 861 Подписное

ВНИКНИ Государственного комитета СССР ио делам изобретениЯ и открытий

113035, Москва, _#_-35, Раушская наб., д. 4/5