Преобразователь кода системы остаточных классов в двоичный код

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ Б ДВОИЧНЫЙ КОД, содержащий группу сумматоров по модулю , накапливающий сумматор, группу триггеров, первую группу элементов И и элемент ИЛИ, причем выходы триггеров группы соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых соединены с тактовым ВХОДОМ преобразователя , ВЫХОДЫ элементов И, кроме первого , первой группы подключены к соответствующим входам элемента ИЛИ, ВЫХОД которого соединен с тактовым ВХОДОМ накапливающего сумматора, выход которого является ВЫХОДОМ преобразователя , единичный ВХОД первого, триггера группы соединен с входом Пуск преобразователя, нулевой вход k-ro триггера группы соединен с единичным ВХОДОМ (k+l)ro триггера группы (k . . . (п-1 ), где П - число оснований , отличающийся, тем, что, с целью сокращения количества оборудования, он содержит шифратор, группу элементов ИЛИ, элемент задержки и вторую группу элементов И, причем ВХОД остатка по наименьшему основанию преобразователя соединен с первыми входами элементов И.второй группы, ВЫХОДЫ которых соединены с первой группой входов шифратора, вторая группа входов которого соединена с выходами триггеров с второй по И-и группы, ВЫХОДЫ шифратора g соединены соответственно с информационными входами накапливающего cyvr (Л матора и сумматоров группы, выходы сумматоров группы соединены с входами соответствующих элементов ИЛИ группы, инверсные выходы которых подключены соответственно к.нулевым входам триггеров с второй по И-и группы, ВЫХОД первого триггера группы соединен с вторыми входами элеменСАд тов И второй группы, ВЫХОД первого :с элемента И первой группы через эле9 ) 35 мент задержки соединен с нулевым входом первого триггера группы и П-м CD ВХОДОМ элемента ИЛИ, выход которого соединен с тактовыми входами сумматоров группы.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (11) 4(51) Н 03 М 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНОЬЮ СВИДЕТЕЛЬСТВУ

Qlh,-;ь, ) ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ. (21) 3650791/24 — 24 (22) !0.10.83 . (46) 07.01.85. Бюл. ¹ (72) С.Н.Хлевной, Н.И.Червяков, Н.И.Швецов и А.П.Болтков (53) 681.3(088.8) (56) 1. Авторское свидетельство СССР

¹ 9914)0, кл. G 06 F 5/02, 1981.

2. Авторское свидетельство СССР по заявке №- 3518613/18-24, 1982 (прототип). (54)(57) ПРЕОБРАЗОВАТЕЛЬ КОДА СИСТЕNbI ОСТАТОЧНЫХ КЛАССОВ В ДВОИЧНЫЙ КОД, содержащий группу сумматоров по модулю, накапливающий сумматор, группу триггеров, первую группу элементов

П и элемент ИЛИ, причем выходы триггеров группы соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых соединены с тактовым входом преобразователя, выходы элементов И, кроме первого, первой группы подключены к соответствующим входам элемента ИЛИ, выход которого соединен с тактовым входом накапливающего сумматора, выход которого является выходом преобразователя, единичный вход первого, триггера группы соединен с входом

"Пуск" преобразователя, нулевой вход

k-го триггера группы соединен с единичным входом (k, +1)-го триггера груп. пы (1(l... (и-l ), где и — число оснований, отличающийся, тем, что, с целью сокращения количества оборудования, он содержит шифратор, группу элементов ИЛИ, элемент задержки и вторую группу элементов И, причем вход остатка по наименьшему основанию преобразователя соединен с первыми входами элементов И второй группы, выходы которых соединены с первой группой входов шифратора, вторая группа входов которого соединена с выходами триггеров с второй по Н -й группы, выходы шифратора соединены соответственно с информационными входами накапливающего сум-. матора и сумматоров группы, выходы сумматоров группы соединены с входами соответствующих элементов ИЛИ

:группы, инверсные выходы которых под» д ключены соответственно к нулевым входам триггеров с второй по ))-й группы, выход первого триггера группы соединен с вторыми входами элементов И второй группы, выход первого элемента И первой группы через элемент задержки соединен с нулевым входом первого триггера группы и И-м . входом элемента ИЛИ, выход которого соединен с тактовыми входами сумматоров группы.

1133669

Изобретение относится к вычисли1 тельной технике и может быть использовано для сопряжения с вычислительными устройствамИ, функционирующими в СОК, а также в аппаратуре передачи данных, использующей коды СОК.

Известно устройство для преобразования чисел из СОК в позиционный код, содержащее суммирующие счетчики, входные регистры, элементы сравнения 10 по основаниям СОК, двоичный накапливающий счетчик, выходы которого являются выходом устройства, первый триггер, первый и второй элемент И (1)

Однако данное устройство требу- 15 ет значительных аппаратурных затрат и обладает недостаточным быстродействием, что снижает эффективность вычислительных устройств, функционирующих в СОК.

Наиболее близким к изобретению щ по сущности технического решения является преобразователь непозиционного кода в двоичный код, содержащий груп;, пу входных регистров, группу элемен"тов сравнения, группу элементов И, 2 группу счетчиков по модулю, накапливающий сумматор, коммутатор, элемент

ИЛИ, группу триггеров, причем входы счетчиков по модулю группы соединены соответственно с выходами элементов

И, первые входы которых соединены с тактовым входом преобразователя, информационные входы которого соединены с входами регистров группы, выходы которых соединены с первыми входами соответствующих элементов сравнения группы, вторые входы которых соединены с выходами соответствующих счетчиков по модулю группы, выходы накапливающего сумматора являются выходами преобразователя

40 входы констант эквивалентов которого соединены с информационными входами коммутатора, выходы которого соединены с информационными входами накапливающего сумматора, управляющий 45 .вход которого соединен с выходом элемента ИЛИ, входы которого соединены с выходами элементов И группы, вторые входы которых соединены с выходами соответствующих триггеров группы и с управляющими входами коммутатора, выход k -го элемента сравнения группы (k=1"; h, где И число оснований) соединен с нулевым входом -ro и единичным входом (М+1)-ro Я триггера группы, единичный вход пер вого триггера группы является входом пуска преобразователя )2);

Недостатком известного устройства являются значительные аппаратурные затраты.

Цель изобретения — сокращение ко--личества оборудования.

Поставленная цель достигается тем, что преобразователь кода системы остаточных классов в двоичный код, содержащий группу сумматоров по модулю, накапливающий сумматор, группу триггеров, первую группу элементов И и элемент ИЛИ, причем выходы триггеров группы соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых соединены с тактовым входом преобразователя, выходы элеменI тов И, кроме первого, первой группы подключены к соответствующим входам элемента ИЛИ, выход которого соединен с тактовым входом накапливающего сумматора, выход которого является выходом преобразователя, единичный вход первого триггера группы соединен с входом "Пуск" преобразователя, нулевой вход k -го триггера группы соединен с единичным входом (k+1)-го триггера группы (k =l-,(и-l), где П вЂ” число оснований, содержит шифратор, группу элементов ИЛИ, элемент задержки и вторую группу элементов И, причем вход остатка по наименьшему основанию преобразователя соединен с первыми входами элементов

И второй группы, выходы которых соединены с первой группой входов шифратора, вторая группа входов котороI го соединена с выходами триггеров с второй по 0-й йгруппы, выходы шифратора соединены соответственно с информационными входами накапливающего сумматора и сумматоров группы, выходы сумматоров группы соединены с входами соответствующих элементов

ИЛИ группы, инверсные выходы которых подключены к нулевым входам триггеров с второй по П -й группы выход первого триггера группы соединен с вторыми входами элементов И второй группы, выход первого элемента И первой группы через элемент задержки соединен с нулевым входом первого

I триггера группы и 11-м входом элемента ИЛИ, выход которого соединен с тактовыми входами сумматоров группы.

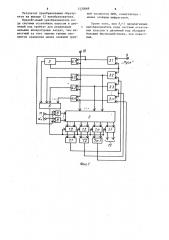

На фиг.! представлен преобразователь кода системы остаточных классов в двоичный код; на фиг.2 — приствуют нулевые потенциалы, то тактовые импульсы на выход элементов И

4.1-4.!! не поступают. о

При поступлении на вход триггера 3.1 импульса "Пуск", он устанавливается в единичное состояние, тактовый импульс поступает на вход элемента 5 задержки через элемент И

4.1. Одновременно открывают элементы И 8 группы и код остатка К1 поступает через шифратор 2 на входы всех сумматоров 1.1-1. h без изменения.

Тактовый импульс появляется на первом выходе элемента 5 задержки и через элемент ИЛИ 6 поступает на тактовый вход всех сумматоров 1.1 — 1.!1. При этом -из содержимого сумматоров 1.2-1. вычитается значение a, а в сумматоре 1.1 оно прибавляется к нулевому значению.

После выполнения операций суммирования и вычитания импульс со второго выхода элемента 5 задержки устанавливает триггер 3.1 в исходное состояние, а 3 ° 2 — в единичное состояние. Прн этом вход II отключается от шифратора 2 и в последующем информация, подаваемая по нему для работы устройства, значения не имеет.

Под действием единичного потенциала на выходе триггера 3.2, на выхо дах шифратора 2 формируется код числа Р1, которое при поступлении тактовых импульсов через элемент

И 4.2 и элемент ИЛИ 6 на тактовые входы сумматоров I.I-I.II подсуммируется к содержимому .сумматора 1.1 и вычитается из сумматоров 1 ° 2-1.II.

Когда сумматор 1.;2 обнулится, на инверсном выходе элемента ИЛИ 7.1 появится единичное значение, которое установит триггер 3.2 в исходное, а триггер 3.3 — в единичное состояние. При этом на выходах шифратора 2, соответствующих сумматору 2.2, появится код нуля. На выходах, соответствующих сумматорам 1.3 — 1. И вЂ” значение /Р1 Р /Р„, где k = 3 — II, соответственно. На выходах, соответствующих сумматору I 1 — значение

1 2

Описанным образом преобразователь будет работать до тех пор, пока при обнулении сумматора 1. И на инверсном выходе элемента ИЛИ 7л-1 не появляется сигнал единицы, которы обнуляет триггер З.п . На этом процесс преобразования заканчивается.

А = (К„М, . ° .Ып), где Ж вЂ” остаток от числа .по модулю

Р1 .

Преобразуя по модулям Р„, получим

/А/Р -ж, а1

/А/р = + 2 =/а а+ 0 2 Д / р2

Ф и-, ао

/A/Ð 0 2 /a,,+O2P +...1a„g Р /

Из чего следует, что перевод числа А можно выполнить последовательно, начиная с а1 прибавлением последую- 45 щих членов указанного уравнения до выполнения равенства о(„ ад..

Преобразователь кода системы остаточных классон в двоичный код работает следующим образом. 50

В исходном состоянии сумматор I ° 1 очищен. В модульные сумматоры ° 2-1.п занесены значения остатков М2 - OLn соответственно. Триггеры 3.1-3. П установлены в нулевые состояния. По входу 10 тактовых импульсов поступают тактовые импульсы, на так как на выходах триггеров 3.1-3.h присут3 1133669 мер реализации шифратора для случая

Р! =5, Р =7, Pg=l! .

Преобразователь кода системы остаточных классов в двоичный код содержит накапливающий сумматор l,l„ сумматоры по модулю 1,2-1,11 группы,-шифратор 2, группу триггеров

3.1-3.п, группу элементов И 4.1-4.II, элемент 5 задержки, элемент ИЛИ 6, группу элементов ИЛИ 7.1-7..п-l, груп- !О пу 8 элементов И, вход 9 "Пуск" преобразователя, вход 10 тактовых импульсов, вход 11 остатка по наименьшему основанию, выход 12 преобразователя.

Шифратор 2 содержит элементы

ИЛИ 13.

Сумматор 11 является двоичным, на- капливающим. Сумматоры 1,2-). и группы являются мрдульными вычитающими.

Любое число А натурального ряда может быть выражено в обобщенной позиционной системе (ОПС ) как

11-1

А-с1;iо р,t- a <

I(=1 где а11 - коэффициенть1 ОПС;

P1, - основания ОПС.

В то же время число А в СОК с основаниями, аналогичными ОПС, записывается в виде 30

Результат преобразования образуется на выходе 12 преобразователя.

Предлагаемый преобразователь кода системы остаточных классов в двоичный код требует для реализации меньших аппаратурных затрат, чем известный за счет замены группы элементов сравнения менее сложной груп1133669 6 пой элементов ИЛИ, коммутатора— менее сложным шифратором.

Кроме того, при Р,) 2 предлагаемыи преобразователь кода системы остаточных классов в двоичный код обладает большим быстродействием, чем известный.

1133669

Составитель А.Клюев

Редактор Н.Данкулич Техред С.Легеза Корректор A.ÇHìîêoño

Заказ 9960/44 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная,4