Сумматор по модулю

Иллюстрации

Показать всеРеферат

СУММАТОР ПО МОДУЛЮ, содержаияй группу элементов И, блок сумг мирования, первый узел формирования обратного кода, причем информационный вход первого узла форм1{рования обратного кода является входом первого операнда сумматора, выход первого узла формирования обратного кода соединен с входом первого операнда блока суммирования, вход второго операнда которого является входом второго операнда сумматора, уяравлякятий йход первого узла формнрования обратного кода является вхопхж кода операции сумматора, о т л я ч а ю щ и и с я тем, чЮ, с .целью повышения достоверности суммирования , в него введены триггер, элемент И, формирователь импульсов и второй узел формирования обратного кода, . причем выкод блока суммирования соединен с информа11 онным входом второго узла формирования обратного кода, выход которого является выходом сумматора, первые входы элементов И группы являются входа а1 кода модуля С5 шатора; вькоды элементов И группы соединены с входом третьего Операнда блока cy o«иpoвaния, выход переполнения которого соединен с первым вход1ом элемента И, выход Которого соединен с .нулевым входом тригW гера, прямой вькод которого соединен с с вторыми входа)0{ элементов И группы, единичный вход триггера и вход фор вфовятеля импульсов объединены и являются вх(щом запуска сумматора, KJiKofl Формирователя импульсов соединен с вторым входом элемента И, управляющий вход второго узла формиро&д 4 Ф 00 вания обратного кода объединен с входом кода опера1щи сумматора. ;о

СОЮЗ COBETCHHX

NMW

РЕСПУБЛИК

QQ (И) ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬС ГВУ (21) 3519549/24-24 (22) 07. 12.82 (46) 15.01.85. Внл. Р 2 (72) С.Н.Хлевной, Н.И.Червяков, Н.И.Швецов и В.А.Цупко (53) 681.3(088.8) (56) 1. Авторское свидетельство ССОР

У 378845, кл. Г 06 F .7/50, .1973.

2. Авторское свидетельство СССР

Р 332460, кл, Г, 06 F 7/50, 1972 (прототип). (54)(57) СУММАТОР ПО МОДУЛЯ, содер-, жащий группу элементов И, блок сум-мирования, первый узел формирования обратного кода, причем информационный вход первого узла формирования обратного кода является входом первого операнда сумиатора, выход первого узла формирования обратного кода соединен с входом первого операнда блока суммирования, вход второго операнда которого. является входом . второго .операнда сумматора, уиравлякщий.йход первого узла формирова-— ния обратного кода является входом кода операции сумматора, о т .л я »

4(51) С; 06 F 11/00 С 06 F 7/50 ч а ю шийся тем, что, с целью повышения достоверности суммирования, в него введены триггер, элемент

И, формирователь импульсов и второй узел формирования обратного кода, причем вьвсод блока суммирования соединен с информационным входом второго узла формирования обратного кода, выход которого является выходом сумматора, первые входы элементов И группы являются входами кода модуля суьвитора, выходы элементов И группы соединены с входом третьего операнда блока сую ирования, выход переполнения которого соединен с

O первым входом элемента И, выход кото- Е рого соединен с .нулевым входом триггера, прямой выход которого соединен ЮФ е вторыми входами элементов И группы, единичный вход. триггера и вход фор ииронетеля импульсов объединены и Я являются входом зануска сумматора, выход формирователя импульсов соединен с вторым входом элемента И, управляюций вход второго узла формирования обратного кода объединен с входом кода операции сумматора.

1134939 2

Наиболее близким по технической сущности к изобретению является устройство, содержащее управляемые. инверторы, позиционный .и непозицион- ньй сумматоры, первые и вторые блоки ключей, инвертор, схему ИЛИ, выходы управляемых инверторов подключены к первым входам позиционного сумматора, первый и второй выходы которого подключены к соответствующим sxoдам непозиционного сумматора, выходы которого подключены к вторым входам первых блоков ключей, первые входы которых соединены с управляющим выходом позиционного- сумматора и входом инвертора, выход которого подключен к первым входам вторых блоков ключей, вторые входы которых соединены со вторыми выходами позиционного сумматора и входом инвертора, выход которого подключен к первым входам вторых блоков ключей, вторые входы которых соединены с вторыми выходами позиционного сумматора и входом инвертора, выход которого подключен к первым входам вторых блоков ключей, вторые входы которых

50

Изобретение относится к вычислительной технике и может быть использовано при построении однородных вычислительных систем, Аункционирующих .а системе остаточных классов (СОК), а также при проектировании типовых элементов замены, работающих по произвольному модулю, в системах контроля передачи дискретной инАормации.

Известно ариАметическое устройство в системе остаточных классов, содержащее приемные регистры, дешиАраторы, схему преобразования в дополнительный код, матрицу запоминания результатов операций, схему выдачи результатов, в которых выходы первого приемного регистра через первый дешифратор, а выходы второго приемного регистра через второй дешиАратор и схему преобразования в дополнительный код подключены к со-! ответствующим входам матрицы запоминания результатов; выходы которой. подключены к входам схемы, выдачи результатов f1) .

Однако дайное устройство обладает низким быстродействием выполнения операции вычитания, большими аппаратурными затратамн и не допускает работу по произвольному модулю.

25 соединены с вторыми выходами позиционного сумматора, а выходы к второму входу элемента ИЛИ, первый вход которого соединен с выходами первых блоков ключей P2).

Однако это устройство характери- зуется большими аппаратурными затратами, результаты суммирования и вычитания выдает в обратном и прямом кодах соответствейно, результат суммирования достоверен в ограниченном ( диапазоне изменения входных величин.

Целью изобретения является повышение достоверности суммирования.

Поставленная цель достигается тем, что в сумматор по модулю, содержащий группу элементов И, блок суммирования, первый узел Аормирования обратного кода, причем информационый вход первого узла Аормирования обратного кода является входом первого операнда сумматора, выход первого узла формирования обратного кода соединен с входом первого операнда блока суммирования, вход второго операнда которого является входом второго операнда сумматора, управляющий вход первого узла Аормирования кода является входом кода операции сумматора, введены триггер, элемент И, Аормирователь импульсов и второй узел формирования обратного кода, причем выход блока суммирования соединен с информационным входом второго узла формирования обратного кода, выход которого является выходом сумматора, первые входы элементов И группы являются входами кода модуля сумматора, выходы элементов И группы соединены с входом третьего операнда блока суммирования, выход переполнения которого соединен с первым входом элемента И, выход которого соединен с нулевым входом триггера, прямой выход которого соединен с вторыми входами элементов И группы, единичный вход триггера и вход Аормирователя импульсов объединены и являются входом запуска сумматора, выход формирователя импульсов соединен с вторым входом элемента И, управляющий вход второго узла формирования обратного кода объединен с входом кода операции сумматора.

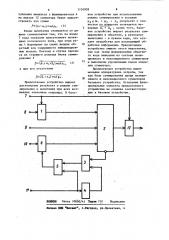

На чертеже приведена структурная схема предлагаемого сумматора по модулю.

Сумматор по модулю содержит первый и второй узлы 1 Аормирования об

3 11349 ратного кода, блок 2 суммирования, элемент И 3, формирователь 4 импульсов, триггер 5, группу 6 элементов

И, вход 7 кода операции, входы 8 и 9 первого и второго операндов сум5 матора, входы 10 кода модуля сумматора, вход 11 запуска сумматора, выход 12 сумматора.

Управляющие входы узлов 1 формирования обратного кода объединены с входом 7 кода операции сумматора.

Дпя случая двоичного кодирования операндов узлы 1 представляют собой управляемые поразрядные инверторы. .При унитарном кодировании операндов узлы 1 содержат схему перестановки и коммутатор, причем информационный вход узла формирования обратного кода соединен с первым входом коммутатора и входом схемы перестановки, выход последней соединен с вторым входом коммутатора, выход н управляющий вход которого являются выходом и управлявшим входом узла формирования обратного кода. Информационный вход первого узла формирования обратного кода является входом. первого операнда сумматора, а выход соединен с входом первого операнда блока 2 суммирования. Блок 2 суммирования выполнен трехвходовым и может быть реализован, например, на двухвходовых сумматорах, выход переполнения его выполнен инверсным.

Вход второго операнда блока суммирования является входом 9 второго М операнда сумматора. Вход третьего операнда блока суммирования подключен к выходу группы 6 элементов И, первые. входы которых являются входом

10 кода модуля сумматора, а вторые входы объединены и подключены к прямому выходу триггера 5, единичный вход которого объединен со входом формирователя импульсов 4 и являются входом 11 запуска сумматора. Формирователь импульсов 4 может быть выполнен в виде триггера с одним устойчивым состоянием и фиксированным временем нахождения в нем, причем при переходе в исходное состоя- ЗО ние на его выходе появляется импульс.

Выход формирователя 4 импульсов соединен с вторым входом элемента И 3, выход которого соединен с нулевым входом триггера 5, а первый вход — 55 с выходом переполнения блока 2 суммирования. Выход блока суммирования соединен с информационным входом

39 4 второго узла формирования обратного кода, выход которого является выходом 12 сумматора.

Предлагаемое устройство работает. следуюшим образом.

Режим суммирования. Обозначим модуль, по которому работает блок суммирования, через ря, а модуль, по которому будет выполняться сложение, МЪ через у„, тогда модуль сумматора р код которого будет подан на.входы

10 устройства, определяется по формуле р = р„ — р . В исходном состоянии на входе 7 кода операции присутствует потенциал логической "1", при этом узлы формирования обратного кода не изменяют на своем выходе содержимого своих информационных кодов. На выходах 8-10 выставлены коды операндов,, ay и модуля сумматора р . Состояние триггера 5 безразлично. формирователь 4 импульсов — в исходном состоянии.

При подаче импульса на вход 11 запуска сумматора формирователь 4 .импульсов переводится в рабочее состояние, триггер 5 устанавливается в единичное состояние и потенциал логической единицы с его прямого выхода, поступая на вторые входы группы б элементов И, разрешает прохож-, дение кода модуля сумматора с входа

10 на вход третьего операнда блока суммирования, на выходе которого присутствует код суммы

P=-4« г Р.) adÐ

При наличии переноса из старшего разряда блока суммирования на его выходе переполнения присутствует потенциал логического "0", который запретит прохождение импульса с выхода формирователя импульсов 4 (по возврацении его в исходное состояние) через элемент И 3 на нулевой вход триггера 5. На выходе 12 сумма-. тора до прихода очередного импульса запуска будет присутствовать код результата согласно (1). Если на выходе переполнения блока суммирования будет присутствовать потенциал логической "1", то импульс с форми- рователя 4 пройдет через элемент

И 3 и переведет триггер 5 в нулевое состояние, что приведет к снятию ко" да модуля сумматора с входа третьего операнда блока 2 суммирования.

Спустя время переходных процессов в блоках 3, 5, 6, 2 и 1 после пос1134939 а при его отсутствии

ВИИИПИ Заказ 1009Î/41 Tsyaa 710 - Подписное

Филиал ППВ "йатамт", r.Óèòîðîä, ул.Проектная, 4 тупления импульса с формирователя 4 на выходе 12 сумматора будет присутствовать код суммы

1=(М 4 М21 тод рп. (2)

Режим вычитания отличается от ре-. жима суммирования тем, что на входе

7 кода операции присутствует потенциал логического нуля, при этом узлы 1 формируют на своих входах об- 10 ратный код содержимого индюрмационных входов. Поэтому в случае перено са иэ старшего разряда блока сумми-. рования 2

15 = " +с Рс1вод Р„, (33

p = (a ä ю д Р °

Предлагаемое устройство выдает достоверные результат в режиме суммирования и вычитания при всех воэ- можных значениях операнда. В базоУ вом устройстве при использовании режима суммирования и условии

Сао +Юг с р ре настям По инверсии попучеется неверным М + нт, кроме того, бввовое устройство выдает результат суммирования в обратном, а результат вычитания — в прямом коде, что соз- . дает неудобства для последующей обработки информации. Предлагаемое устройство лишено этого недостатка, так как <хемы формирования обратного кода выведены из состава позиционного и непозиционного сумматоров и выполнены управляемым кодом операции сумматора.

Предлагаемое устройство имеет меньшие аппаратурные затраты, так как блок суммирования проще позиционного и непозиционного сумматоров базового устройства. Остальные функциональные.элемента предлагаемого устройства не сложнее соответствующих в базовом устройстве.