Запоминающее устройство

Иллюстрации

Показать всеРеферат

ЗАПОМИНАК |ЕЕ УСТРОЙСТВО, содержащее накопитель, вьтолненный на линии задержки, выход которой соединен с входом корректирующего усилителя, и блок управления, о т л и чающееся тем, что, с целью повышения точности устройства, в него введены сумматоры, коммутатор, ключ и масштабирующий усилитель, выход которого является первым выходом устройства, первый вход масштабирующего усилителя соединен с выходом корректирующего усилителя и с первым входом первого сумматора, выход которого является вторым выходом устройства, второй вход первого сумматора соединен с выходом ключа, первый-вход которого соединен с первым выходом блока управления , второй вход ключа является первым входом устройства и соединен с первым входом второго сумматора, выход которого соединен с первым входом коммутатора, второй и третий входы которого соединены с вторым 9 и третьим выходами блока управления, первыйи второй выходы коммутатора соединены соответственно с входом блока управления и с входом линии задержки, второй вход второго сумматора является вторым входом устройства , четвертый выход блока управления соединен с вторым входом масштабирующего усилителя. СО 4 СО Ф

аю (в

СОЮЗ СОВЕТСКИХ

СШОФВВП и

РЕСПУБЛИК

4(51) G 11 С 21/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ГОС ДАРСТ ЕКК Й HOMmer CCCe

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

Н ABTOPCNOMV СВИДЕТЮЪСТВУ (21) 3480515/24-24 (22) 11.08.82 (46) 15.01.85. Бюл. Р 2 (72) И.P.Áèëüïñ, В.А.Бурик, Б.С.Гук и И.Г.Загородний (7 1) Львовский филиал Киевского проектно-конструкторского бюро автоматизированных систем управления (53) 681.327.66(088.8) (56) 1. Гутников В.С. Интегральная электроника в измерительных устройствах. Л., "Энергия", 1980, с.208212.

2. Патент СНА И 4140927, кл. Н 03 К 3/353, опублик. 1981 (прототип). (54)(57) ЗАПОМИНАЮЩЕЕ УСТРОИСТВО, содержащее накопитель, выполненный на линии задержки, выход которой соединен с входом корректирующего усилителя, и блок управления, о т— л и ч а ю щ е е с я тем, что, с целью повышения точности устройства, в него введены сумматоры, коммутатор, ключ и масштабирующий усилитель, выход которого является первым выходом устройства, первый вход масштабирующего усилителя соединен с выходом корректирующего усилителя и с первым входом первого сумматора, выход которого является вторым выходом устройства, второй вход первого сумматора соединен с выходом ключа, первый. вход которого соединен с первым выходом блока управления, второй вход ключа является первым входом устройства и соединен с первым входом второго сумматора, выход которого соединен с первым входом коммутатора, второй и третий входы которого соединены с вторым Я и третьим выходами блока управления, первый и второй выходы коммутатора соединены соответственно с входом блока управления и с входом линии задержки, второй вход второго сумма- Я тора является вторь1м входом устройства, четвертый выход блока управления соединен с вторым входом масштабирующего усилителя.

1134967

Изобретение относится к вычислительной технике, в частности к за-поминающим устройствам, и может быть использовано в устройствах динамического запоминания импульсных сигналов.

Известно запоминающее устройство, выполненное на основе регистра сдвига и используемое в качестве распределителя импульсов Я .

Основным недостатком распределителей, построенных на базе триггеров, является требование постоянства формы импульсов (причем форма импульсов должна быть близка к прямоугольной} .

Известно также запоминающее устройство, содержащее накопитель на линиях задержки, соединенное с усилителем-инвертором без обратной свя-зи (2) .

Однако данное устройство обладает низкой точностью,. требует записи

25 сигнала в начале каждого цикла и не позволяет проводить операции перезаписи сигналов.

Цель изобретения -- повышение точности устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее накопитель, выполненный на линии задержки, выход которой соединен с входом корректирующего усилителя, и блок управления, введе- 35 ны сумматоры, коммутатор, ключ и масштабирующий усилитель„ выход которого является первым выходом устройства, первый вход масштабирующего усилителя соединен с выходом коррек- 40 тирующего усилителя и с первым входом первого сумматора, выход которого является вторым выходом устройства, второй вход первого сумматора соединен с выходом ключа, первый вход ко- <5 торого соединен с первым выходом блока управления, второй вход ключа является первым входом устройства и соединен с первым входом второго сумматора, выход которого соединен с 50 первым входом коммутатора, второй и третий входы которого соединены с вторым v. третьим выходами блока управления, псрвый и второй выходы коммутатора соединены соответствен- 55 но с входом блока управления и с входом линии задержки, второй вход второго сумматора является вторым входом устройства, четвертый выход блока управления соединен с вторым входом масштабирующего усилителя.

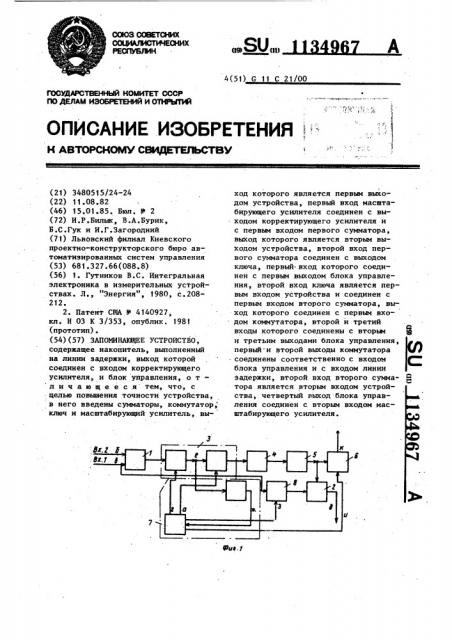

На фиг. 1 изображена функциональная схема предлагаемого устройства, на фиг.2 — функциональная схема блока управления.

Устройство (фиг.1) содержит сумматоры 1 и 2, коммутатор 3, накопитель на линии 4 задержки, корректирующий усилитель 5, масштабирующий усилитель 6, блок 7 управления и ключ 8.

Блок 7 управления (фиг.2) содержит формирователь 9 импульсов„ формирователь 10 временных интервалов, узел связи, элемент 12 управления выбором масштабного коэффициента, элемент 13 управления ключом 8, узел

14 управления режимом коммутатора 3.

Устройство работает в четырех режимах: записи, хранения (регенерации), сброса и исключения.

В режиме записи на Вх 2 устройства подается записываемый аналоговый сигнал произвольной формы, который проходит последовательно по цепям с максимальной задержкой, т.е. соответственно через блоки и элементы 1, 3, 4, 5 и 6.

В режиме сброса перед поступлением на один из входов (Вх 1 или

Вх 2) коммутатор 3 соединяет сигнальные цепи на один общий выход (не показан) устройства на время прохождения сигнала, в результате чего записанный аналоговый сигнал стирается.

В режиме регенерации (хранения) запоминающее устройство работает так же, как и в режиме записи, с той лишь разницей, что аналоговый сигнал подается на вход Вх 1 сумматора

1 данного устройства.

В режиме исключения сигнал проходит последовательно через блоки 3 и 2, т.е. по цепям с минимальным временем задержки, в результате чего основные блоки устройства "исключаются", в работе не участвуют.

В предлагаемом устройстве блок 7 управления формирует управляющие сигналы, обеспечивающие работу запо- минающего устройства в требуемых режимах.

Блоки и элементы, входящие в состав предлагаемого устройства, можно реализовать следующим образом.

Составитель А.Воронин

Редактор М.Петрова Техред Т.Маточка

Корректор M.äåì÷èê

Заказ 10094/43 Тираж 583 Подписное

ВНИИНИ Государственного комитета "."СР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород,ул. Проектная, 4

3 1

Коммутатор 3 и ключ 8 можно выполнить на основе реле, герконов, микросхемных ключей нли на обычных коммутаторах, линию 4 задержки — на основе произвольной аналоговой линии задержки (например, ультразвуковой), усилители 5 и 6 и сумматоры

1 и 2 — на основе операционных усилителей, охваченных обратными связями, причем усилитель 5 должен

-включать корректирующие цепи и обратные связи, обеспечивающие равенство единице передаточной функции совокупности каскадно соединен134967 4 ных блоков 1, 3, 4, 8 и 9. Блок 7 управления можно выполнить, например, на основе микропроцессора или микро-ЭВМ.

Использование предлагаемого запоминающего устройства в автоматике, вычислительной технике и, в частнос-. ти, в качестве динамического запоминающего устройства импульсных сигна10 лов произвольной формы в отличие от прототипа позволяет повысить точность процессов записи, воспроизведения и регенерации (хранения) записанных сигналов в 2-2 5 раза.