Устройство для вычисления функции @ = @ + @

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ + в , содержащее два регистра, два сумматора и коммутатор, причем входы первого и второго регистров соединены с соответствующими входами устройства , выход коммутатора подключен к первому входу первого сумматора, выход которого соединен с выходом устройства, о тличающееся тем, что, с целью повышения быстродействия, оно содержит третий сумматор, вычитатель и преобразователь в дополнительный код, причем первые входы второго, и третьего сумматоров и вычитателя подключены к выходу первого регистра , выход второго регистра подключен к вторым входам второго и третьего сумматоров и вычитателя, выходы второго и третьего сумматоров подключены к информационным входам коммутатора, управляющий вход которого соединен с выходом знакового разряда вычитателя и с управляющим входом преобразователя в дополнитель ный код, выход которого подключен к второму входу первого сумматора, информационный выход вычитателя соединен с информационным входом преобразователя в до (Л полнительный код.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТ ИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1136153 A

4(51) G 06 F 7/544

ОПИСАНИЕ ИЗОБРЕТЕНИ5 /

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3603695/24-24 (22) 09.06.83 (46) 23.01.85. Бюл. Р 3 (72) H. Н. Касаткин и А. С. Тарасов (53) 681.3 (088.8) (56) 1. Авторское свидетельство СССР

No 1001085, кл. G 06 Е 7/38, 1981.

2. Авторское свидетельство СССР И 964634, кл. 6 06 F 7/552, 1981 (прототип). (54) (57). УСТРОЙСТВО ДЛЯ ВЬИИСЛЕНИЯ

ФУНКЦИИ Х=1Йаеаа, ееаержаеаее аеа регистра, два сумматора и коммутатор, причем входы первого и второго регистров соединены с соответствующими входами устрой 1 ства, выход коммутатора подключен к первому входу первого сумматора, выход которого соединен с выходом устройства, о тл и ч а ю ш е е с я тем, что, с целью повышения быстродействия, оно содержит третий сумматор, вычитатель и преобразователь в дополнительный код, причем первые входы второго. и третьего сумматоров и вычитателя подключены к выходу первого регистра, выход второго регистра подключен к вторым входам второго и третьего сумматоров и вычитателя, выходы второго и третьего сумматоров подключены к информационным входам коммутатора, управляющий вход которого соединен с выходом знакового разряда вычитателя и с управляющим входом преобразователя в дополнитель ный код, выход которого подключен к второму входу первого сумматора, информационный выход вычитателя соединен с информационным входом преобразователя в дополнительный код.,11361

Изобретение относится к вычислительной технике, в частности к устройствам для определения модуля комплексных чисел в реальном времени, и может быть использовано в вычислительных устройствах. 5

Известно устройство для вычисления моду. ля комплексного числа, содержащее два входных регистра, два сумматора, вычитатель и коммутатор, выход которого соединен с выходом устройства, информационные входы коммутаторов подключены к выходам соответствующим сумматоров, выход знакового разряда вычитателя подключен к управляющему входу коммутатора, первые входы сумматоров и вычитателя подключен к выходу первого входного регистра, вторые входы сумматоров и вычитателя подключены к выходу второго входного регистра, входы первого и второго входных регистров подключены к соответствующим входам 20 устройства (1) .

Однако устройство характеризуется недостаточной точностью вычисления значения модуля комплексного числа, Наиболее близким к изобретению по тех- 25 нической сущности является устройство для выеиенеиия функции Х =)где+Ее, содержащее первый входной регистр, второй входной регистр, два коммутатора, первый сумматор, второй сумматор, выход которого яв- 30 ляется выходом устройства, и схему сравнения, выход которой соединен с управляющими входами коммутаторов, информационные входы которых соединены с выходами первэго и второго входных регистров соответственно, входы схемы сравнения подключены к выходам входных регистров„входы первого сумматора подключены,к выходам первого коммутатора и второго сумматора, четыре входа которого подключены к выхо- 40 ду второго коммутатора (2).

Недостатком известного устройства являются его сравнительно низкое быстродействие, обусловленное последовательным прохождением сигнала через все блоки устройства, а также тем, что второй сумматор должен производить суммирование четырех чисел.

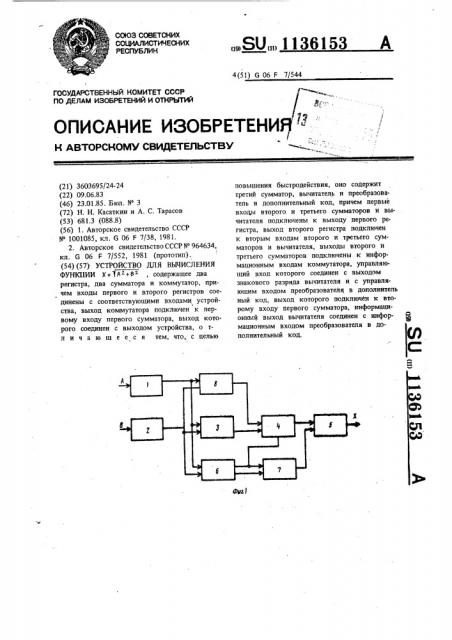

53 2 читатель и преобразователь в дополнительный код, причем первые входы второго и третьего сумматоров и вычитателя подключены к выходу первого регистра, выход второго регистра подключен к вторым входам второго и третьего сумматоров и вычитателя, выходы второго и третьего сумматоров подключены к информационным входам коммутатора, управляющий вход которого соединен с выходом знакового разряда вычитателя и с управляющим входом преобразователя в допол нительный код, выход которого подключен к второму входу первого сумматора, информационный выход вычитателя соединен с информационным входом преобразователя в дополнительный код, На фиг, 1 приведена структурная схема. предлагаемого устройства; на фиг. 2 — график относительной погрешности вычислений д" (%) от отношения А и В. Устройство содержит регистр 1, регистр 2, сумматор 3, коммутатор 4, сумматор 5, вычитатель 6, преобразователь 7 в дополнительный код, сумматор 8.

Устройство функционирует в соответствии с приближенной зависимостью ген А «В ИРР(А ОЕХЬВ) ер -А,В; (1J

1,5 A +В 1,5 |8+0,4È6Д) ПРИ Ц)Д.

Данная аппроксимация получена при разложении в степенной ряд функции +х при (X ) с при

А Ъв ),убг)Аг,вг — 166 А г()«(в)А)г» (2)

1,5 Д (1+0416 — ) = 1,5(Д+ 0,416 В).

Выбор коэффициента 1,56 обусловлен более простой апп реализацией устройства. Его можно рассматривать как масштабный и учитывать при необходимости в дальнейших вычислениях.

Цепь изобретения — повышение быстродействия.

Поставленная цель достигается тем, что

50 устройство для вып исления функции X4A +Â r содержащее два регистра, два сумматора и: коммутатор, причем входы первого и второго регистров соединены с соответствующими входами устройства, выход коммутатора 55 подключен к первому входу первого сумматора, выход которого соединен с выходом устройства, содержит третий сумматор, выф1

1,5(A+ 0,4166) = 1,5 А+ 0,6258=2 А+

+ 2 38 —. 2 1()()- Р (Н

1,5(.g +0,416 Д) ." 1,5$+ 0,625Д=2 Ь+

+2 A — 2 (Д-В I (3) В предлагаемом устроистве умножение на коэффициенты 1,56 и 0416 заменяется суммирование.м со сдвигом входных сигналов

А .. и В в соответствии с выражениями:

1136153

+С +С

2 Еыц ирЕоор ом2. гдеС „, С ком

6 см 2 см4

С аы ораоб

Учитывая, --2С = 2С см4 см2 см ((С см

Сэ 4Ссм I С2=36см t

100% =

1,56 А 1+—

)+ 041Ü—

В! А,96 — 1 100и/о (Я )2 з

Устройство работает слецук>щим образом.

Коды операндов А и В с выходов регистров 1 и 2 подаются на входы сумматоров

3 и 8 н.вычитателя 6. В сумматорах 3 н 8 производится суммирование в соответствии с выражениями (2+"4 + 2 8 ) и (2+ 8+

+ 2 3А). Операция умножения операндов А и В на коэффициенты (2 ) и (2 3) осуществляется подключением регистров 1 и 2 со сдвигом на один разряд влево для коэффи- 10 циента 2+ и со сдвигом на три разряда вправо для коэффициентжф 3 на входы сумматоров

3 и 8.

Одновременно с сумчированием в сумматорах 3 и 8 в вычитателе 6 производится . вычитание операнда В из операнда А. При условии А В знаковый разряд вычитателя

6 устанавливает коммутатор 4 в состояние, при котором на его выходе появляется код выражения (2+уA+ 2 3 8 ) .при условии

„А (В на выходе коммутатора 4 появляется код выражения (2+ В + 2 3 А), Знаковый разряд и код разности (А — В). с выхода вычитателя 6 подается на вход преобразователя 7, который выполняет опе- 25 рацию в соответствии c выражением /А-В/ одновременно о прохождением сигнала через коммутатор 4. Код с выхода преобразователя 7 попается на вход сумматора 5 со сдвигом вправо на один разряд для получения кода в соответствии с выражением 2 "1А — Bl Код

30 с выхода коммутатора 4 подается на вход сумматора 5, в результате чего на выходе сумматора 5 получаем значение (2 "A+

+ 2  —.2 "(А-61).при А Ъ В и значение . (2+" 8+2 34 — 2 f4-61) при А (В, что соответствует значению искомой функции, помноженной на коэффициент 1,56.

Сравнивая быстродействие предлагаемого устройства с известным, находим максимальное время вывевенин функции Згйагна в ео

:Ъ известном устройстве (t ) и в нредлагае-. мом (С .).

+С . 1 ск Ср ком см4 См2 время выполнения операции срав пения; время задержки сигнала в коммутаторе; время суммирования двух чисел; время суммирования четырех чисел; время вычитания в вычитателе; время преобразования в дополнительный код. что

1 =С =С «Ð выч см2 ореол см у т.е. предлагаемое устройство является более быстродействующим. Кроме того, эа счет исключения операции суммирования четырех чисел упрощается его схема.

Относительная погрешность d"(% ) вычислении функции 1,уордаера в предлагаемом устройстве, определяемая по формуле

15А 1+0416 — )-156 1+ — г А! (4J даже в самом худшем случае, когдап A=0,42, не превышает 4%, т.е. не превышает погрешность известного устройства.

1136153

6, С

В 02 О 40 05 Ц 47 И 09

Фиг.Z

Составитель В. Березкин

Техред M. Кузьма Корректор М.Демчик

Редактор Н. Бобкова

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 10286/36 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5