Универсальный логический модуль

Иллюстрации

Показать всеРеферат

УНИВЕРСАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ, содержащий регистр сдвига, отличающийся тем, что, с целью уменьшения аппаратурных зат рат, в него введены счетчик, схема сравнения, элементы ИЛИ, мультиплек сор, элемент ЗАПРЕТ и Генератор импульсов , выход которого соединен с первым входом элемента ЗАПРЕТ, втор вход которого соединен с входом бло кировки мультиплексора.выходом схемы сравнения, первая группа входов которой соединена с первой группой м из w информационных входов модуля, вторая группа m входов схемы сравнения соединена с выходами счетчика , вход установки которого соединен с входом сброса модуля и входом установки в О регистра сдвига, счетный вход счетчика соединен с выходом элемента ЗАПРЕТ и первым входом первого элемента ИЛИ, второй вход которого соединен с входом синхронизациимодуля, выход первого элемента ИЛИ соединен с входом синхронизации регистра сдвига, вход записи которого соединен с выходом второго элемента ИЛИ, входы которого соединены с входом настройки модуля и выходом старшего разряда регистра сдвига соответственно, выходы разрядов с номерами js(i-i)x 2(,2 JKOToporo соединены с информационными входами мультиплексора , управляющие входы которого соединены с второй группой из n-m информационных входов модуля, выход мультиплексора является выходом модуля .

СООЗ СОВЕТСКИХ

РЕСПУБЛИК (19) (11) 4 (5!) G06 F 7 00 ;f !

ОПИСАНИЕ ИЗОБРЕТЕНИЯ! с свтотосомт ссстостссостст (21) 3637289/24-24 (22) 23.08,83 (46) 30.01.85.Вюл.9 4 (72) Л.Б.Авгуль, Н.Ф,Окулович, В.А.Мищенко и СсН.Макареня (53) 68!.3 (088.8) (56) 1. Авторское свидетельство СССР

М 911507, кл. G 06 F 7/00, 1980.

2. Якубайтис Э.A. Универсальные логические элементы. — "Автоматика и вычислительная техника", 1973, )1 - 5, с. !5, рис, 3 (прототип). (54)(57) УНИВЕРСАЛЬНЫЙ ЛОГИЧЕСКИЙ

МОДУЛЬ, содержащий регистр сдвига, отличающийся тем, что, с целью уменьшения аппаратурных затрат, в него введены счетчик, схема

l сравнения, элементы .ИЛИ, мультиплексор, элемент ЗАПРЕТ и генератор импульсов, выход которого соединен с первым входом элемента ЗАПРЕТ, второй вход которого соединен с входом блокировки мультиплексора, выходом схемы сравнения, первая группа входов которой соединена с первой группой

1У из tn информационных входов модуля, вторая группа m входов схемы сравнения соединена с выходами счетчика, вход установки в "0" которого соединен с входом сброса модуля и входом установки в "0" регистра сдвига, счетный вход счетчика соединен с выходом элемента ЗАПРЕТ и первым входом первого элемента ИЛИ, второй вход которого соединен с входом синхронизации модуля, выход первого элемента ИЛИ соединен с входом синхронизации регистра сдвига, вход записи которого соединен с выходом второго элемента ИЛИ, входы которого соединены с входом настройки модуля и выходом старшего разряда регистра сдвига соответственно, выходы разрядов с номерами j=(i-11«

«2 (i=1,2 " )которого соединены с информационными входами мультиплексора, управляющие входы которого соединены с второй группой из и-rn информационных входов модуля, выход мультиплексора является выходом модуля.

13745

1 1

Изобретение относится к вычислительной технике и автоматике и предназначено для реализации всех логических функций п переменных, Известно устройство для реализации всех логических функций и переменных, содержащее 2" элементов И элемент ИЛИ, два дешифратара, п информационных и 2" настроечных входов и Один выход 51 3.

Недостатком устройства является большое числа внешних входов, которое равно 9 = n + 2".

Наиболее близким техническим решением к предлагаемому устройству является универсальный логический элемент на п переменных, содержащий сдвигающий регистр, 2" элементов И на (n. + 1) входов, 2 диодов, и и элементов HE, n информационных входов, один настроечный вход, вход синхрснизации регистра и один выход 12 !.

Недостатком этого, элемента является ега большая сложность, которая может быть подсчитана па

I формуле: S = S рег+ S где S рег сложнс сть схемы сдвигающега регистра, S = 2" (n+ 2)+ и — сложность операционной части элемента.

Цель изобретения — уменьшение аппаратурных затрат °

l5

25

45

Поставленная цель достигается тем, что в универсальный логический модуль, содержащий регистр сдвига, 35 введены счетчик, схема сравнения, элементы ИЛИ, мультиплексор элемент ЗАПРЕТ и генератор импульсов, выход которого соединен с первым входом элемента ЗАПРЕТ, второй вход которого соединен с входом блокировки мультиплексора и выходом схемы сравнения, первая группа входов которой соединена с первой группой из m информационных входов модуля, вторая группа из ш входов схемы сравнения соединена с выходами счетчика,:вход установки в "Оп которого соединен с входом сброса модуля и входом установки в "Оп регистра сдвига, счетный вход счетчика соединен с выходами элемента ЗАПРЕТ и первым входом первого элемента ИЛИ, второй вход которого соединен с входом синхронизации модуля, выход первого элемента ИЛИ соединен с входом синхронизации регистра сдвига, вход записи которого соединен с вы7 2 ходом второго элемента ИЛИ, входы которого соединень1 с входом настройки модуля и выходом старшего разряда регистра сдвига соответственно, выходы разрядов с номерами

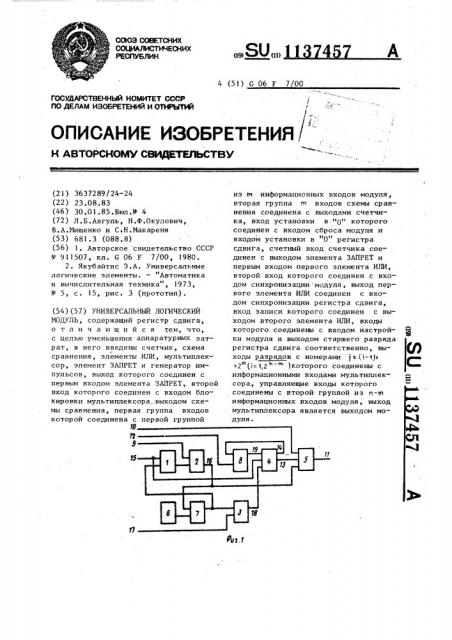

j = (i-! ) ° 2 (i = 1,2" ) которога соединены с информационными вхоI дами мультиплексора, управляющие входы которого соединены с второй группой из n-m информационных входов модуля, выход мультиплек сора является выходом нуля, На фиг, 1 представлена структурная схема универсального логического модуля! на фиг, 2 — схема соответствия между разрядами регистра сдвига и сигналами настройки.

Иадуль содержит счетчик 1, схему 2 сравнения, первый элемент ИЛИ 3, регистр 4 сдвига, мультиплексор 5, генератор 6 импульсов,.элемент ЗАПРЕТ 7 и второй элемент ИЛИ 8. Первая группа из m информационных входов 9 модуля соединена с первой группой входов схемы сравнения 2, вторая группа из и-ш информационных входов 10 — с управляющими входами мультиплексора 5, выход которого является выходом 11 модуля. Вход 12 настройки соединен с первым входом второго элемента ИЛИ 8, выход которого соединен с входом записи регист— ра 4. Выходы 13 регистра соединены с информационными входами мультиплексора 5. Выход !4 регистра 4 соединен с вторым входом второго элемента

ИЛИ 8, Вход сброса 15 модуля соединен с входом установки в "0" регистра 4 и входом установки в "0" счетчика 1, счетный вход которого соединен с выходом элемента ЗАПРЕТ 7 и первым входом первого элемента ИЛИ 3. Выходы счетчика соединены с второй группой входов схемы 2 сравнения, выход 16 которой соединен с вторым входом (входом запрета ) элемента

ЗАПРЕТ 7 и входом блокировки мультиплексора 5. Выход генератора импульсов 6 соединен с первым входом элемента ЗАПРЕТ 7. Вход .17 синхронизации модуля соединен с вторым входом первого элемента ИЛИ 3, выход 18 которого соединен с входом синхронизации регистра 4, Вход 19 записи регистра 4 соединен с выходом второго элемента ИЛИ д.

Разрядность счетчика 1 — ш, реп гистра 4 сдвига — 2 двоичных разря1137

3 дов. Выход 14 регистра 4 является выходом старшего нулевого разряда, а вход записи 19 — входом младшего (2"- 1)-го разряда. Группа выходов 13 регистра 4 содержит выходы

Ъ-т

2 разрядов, а именно: выходы разрядов с номерами

j = (i-1) ° 2 (i 1,2" ). (1)

Для настройки модуля на реализацию некоторой нулевой функции !о

f (х„, х„) на вход-15 модуля поступает импульс, обнуляющий счетчик 1 и регистр 4. Затем на вход синхронизации 17 модуля подаются импульсы синхронизации регистра сдви-15 га 4, которые сопровождают 2"сигналов настройки, последовательно поступающих на вход 12 модуля.

Сигналы настройки V ., 1 = !,2 принадлежат множеству (0«III« причем ур двоичный вектор " = (U, U2 " U») соответствует двоичному номеру реализуемой булевой функции в классе функций и переменных. На вход 12 модуля сигналы настройки U должны д поступать в такой последовательности, чтобы через 2 тактов в i-ом разряд де регистра оказалась настройка U причем i u j связаны между собой следующими соотношениями: (p 1) 2 "+ Ы, (2) где oI = — — --

2" «У i — (d-1) 2

Ф

Для n = 4 и m = 2 соответствие между разрядами регистра i u настройками U. показано на фиг. 2.

Таким образом, после заполнения регистра 4 всеми 2 настройками и на информационные входы мультиплексора буду поданы настройки с номе- 40 рами У, j = 1,2" (на фиг.2, U» U> .U» U4). Если осуществить кольцевой сдвиг содержимого регистра 4 на один разряд, то на информационные входы мультиплексора посту- 45 пят наст ойки U !, ) = 2" 1п+

+ 1, 2 2 на фиг. 2, U5, U, Пч Пв) и т.д, После занесения в регистр сдвига 4 кода настройки модуль готов к 50 работе.

Работа модуля основана на следую.щем принципе. Всякую булевую функ-. цию п переменных f (х, х ) можи но представить в виде: 55

Ь„«х„-) — х,хг « ° ° ° « (п о (.,+1 «>n)!«

217г « ° ° ° «Х зтз f1 (XI«I«p«Х()Ч ° ° ° ЧХ1Х « ° ° ° « хт (x, (хю„, х ), (з) 457 4 где fi (х,„,х„) = Х (х„, х„) при

i — и конституенте аргументов и

x1 «xh равной единице (1 = О, 2 — 1) .

Тогда, если разбить таблицу истинности функции f (х,, х„) на 2 равных частей длины 2" бит, ее (i + 1)-я часть будет представлять собой таблицу истинности функции

f<(х ... х„) . Поскольку вектор (U„ Uã, U „ ) совпадает с г двоичным номером реализуемой функции Е (х,, х„), то настройка

U- j = 2" численно равна

j «« значению функции f (х „, х„) (на наборе j — 1. Следовательно, таблица истинности фунхции ,f (x „„, xÄI соелалает с настройками U j = I . 2" + ,+ Il-Ill

В предлагаемом модуле функции

f;(х „, х„), i = 0,2 — 1 реализуются мультиплексором, на управляющие входы которого подаются аргументы х, х„, а на информацион П+1 ные — настройки U . 2(т ("+ ), (i+ )) 2Ь («

В регистр сдвига настройки наносятся (см. (2) ), и на информационные входы мультиплексора подаются сигналы с выходов таких разрядов регистра (см.(1)), чтобы при кольцевом сдвиге регистра на один pasряд сигналы U j = i 2"ц1+ 1, n-tn (i+1) -2 изменились на сигналы UI,, к = (i+I) - 2 + 1, (i +1)-2", при i = 0,2(" -2, и на сигналы U «

r = l 2 m npu i = 2 -I. Таким образом, при кольцевом сдвиге регистра на один разряд мультиплексор перестраивается с реализации функции f. (х „, x„) на реализацию (Ъ+1 «П функции f +1 (х„„„, х„) при i 0,2 -2 или на реализацию функции

f(х...х)при i =2-(.

Модуль работает следующим образом.

Перед началом работы счетчик 1 обнулен, а регистр сдвига 4 содержит код настройки. На информационные входы мультиплексора поданы сигналы U j = ),2" (" «соответствующие функции f (х,„, х„) . На управляющие входы мультиплексора 5 поступают младшие n-m аргументОв функции f (х, х„,), а на вход схемы сравнения — старшие m разрядов. Если все х1,= О, к = 1, ш, то на выходе 16 схемы 2 сравнения появится

5 I I 37457 сигнал ") ", поступление которого на вход блокировки мультиплексора 5 разрешит появление на выходе модуля сигнала, соответствующего значению (х„, х„) на данном наборе аргументов. Одновременно сигнал с выхода )6 поступит на вход запрета элемента

ЗАПРЕТ 7 и заблокирует импульсы генератора 6 импульсов, Если не все хф 0, к = 1, m, то на выходе 16 схема 2 сравнения появится сигнал "О", заблокирующий мультиплексор 5 и разрешающий прохождение импульсов генератора 6 через элемент 7. Импульс генератора, пройдя через элементы 7 и 3, осуществит кольцевой сдвиг регистра 4 на один разряд. На информационных входах мультиплексорa 5 появятся сигналы U1, 3 = 2" + 1 2 2" р соответствую- Ы иие функции f, (x,, x„) Одновременно импульс с выхода элемента ЗАПРЕТ 7 переведет счетчик 1 в очередное состояние 000...01 Если х х не совпадут с новым состоя- 25

1Р кием счетчика, то очередной импульс генератора 6 осуществит новый кольцевой сдвиг регистра 4 и переведет счетчик в очередное состояние. Так будет продолжаться до тех пор, пока состояние счетчика не станет рядного совпадения с m старшими разрядами x„, х . Одновременно будет осуществляться кольцевой сдвиг регистра 4.

5 Таким образом, старшие разряды х„, х выбирают функцию Е1(х „, х„), а младшие х „, х — значение этой

)у)+1 и функции при данных значениях х, x„, т.е. в соответствии с выраIn+1 жением (3) реализуется функция

f Гх„, х„), настройки которой хранятся в регистре 4.

Достоинством предлагаемого модуля является малое число входов и мень15 шая по сравнению со схемой известного модуля сложность, которая может быть рассчитана по формуле

8оха рег + 8о р

8о= S т+ $а+Бмк+ 6 — сложность операционной части генератора импульсов;

Бй,к= 2" (n — m1-1) и†сложность схем >)

ЗО ш+ 2 мультиплексора, тогда Б = Брй,-+ 2" (h — m + ) +

h + + h = m = 2 сложность операционной части предлагаемого модуля (т.е, части модуля без регистра для хранения настроек)

S = 48, в то время как сложность операционной части известного модуля при и = 4 S = 2" О) + 2) + и = 100, Таким образом, при одинаковой сложности регистра для хранения настроек сложность операционной части предлагаемого модуля более, чем в два раза меньше сложности операционной части известного моду45

Предлагаемый модуль имеет w + 3 входа (как и известный (2) р в то время как число входов известных универсальных модулей, с настройками, 5О принадлежащими множеству (О, 1), рав— но Р =h+ 2". поразрядно совпадать с поступившими аргументами. Тогда с выхода 16 схемы сравнения 2 на вход запрета элемента ЗАПРЕТ 7 поступит сигнал "1 " заблокирующий импульсы генератора 6 ..

На вход блокировки мультиплексора 5 поступит сигнал "1", а на его информационные вхорь — сигналы U соответствующие функции f гх,х„), где i — номер конституенты единицы, которук) составят поступившие аргументы х х . Тогда согласно выраже,) ° нию (3) на выходе модуля появится сигнал, соответствующий значению функции f Гх, х„) на данном входном наборе.

При поступлении очередных значений х„, х„ модуль работает аналогично. Состояние счетчика будет последовательно изменяться до поразмодуля; сложность схеме>1 регистра;

8 = 8 — сложность схемы

cr счетчика;

S = 10 — сложность схемы

1137457

w©4 ч Q

Ъ з фЖ ф

4Ь

Составитель А.Федоров

Техред Т.Дубинчак

Редактор М.Недолуаенко

Корректор С.Шекмэр

Подписное

Филиал ППП "Патент" ° r.Óàãîðoä,,óë.éðîåêòíàÿ, 4

Заказ )0525/36 Тиржк 710

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий!!3035, Москва, Ж-35, Раужская наб., д.4/5