Устройство для отладки программ

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ, содержащее блок памяти, первый элемент задержки и триггер, . причем адресный, информационный входы и .вход считывания устройства соединены соответственно с адресным, информационным входами и входом считывания блока памяти, о т л и ч а ю щ е е ся тем, что, с целью повьшения быстродействия при отладке программ , в устройство введены шифратор команды Останов, группа элементов И, группа элементов ИЛИ, второй элемент задержки, а в блок памяти введен дополнительный разряд, причем информационные вьЬсоды блока памяти и выход дополнительного разряда блока памяти соединены соответственно с первыми входами элементов И группы и с единичным входом триггера, единичный и нулевой выходы которого соединены с первыми входами первого и второго элементов И соответственно, выход первого элемента И соединен со вторыми входами элементов И группы, выходы которых соединены с первь ми входами элементов ИЛИ группы, выход второго элемента И соединен со входом шифратора команды Останов, выходы которого соединены со вторыми входами соответствующих элементов ИЛИ группы, вход считывания устройстСП ва через первый элемент задержки соединен со вторыми входами первого и второго элементов И, выход второго элемента задержки соединен с нулевым входом триггера, вход второго элемента задержки подкщ)чен ко входу второго элемента И, выходы элементов ИЛИ оо ю группы образуют группу информационных выходов устройства.

СОЮЗ СОВЕТСНИХ

РЕСПУБЛИН 4(51) G 06 F 12/00 G 06 F 11/26

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТНРЬ1ТИЙ

1 !

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPCHOMY СВИДЕТЕЛЬСТВЪ -л (21) 3618204/24-24 (22) 11.07.83 (46) 30.01.85. Бюл. № 4 (72) Л.О.Беспалов, В.Я.Зельченко, М.Н.Рахманин, В.В.Савуткин, Т.К.Цогоев и В.И.Шагулин (53) 681.3(088.8) (56) 1. Патент США № 3935563, кл. 340-172.5, 1975.

2. Авторское свидетельство. СССР № 754419, кл. С 06 F 13/06, 1979. (54)(57) УСТРОЙСТВО ДЛЯ ОТЛАДКИ

ПРОГРАММ, содержащее блок памяти, первый элемент задержки и триггер, причем адресный, информационный входы и .вход считывания устройства соединены соответственно с адресным, информационным входами и входом считывания блока памяти, о т л и ч а ю— щ е е с я тем, что, с целью повышения быстродействия при отладке программ, в устройство введены шифратор команды "Останов", группа элементов И, группа элементов ИЛИ, второй элемент задержки, а в блок памяти введен дополнительный разряд, причем информа„SU„„1137472 A ционные выходы блока памяти и выход дополнительного разряда блока памяти соединены соответственно с первыми входами элементов И группы и с единичным входом триггера, единичный и нулевой выходы которого соединены с первыми входами первого и второго элементов И соответственно, выход

- первого элемента И соединен со вторыми входами элементов И группы, выходы которых соединены с первыми входами элементов ИЛИ группы, выход второго элемента И соединен со входом шифратора команды "Останов", выходы которого соединены со вторыми входами соответствующих элементов

ИЛИ группы, вход считывания устройства через первый элемент задержки соединен со вторыми входами первого и второго элементов И, выход второго элемента задержки соединен с нулевым входом триггера, вход второго элемента задержки подк почен ко входу второго элемента И, выходы элементов ИЛИ группы образуют группу информационных выходов устройства.

1137472

Изобретение относится к цифровой вычислительной технике и может быть использовано при отладке программ за. дач специализированных ЦВМ, содержащих в своем составе штатные блоки памяти (ВП) с рабочими программами.

Иэвестйо устройство для отладки программ, содержащее генератор тактовых импульсов, рабочие регистры, счетчик команд, блок памяти программ, 1О блок формирования адресов, блок ком" мутации и блок управления, который после исполнения каждой выполняемой команды основной программы с помощью блока коммутации осуществляет вставку и исполнение нескольких вспомога- тельных служебных команд, распечатывающих содержимое основных регистров и счетчика команд ЦВМ. После распечатки блоком управления производится формирование адреса следующей команды (I) .

Недостатком этого устройства является отсутствие оперативного контроля правильности прохождения программы по намеченной трассе адресов и в реальном масштабе времени.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее блок памяти ЗО программ, адресный, информационный входы и вход считывания которого сое" динены соответственно с адресным, информационным входами и входом считывания устройства, оперативный за- З5 поминающий блок, блок анализа кода команды, вход которого подключен к выходу блока памяти программ, блок организации переписи информации, входы которого связаны соответствен- 40 но с адресным входом блока памяти программ и с выходом блока анализа кода команды. Выход блока организации переписи соединен с входом оперативного запоминающего блока. 45

Известное устройство, при наличии в коде команды условного перехода, осуществляет запись адреса этой команды в соответствующую ячейку опера-50 тивного запоминающего блока. По завершении прохождения программы или ее части производится отображение хода вычислительного процесса, зафиксированного в оперативном запоми- у нающем блоке f2j

Недостатком устройства-прототипа является невозможность оперативно . контролировать правильность прохожде; ния программы.

Цель изобретения - повышение быстродействия при отладке программ.

Поставленная цель достигается тем, что в устройство для отладки программ, содержащее блок памяти, первый элемент задержки и триггер, причем информационный, адресный входы и вход считывания устройства. соединены соответственно с адресным, информационным входами и входом считывания блока памяти, введены шифратор команды "Останов", группа элементов И, группа элементов HJIH, второй элемент задержки, а в блок памяти введен дополнительный разряд, причем информационные выходы блока памяти и выход дополнительного разряда блока памяти соединены соответственно с первыми входами элементов И группы и с единичным входом триггера, единичный и нулевой выходы которого соединены с первыми входами первого и второго элементов И соответственно, выход первого элемента И соединен с вторыми входами элементов И группы, выходы которых соединены с первыми входами элементов ИЛИ группы, выход второго элемента И соединен с входом шифратора команды "Останов", выходы которого соединены с вторыми входами соответствующих элементов КПИ группы, вход считывания устройства через первый элемент задержки соединен с вторыми входами первого и второго элементов И, выход второго элемента задержки соединен с нулевым входом триггера, вход второго элемента задержки подключен ко входу второго элемента И, выходы элементов ИЛИ группы образуют группу информационных выходов устройства.

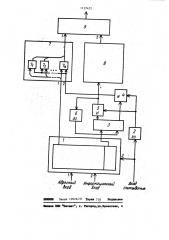

На чертеже приведена структурная схема устройства.

Устройство содержит блок 1 памяти, первый элемент 2 задержки, триггер 3, единичный вход которого соединен с выходом дополнительного разряда блока 1.памяти, первый и второй элементы И 4 и 5, первые входы которых подключены соответственно к нулевому и единичному выходам триггера 3, вторые входы объединены и связаны с выходом элемента 2 задержки, второй элемент 6 задержки, выход которого подключен к нулевому входу тцигге à 3, группу элементов И 7, шифра-

11374 з тор 8 команды "Останов" и группу элементов ИЛИ, выход которой является выходом устройства, причем адресный, информационный входы и вход считывания устройства соединены соответственно с адресным, информационным входами и входом считывания блока 1 памяти . Вход считывания блока 1 памяти связан с входом первого эле- мента 2 задержки. Вход второго эле- 10 мента 6 задержки объединен с входом шифратора 8 и подключен к выходу элемента И 5.

Информационные выходы блока 1 памяти и выход элемента И 4 соединены !5 соответственно с первыми и вторым входами группы элементов И 7. Выход группы элементов И 7 подключен к первому входу группы элементов. ИЛИ .9, второй вход которого связан с выхо- 20 .дом шифратора 8 команды "Останов" °

Устройство работает следующим образом.

Через информационный вход устройства производится загрузка блока 1 25 памяти исходным вариантом программы, подлежащей отладке. Одновременно по . этим же адресам осуществляется запись информации в дополнительный разряд блока 1 памяти. Значение информа- 0 ции, записанной в дополнительном разряде, определяется трассой (ориентированным графом) адресов, используемых в процессе отладки. При этом под вершинами трассы понимаются адре->> са условных переходов. Затем, в процессе считывания на адресный. вход устройства подается код адреса выбираемой ячейки блока 1 памяти, а на вход считывания — сигнал опроса. 40

При наличии на входах блока 1 памяти кода адреса и сигнала опроса из блока производится считывание инфор72 мацки, которая поступает на первые входы группы элементов И 7 (информационная часть) и на единичный вход триггера 3 (информационная считанная из дополнительного разряда).

Сигнал опроса, поступающий на соответствующий вход блока 1 памяти, одновременно подается на вход первого элемента 2 задержки. Далее, этот сигнал,.задержанный элементом 2 задержки на время работы блока 1 памяти и установки триггера 3, поступает на второй вход элементов И 4 и 5.

В зависимости от состояния триггера 3 сигнал пройдет через элемент

И 4 или 5.

Первый случай соответствует ходу программы по намеченному пути выбираемых адресов. Во втором случае . оперативно устанавливается факт несоответствия в ходе трассы программы, С выхода элемента И 4 сигнал пос-. тупает на второй вход группы элемен-, тов И 7 и "подсвечивает" информацию, находящуюся на первом входе этой группы. В результате информационное слово, считанное иэ блока памяти, появляется на выходе группы элементов И 7 и проходит, через группу элементов ИЛИ 9 на выход устройства.

Если сигнал появляется .иа выходе элемента И 5, то он, во-первых, пройдя через второй элемент 6 задержки, устанавливает триггер 3 в исходное сос-. тояние, во-вторых, поступает на вход шифратора 8 команды "Останов", которая передается через группу элементов ИЛИ 9 на выход устройства.

Техническим преимуществом предлагаемого устройства является простота осуществления кбнтроля правильности прохождения программы в процессе ее отладки. !

1137472

Инрормационньи

Р У

ЗНИ1 Щ З каэ 10526/37 ТмРаа 710 П Ф

@.ann, е t. ymyo493eeay0RM ° 4