Устройство для вычисления обратной функции

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ОБРАТНОЙ ФУНКЦИИ, содержащее блок определения коэффициента, сумматор, первый второй, третийи четвертый интеграторы, причем информационный вход устройства соединен с входом приращения независимой переменной Первого интегратора, выходы приращения интеграла первого и второго интег раторов подключены соответственно к первому и второму входам сумматора , выход которого-соединен с первым входом приращения подынтегральной функции третьего интегратора, второй вход приращения подынтегральной функции.которого подключен к выходу приращения интеграла четвертого интегратора, а выход приращения подынтегральной функции - к входу приращения независимой переменной четвертого интегратора и к информационному выходу устройства, о т - личаюшееся тем, что, с целью увеличения быстродействия, в него введен пятый интегратор, вход приращения независимой переменной которого соединен с информационным входом устройства, выход приращения интеграла - с третьим входом сумматора, а выход подынтегральной функции - с информационным входом блока определения коэффициента, подключенного управляющим входом к управляющему входу устройства, а выходом - к входам второго и четвертого интеграторов, вход приращения независимой пере.менной второго ин- . тегратора соединен с выходом приращения интеграла третьего интегратора , входом приращения подынтегральной функции первого интегратора и входом приращения-независимой переменной пятого интегратора, блок определения коэффициента содержит две группы элементов И, первые -входы СО элементов И обеих групп образуют информационный вход блока, вторые входы первых элементов И обеих групп соединены с управляющим входом блока определения коэффициента, выход -го оо элемента И первой груцпыЛ 1,... Л где ц - число элементов в группе) соединен с вторыми входами ( +1)-го элемента И первой и второй групп, выходы элементов И второй группы образуют выход блока определения коэффициента .

„„SU„„1137478

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН.4 (51) G 06 F 15/328

ОПИСАНИЕ ИЗОБРЕТЕНИ 1

К ABTOPCH0MV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbfTN4 (21) 3485465/24-24 (22) 02,09,82 (46) 30.01.85. Бюл, N- 4 (72) В.А,Авдеев и В.Ф.Арсени (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (53) 681.32 (088.8) (56) 1, Майоров Ф.В, Цифровые интегрирующие машины. М., Машгиз, 1962, с, 47.

2. Авторское свидетельство СССР

У 942035,кл. G 06 F 15/328,1981 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ

ОБРАТНОЙ ФУНКЦИИ, содержащее блок определения кОэффициента, сумматор, первый, второй> третий и четвертый интеграторы, причем информационный вход устройства соединен с входом приращения независимой переменной первого интегратора, выходы приращения интеграла первого и второго интеграторов подключены соответственно к первому и второму входам сумматора, выход которого соединен с первым входом приращения подынтегральной функции третьего интегратора, второй вход приращения подынтегральной функции. которого подключен к выходу приращения интеграла четвертого интегратора, а выход приращения подынтегральной функции — к входу приращения независимой переменной четвертого интегратора и к информационному выходу устройства, о т л и ч а ю ш е е с я тем, что, с целью увеличения быстродействия, в него введен пятый интегратор, вход приращения независимой переменной которого соединен с информационным входом устройства, выход приращения интеграла — с третьим входом сумматора, а выход подынтегральной функции — с информационным входом блока определения коэффициента, подключенного управляющим входом к управляющему входу устройства, а выходом — к входам второго и четвертого интеграторов, вход приращения

Ф независимои переменной второго ин- . Q тегратора соединен с выходом приращения интеграла третьего интегратора, входом приращения подынтегральной функции первого интегратора и входом приращения независимой пере- Я

МрННоН пятого интегратора, блок определения коэффициента содержит две группы элементов И, первые .входы элементов И обеих групп образуют ин- CQ формационный вход блока, вторые входы первых элементов И обеих rpynn coe вфЬ динены с управляющим входом блока «Д определения коэффициента, выход -го Я© элемента И первой группы | ; = 1 э ° ° ° ю и, где ll — число элементов в группе), соединен с вторыми входами (i +1)-.ro элемента И первой и второй групп, выходы элементов И второй группы об,фЬ разуют выход блока опредепения коэффициента.

1 11З

Изобретение относится к вычислительной технике и может быть использовано для вычисления значения обратной функции на заданном интервале с корректировкой условия сходимости 5 на каждом шаге решения, о

Известно устройство для вычисления обратной функции, которое содержит интеграторы, соединенные между собой в соответствии с решением системы дифференциальных уравнений Шеннона (1), Недостаток известного устройства для вычисления обратной функции— низкое быстродействие, 15

Наиболее близким по технической сушности к изобретению является устройство для вычисления обратной функции, в состав которого входят первый, второй, третий и четвертый 20 интеграторы, первый, второй и третий сумматоры, регистр сдвига,.регистр коррекции и коммутатор (определитель коэффициента). 121, Недостаток известного устройства 25 относительно низкое быстродействие, вызванное тем, что к каждому шагу решения задачи (итерации) добавляются два такта, В первом дополнительном такте выполняется передача ин- gp формации иэ регистра сдвига через коммутатор (определитель коэффициента) в регистр коррекции, а во втором такте — передача информации из регистра коррекции в четвертый интег ратор. Необходимость осуществления второго дополнительного такта в каждой итерации вычисления обратной функции снижает быстродействие устройства.

Целью изобретения является увеличение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее блок определения коэффициента, сум- 45 матор, первый, второй, третий и четвертый интеграторы, причем информационный вход устройства соединен с входом приращения независимой переменной первого интегратора, выходы приращения интеграла первого и вторбго интеграторов подключены соответственно к..первому и второму входам сумматора, выход которого соеди нен с первым входомиприращения подын 55 тегральной функции третьего интегратора, второй вход котороГо прираще- . ния.подынтегральной функции которого

478 подключен к выходу приращения интег-, рала четвертого интегратора, а выход приращения подынтегральной функции к входу приращения независимой переменной четвертого интегратора и к информационному выходу устройства, введен пятый интегратор, вход приращения независимой переменной которого соединен с информационным входом устройства, выход приращения интегратора — с третьим входом сумматора, выход подынтегральной функциис информационным входом блока определения коэффициента, подключенного управляющим входом к управляющему входу устройства, а выходом — к входам второго и четвертого интеграторов, вход приращения независимой переменной второго интегратора соединен с выходом приращения интеграла третьего интегратора, входом. приращения подынтегральной функции первого интегратора и входом приращения независимой переменной пятого интеграто- ра, блок определения коэффициента содержит две группы элементов И, первые входы элементов И обеих групп образуют информационный вход блока, вторые входы первых элементов И обеих групп соединены с управляющим входом блока определения коэффициентов, выход 1; -го (= 1,..., П, где П вЂ” число элементов в группе), элемента И первой группы соединен с вторыми входами (+1)-го элемента И первой и второй групп, выходы элементов И второй группы образуют выход блока определения коэффициента.

Наличие дополнительного пятого интегратора и новых связей в устройстве приводит к тому, что в каждой итерации вычисления обратной функции имеется только один дополнительный такт (вместо двух тактов в известном устройстве) передачи информационнога слова с выхода подынтегральной функции пятого интегратора через ° блок определения коэффициента на входы приращения подынтегральной функции второго и четвертого интеграторов.

Так как число итераций для воспроизведения обратной функции на заданном интервале с помощью цифровых интеграторов с тернарным способом кодирования приращений достаточно велико (большая частота выдачи результатов решения), :то снижение числа тактов

3 1 в каждой итерации приводит к значительному увеличению быстродействия.

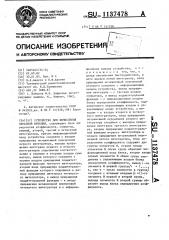

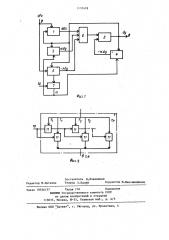

На фиг.1 представлена структурная схема устройства для вычисления обратной функции," на фиг,2 — структурная схема определителя коэффициента.

Устройство (фиг,1) содержит первый 1, второй 2, третий 3, четвертый 4 и пятый 5 интеграторы, сумматор 6 и: блок определения коэффициента 7, а также информационный выход устройства 8, информационный 9 и управляющий 10 входы, Блок определения коэффициента 7 (фиг,2} предназначен для выделения первого старшего единичного значения подынтегральной функции интегратора 5 и содержит элементы И 11, Устройство работает следующим образом.

При вычислении функции у = х для значений X приближающихся к нулю, погрешность вычислений в известных устройствах резко возрастает, Для устранения этого недостатка на каждом шаге вычисления функции производится корректировка условия сходимости решения. Для выполнения этого действия вводят коэффициент ()( корректировки условия сходимости, .тогда ()(y + xy = 1 + Ф,у (1)

Продефференцировав уравнение (1), получим

dy = ((x - x) dy - ydx), (2)

1 решением которого при заданных начальных условиях является функция у х

Дифференциальному уравнению (2) соответствует раэностное уравнение

137478

4 по которому ведутся вычисления в устройстве.

Разностная схема (3} должна быть устойчивой, т.е. иметь решение, сводящееся к решению дифференциаль.— ного уравнения (2) при h О.

Устойчивость решения уравнения (3) обеспечивается за счет выбора.коэф- фициента ;, ()(; (х;.

10 Перед началом вычислений в интеграторы 1, 2, 4 и 5 заносятся соответственно начальные значения ()(о, Мо и хо. Вычисление функции (1

15 х начинается в устройстве с мо" мента подачи на вход 9 устройства приращений dx. На выходах интеграторов 1, 2 и 5 формируются соответст, венно приращения -ydx,()(,dy и -xdy, которые поступают на входы сумматора 6, На выходе интегратора 3 вырабатываются приращения dy, которые поступают на соответствующие входы интеграторов 1, 2 и 5 таким образом, что с помощью интегратора 5 от-; рабатывается рассогласование приращений dy и (М-x)dy-ydx. После каждого шага решения (итерации) импульсом опроса, поступаяощим в синхронные О промежутки времени на управляющий вход 10, производится передача коэф фициента(на входы подынтегральной, функции интеграторов 2 и 4, Коэффи- циент К определяется с помощью схеЗ5 мы (см. фиг.2) как первое старшее единичное значение подынтегральной функции интегратора 5.

В данном устройстве нахождение коэффициента ()(, и ввод его в опреде40 ленные интеграторы осуществляется за один такт времени, что приводит к увеличению быстродействия устройства.

Таким1образом, введение новых

45 узлов и конструктивных связей позволяет увеличить быстродействие устройства.

1137478 ать

Фиг.2

Составитель И,Пчелинцев

Редактор М.Циткина Техред 3.Палий Корректор М.Максимишинец

Заказ 10526/37, Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4