Запоминающее устройство с коррекцией однократных ошибок

Иллюстрации

Показать всеРеферат

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОДНОКРАТНЫХ ОШИБОК по авт.св. № 1073799, отличающееся тем, что, с целью повышения надежности устройства, в него введены блоки сравнения, элемент И, триггер и элемент индикации, причем одни входы блоков сравнения подключены к выходам сумматоров по модулю два, другие входы - к выходам основного блока памяти, выходы блоков сравнения соединены с входами элемента И, выход которого подключен к одному из входов триггера, другие входы которого подключены к одлим из выходов блока управления, а выход триггера соединен с входом элемента индикации и является одним из выходов устройства. (Л с

СОЮЭ СОВЕТСНИХ

OIWll

РЕСПУБЛИК (191 1И) 4(51 б 11 С 29/00

" > аюа

Ю»ОПИСАНИЕ ИЗОБРЕТЕНИЯ

X A8TOPCXOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ll0 ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТНРЫТИЙ (61) 1073799 (21) 3612894/18-24 (22) 29.06.83 (46) 30.01.85. Бюл. И 4 (72) А.Л.Самойлов и Н.С.Щербаков (53) 681.327(088.8) (56) l.. Авторское свидетельство СССР

Ф 1073799, кл. G 11 С 29/00, 1982 (прототип). (54) (57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С

КОРРЕКЦИЕЙ ОДНОКРАТНЫХ ОШИБОК по авт.св. В 1073799, о т л и ч а ющ е е с я тем, что, с целью повышения надежности устройства, в него введены блоки сравнения, элемент И, триггер и элемент индикации, причем одни входы блоков сравнения подключены к выходам сумматоров по модулю два, другие входы — к выходам основного блока памяти, выходы блоков сравнения соединены с входами элемента И, выход которого подключен к одному иэ входов триггера, другие входы которого подключены к одним из выходов блока управления, а выход триггера соединен с входом элемента индикации и является одним иэ выходов устройства.

I I 137

Изобретение относится к вычислительной технике и может быть использовано в качестве запоминающего устройства в вычислительных системах, к которым предъявляются требования исправления однократных и обнаружения двукратных ошибок.

По основному авт.св. Ф 1073799 известно запоминающее устройство с коррекцией однократных ошибок, содер- 1О жащее основной и дополнительный блоки памяти, блок кодирования и блок управления, выход которого подключен к управляющим входам основного блока памяти и дополнительного блока памяти, входы которого соединены с выходами блока кодирования, входы которого объединены соответственно с входами основного блока памяти и яв— ляются информационными входами устройства, К мажоритарньгх элементов (где К вЂ” число информационных входов устройства и 2% сумматоров по модулю два, выходы которых подключены к одним из входов мажоритарньгх эле- . ментов, другие входы которых подключены к одним из выходов основного блока памяти, а выходы мажоритарных элементов являются информационными выходами устройства, одни из входов

-сумматоров по модулю два подключены

ЗО к другим выходам основного блока памяти, а другие входы — к выходам дополнительного блока памяти (1 J.

Известное устройство не обеспечивает обнаружения двукратных ошибок, 35 что снижает его надежность.

Цель изобретения — повышение надежности устройства.

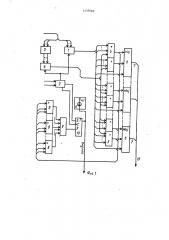

Поставленная цель достигается тем, что в запоминающее устройство 40 с коррекцией однократных ошибок введены блоки сравнения, элемент И, триггер и элемент индикации, причем одни входы блоков сравнения подклю-чены к выходам сумматоров по модулю 45 . два, другие входы — к выходам основного блока памяти, выходы блоков сравнения соединены с входами элемента И, вьиод которого подключены к одному из входов триггера, другие входы которого подключены к одним из выходов блока управления, а выход триггера соединен с входом элемента индикации и является одним из вьиодов устройства. 55 . Ha фиг.1 показана структурная схема предлагаемого запоминающего устройства с коррекцией Ьднократных

540 ошибок; на фиг.2 — структурная схема блока управления; на фиг.3 — Н-матрица, поясняющая подключение входоь устройства и основного блока памяти к блоку кодирования, для кода

"45, 36".

Запоминающее устройство с коррекцией однократных ошибок (фиг.l) содержит основной блок 1 памяти, блок

2 управления, блок 3 кодирования, дополнительный блок 4 памяти, сумматоры 5 по модулю два, мажоритарные элементы 6, имеющие выходы 7, блоки

8 сравнения, элемент И 9, триггер 10 и элемент 11 индикации.

Блок 2 управления (фиг.2) содержит элемент HF. 12, элемент 13 задержки, формирователи 14 и 15 сигналов, элемент HH 16, элемент И 17, группу элементов НЕ 18, элемент И 19, триггер

20 и кнопку 21 сброса.

В основу работы предлагаемого устройства заложено использование корректирующего кода, допускающего мажоритарное декодирование.

Устройство работает следующим образом.

Режим записи.

В этом режиме на входы устройства поступают импульс обращения„ признак операции "Запись" потенциал "1" информационное слово и код адреса.

Информационное слово подается на входы блоков 1 и 3. В блоке 3 разряды информации подключаются к входам сумматоров по модулю два в соответствии с алгоритмом, представленным в виде Н-матрицы (фиг.3), например, для корректирующего кода

"45, 36". В результате на выходе каждого сумматора образуется сумма по модулю два, являк цаяся одним иэ дополнительных избыточных разрядов

Каждый разряд информационного слова входит один раз в две (и только в две) суммы. Это позволяет при деко дировании однозначно получить истинное значение любого разряда путем суммирования по модулю два тех разрядов, которые размещены в строке

Н-матрицы, содержащей данный разряд.

Разряды информационного слова и разряды контрольной информации, полученной в блоке 3, записываются соответственно в блоки 1 и 4.

Режим считывания с коррекцией однократных ошибок.

В этом режиме на входы блока 2 поступают импульсы обращенчя и при25

При появлении двукратной ошибки s разрядах блоков 1 и (или 1 4 памяти также происходит формирование сигнала ошибки на выходе устройства, 3 1137 знак операции "Считывание". С выхоII Il да блока 2 потенциал Считывание поступает на входы блоков 1 и 4. По коду адреса из блоков 1 и 4 считывается основная и избыточная информация, которая поступает яа входы сумматоров 5 я мажоритарных элементов 6.

Если ошибок при считывании не было, то на выходах сумматоров 5 появляется результат, равный значению соответствующего разряда блока 1. Сигналы с выходов сумматоров 5 по модулю два подаются на два из трех входов мажоритарного элемента 6, на третий вход которого подается сигнал с выхода соответствующего разряда блока 1. Следовательно, при отсутствии ошибок яа всех трех входах мажоритарного элемента 6 значения одинаковы и равны значению выхода блока 1 соответствующего разряда. Учитывая, что мажоритарный элемент 6 работает по принципу "2 и 3", íà его выходе 7 присутствует значение, равное значению сигнала на всех его входах. Если при считывании из блоков 1 и 4 появляется ошибка в одном из разрядов, то на двух из трех входов мажоритарного элемента 6 будет

30 верное значение, при этом на его выхдде 7 как и в случае отсутствия ошибки будет значение, соответствующее истинному значению корректируемого разряда ияформации блока 1 памя- .

Режим считывания с обнаружением однократных и двукратных ошибок.

При появлении однократных ошибок в разрядах блока 1 или 4 устройство производит не только их коррекцию, 40 .яо и формирует сигнал ошибки с инди@ецией неисправности. При появле540 1 нии однократной ошибки на одном из трех входов одного мажоритарного элемента 6 сигнал отличается от сигналов на двух других входах этого же мажоритарного элемента (возникает неравнозначность ). Поскольку входы мажоритарных элементов 6 соединены с соответствующими входами блоков 8 сравнения, на выходе одного из блоков 8 сравнения присутствует сигнал

И II неравноэначности (логический 0 }.

Следовательно, на выходе элемента

И 9 также логический "0", который поступает на вход триггера 10, и с приходом импульса от блока 2 на другой вход триггера 10 в него записывается сигнал ошибки, который направ" ляется на выход устройства в виде ло гического "0". Одновременно загорается светодиод в элементе ll индикации.

При нажатии кнопки 21 сброса в блоке 2 управления триггер 10 устанавливается в исходное состояние, сигнал ошибки снимается.

Предлагаемое устройство обнару" живает не только все однократные и двукратные ошибки, но и часть ошибок более высокой кратности. Таким образом, оно обеспечивает ие только исправление однократных ошибок, но и сигнализирует о наличии однократч яых и двукратных ошибок, появившихся в любых разрядах блоков памяти или в сумматорах. Кроме того, предлагаемое устройство обеспечивает обнаружение и исправление части ошибок бЬлее высокой кратности.

1137540 1137540 н 1и4

n 10

Фиг. 2

f)37540

Составитель В.Рудаков

Техред С.йовжий

Редактор Л.Алексеенко

Корректор С.Черни

Подписное

Филиал ПИП "Патент", r.Óærîðîä, ул.Проектная, Заказ I0534/40 Тираж 583

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

133035, Москва, Ж-35, Раушская наб., д. 4/5