Параллельный пирамидальный счетчик-дешифратор количества единиц в @ -разрядном двоичном коде

Иллюстрации

Показать всеРеферат

ПАРАЛЛЕЛЬНЫЙ ПИРАМИДАЛЬНЫЙ СЧЕТВДК-ДЕШИФРАТОР КОЛИЧЕСТВА ЕДИНВД Б п-РАЗРЯДНОМ ДВОИЧНОМ КОДЕ по авт. св. № 892715, отличающийся тем, что, с целью расширения функциональных возможностей, в нето в первом ярусе введены два элемента И, первые входы которых подключены соответственно к нулевому и единичному входам первого яруса, вторые входы - к первой управляющей шине, а выходы соединены с выходами первого яруса, в каждый К-и ярус дополнительно введены элемент:; lUlIi и К элементов И, первые входы которых подключены к второй управляющей шине, а вторые входы - к соответствующим выходам (к -1)-го яруса,при этом выход первого из К г лементов И соединен с входом соответствующего дополнительного элемента ИЛИ, другой вход которого соединен с третьей управляющей щиной, а выход дополнительного элемента ШШ и остальных из К элементов И подключены соответственно к объединенным второму и первому i входам соответствующих нечетного и -четного элементов И К -го яруса, кроСЛ ме того, в каждый ярус введен шифратор , вход которого подключен к выходам этого яруса, а выходы всех шифраторов подключены к дополнительной выходной шине.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧ ЕСНИХ

РЕСГ1УБЛИН

4(51) Н 03 M 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТНЕННЦЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬГГИЙ (46) 07.02 ° 85. Бюл. № 5 (61) 8927)5 (21) 3653760/24-21 (22) 17.10,83 (72) В.П.Гондарев, И.Н.Федоренко и В.С.Мнрнода (71) Таганрогский радиотехнический институт им. В.Д.Калмьпсова (53) 681.188(088.8) (56) 1. Авторское свидетельство СССР № 892715, кл. H 03 К 13/24, 30.04.80. (54) (57) ПАРАЛЛЕЛЬНЫЙ ПИРАМИДАЛЬНЫЙ

СЧЕТЧИК-ДЕШИФРАТОР КОЛИЧЕСТВА ЕДИНИЦ В и-РАЗРЯДНОМ ДВОИЧНОМ КОДЕ по авт. св. № 892715, о т л и ч а юшийся тем, что, с целью расширения функциональных возможностей, в него в первом ярусе введены два элемента И, первые входы которых подключены соответственно к нулевому и единичному входам первого яруса, вторые входы — к первой управляющей

„„Я0.„1138935 А шине, а выходы соединены с выходами первого яруса, в каждый К -й ярус дополнительно введены элемент; ИЛИ и k элементов И, первые входы которых подключены к второй управляющей шине, а вторые входы — к соответствующим выходам (K -1) -го яруса,при этом выход первого из К "-.лементов И соединен с входом соответствующего дополнительного элемента ИЛИ, другой вход которого соединен с третьей управляющей шиной, а выход дополнительного элемента ИЛИ и остальных иэ К элементов И подключены соответственно к объединенным второму и первому входам соответствующих нечетного и Pg .четного элементов И К -го яруса, кроме того, в ншедий ярус введен шифра- Щ тор, вход которого подключен к выходам этого яруса, а выходы всех шифраторов подключены к дополнительной выходной шине.

1138935

Изобретение относится к импульсной технике и предназначено для параллельного подсчета — дешифрации количества единиц в двоичном коде, число разрядов которого равно 5

По основному авт. св. 11 892715 из- . вестен параллельный пирамидальный счетчик-дешифратор. количества единиц в и --разрядном двоичном коде, содержащий в первом, втором, третьем,..., 1P n-м ярусах соответственно 0,4,6,..., 2 двухвходовых элементов И, причем в каждом k -м ярусе первые .входы нечетных и вторые входы четных элемен тов И подключены соответственно к 15 нулевому и единичному входам этого яруса, второй и первый входы соответственно нечетного и следующего за ним четного элементов И объединены и подключены к соответствующим выходам,20 (k-1)-ro яруса, выходы первого и К -го элементов И k-го яруса соединены соответственно с его первым и К-м выходами, а выходы четного и следующего за ним нечетного элементов И под- 25 ключены к входам соответствующего элемента ИЛИ, выход которого соединен с соответствующим выходом этого

I яруса, при этом все выходы каждого яруса соединены с выходной шиной fl),gp

Недостатками известного устройства являются его неприспособленность для подсчета — дешифрации количества единиц в отдельных группах разрякода или в нескольких п.-разрядных двоичных кодах, а также невозможность непосредствен" ной выдачи выходного сигнала в форме, удобной для обработки в ЭВМ, что обусловливает недостаточные функцио- 4О нальные возможности этого устройства.

Цель изобретения — расширение функциональных возможностей.

Цель достигается тем, что в параллельный пирамидальный счетчик — 45 дешифратор количества единиц в и-разрядном двоичном коде в первом ярусе введены два элемента И, первые входы которых подключены соответственно к нулевому и единичному входам первого яруса, вторые входы — к первой управ,ляющей шине, а выходы соединены с выходами первого яруса, в каждый К-й ярус дополнительно введены элемент

ИЛИ и К элементов И, первые входы которых подключены к второй управляющей шине, а вторые входы — к соот. ветствующим выходам (K-1)-ro яруса, при этом выход первого из k элементов И соединен с входом соответствующего дополнительного элемента ИЛИ, другой вход которого соединен с третьей управляющей шиной, а выходы дополнительного элемента ИЛИ и остальных из К элементов И подключены соответственно к объединенным второму и первому входам соответствующих нечетного и четного элементов И К -го яруса, кроме того, в каждый ярус введен шифратор, вход которого подключен к выходам этого яруса, а выходы всех шифраторов подключены к дополнитель1 ной выходной шине.

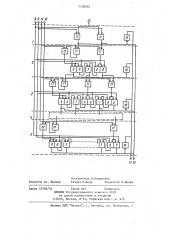

На чертеже приведена схема параллельного пирамидального счетчикадешифратора количества единиц в и-разрядном двоичном коде для случая

1 = 5.

Счетчик-дешифратор состоит из ярусов 1-5, которые содержат соответственно 0,2 2, 2.3, 2-4, 2 5 двухBxopoBbIx ýëåìåíòoâ И 6 и двухвходовых элементов ИЛИ 7 (количество элементов в каждом ярусе, начиная со .. второго, вдвое больше порядкового номера яруса ), причем первый и второй входы, соответственно нечетного и следующего за ним четного элементов И 6 какого-либо яруса 2-5, кроме первого, подключены соответственно к единичному 8 и нулевому 9 входам этого яруса, выходы первого и последнего элементов И 6 в какомлибо ярусе 2-5 соединены с соответственно первым и последним выходами этого яруса, а выходы четного и следующего за ним нечетного элементов

И 6 подключены к входам соответствующего элемента ИЛИ 7, выход которого соединен с соответствующим выходом этого яруса. Все выходы каждого яруса 1-5 подключены к выходной шине 10.

Кроме того, первый ярус 1 содержит два дополнительных элемента И 11, а каждый k -й ярус содержит дополнитель .но k элементов И 11 и элемент ИЛИ 12.

Первые входы элементов И 11 первого яруса 1 подключены соответственно к нулевому и единичному входам 9 и 8 первого яруса 1, вторые входы элементов И 11 соединены с первой управляющей шиной 13, а выходы — с выходами первого яруса 1. В каждом из остальных ярусов 2-5 первые входы дополнительных элементов И ll подключены к

935 з 1138 второй управляющей шине 14, а вторые их входы — к соответствующим выходам предыдущего яруса, Один вход дополнительного элемента ИЛИ 12 подключен к третьей управляющей шине 15, другой вход — к выходу первого и дополнительных элементов И 11 этого яруса, а выходы элемента ИЛИ 12 и остальных дополнительных элементов И ll соединены с объединенными входами соот- !О ветствующих нечетного и следующего за ним четного элементов И 6 этого же яруса. Кроме того, каждый ярус

1-5 содержит шифратор 16, подключенный своими входами к выходам этого 15 яруса; выходы всех шифраторов соединены с дополнительной выходной шиной 17.

Входы 8 и 9, выходные шины 10 и

17, вторая и третья управляющие ши= 2о ны 14 и !5 содержат каждая по h проводов, каждый из которых подведен к одному из ярусов. Шифратор 16 служит для преобразования сигналов с вы. ходов ярусов в удобную для ЭВМ форму 25

Устройство работает следующим образом.

Управляющий сигнал с шины 13 поступает на элементы И 11 первого яру са 1. С входов 8 и 9 коды поступают на элементы И 11 первого яруса и элементы И 6 остальных ярусов 2-5.При наличии разрешающего сигнала на шине

14 и запрещающего сигнала на шине 15 всех ярусов результаты подсчета с предыдущего яруса поступают в последующий и на шину 10 непосредственно и через шифратор 16 " на дополнительную шину 17. На выходах каждого К -го яруса будут результаты подсчетов предыдущих К разрядов. При наличии запрещающего сигнала с шины 14 на элементах И ll K -го яруса и разре ; шающего сигнала с шины 15 на элемен тах ИЛИ 12 К -го яруса, а в других ярусах на элементах И ll — разрешающего и на элементах ИЛИ 12 — запрещающего, подсчет в (k-l) ярусах осуществляется как описано выше, с K-го яруса подсчет начинается заново и К-й ярус будет работать как первый, (K+1) -й — как второй и т.д. Так, меняя управление на шинах 14 и 15,можно подключить по входам 8 и 9 входную информацию от разных источников.

Использование дополнительных элементов И, ИЛИ и шифраторов позволяет

I применять параллельный пирамидальный счетчик-дешифратор количества единиц в и -разрядном коде для подсчета единиц в нескольких кодовых комбинациях, содержащих меньшее чем ь число разрядов и получать выходной сигнал в форме, удобной для обработки в 3ВМ.

Преимущества предлагаемого устройства позволяют использовать его в качестве вероятностного коммутатора при решении широкого класса задач обработки информации.

1138935

Составитель О.Ревинский

Техред О.Неце. Корректор О,Билак

Редактор Аг. Шандор

Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., 4/5

Заказ 10705/44

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4