Устройство для вычисления квадратного корня

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ, содержащее счетчик циклов и сумматор, отличающееся тем, что, с целью сокращения аппаратурных затрат, устройство содержит регистр сдвига и регистр результата, содержащий п триггеров (гдеП- разрядность регистра ) , информационные входы триггеров регистра результата соединены с выходом переноса сумматора, тактовый вход 4-го триггера регистра результата

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (! 1) 4(51) С 06 F 52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABT0PCHOIVlV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3644704/24-24 (22) 27.09.83 (46) 15. 02.85. Бюл. 11 6 (72) А.N.Êîñîëàïîâ и В.С.Мелентьев (7.1) Куйбышевский ордена Трудового

Красного Знамени политехнический институт нм. В.В.Куйбышева (532 681.325(088.8) (56) 1. Авторское свидетельство СССР

Ф 239665, кл. С 06 F 7/552, 1969.

2. Авторское свидетельство СССР

К 877529, кл. С 06 F 7/552, 1979 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ ВЪИИСЛЕНИЯ

КВАДРАТНОГО КОРНЯ, содержащее счетчик циклов и сумматор, о т л и— чающее с я тем, что, с целью сокращения аппаратурных затрат, устройство содержит регистр сдвига и регистр результата, содержащий tl триггеров (rpe rl — разрядность регистра), информационные входы триггеров регистра результата соединены с выходом переноса сумматора, тактовый вход 4-го триггера регистра результата (j = З,n ) соединен с входом установки нуля (< -2)-го триггера регистI ра результата и выходом < -ro разряда счетчика циклов, тактовые входы первого и второго триггеров регистра результата соединены с выходами соответственно первого и второго раз- . рядов счетчика циклов, выход (0+1)го разряда которого соединен с входами установки нуля (q-1)-го и 11-го триггеров регистра результата, выходы триггеров регистра результата соединены соответственно с разрядными входами первого слагаемого суммато- ч> ра (11+1)-й разрядный вход первого слагаемого которого соединен с шиной логической единицы устройства, разрядные входы второго слагаемого соединены соответственно с разрядными выходами регистра сдвига, разрядные входы которого соединены с выходами разрядов сумматора.

1 11401

Изобретение относится к вычислительной технике и может быть применено для аппаратурной реализации операции вычисления квадратного корня.

Известно устройство для вычисления корня, содержащее счетчик циклов, дешифратор со схемами объединения на выходе, два регистра сдвига и параллельный сумматор, причем выходы счетчика циклов подключены к входам дешифратора, выходы которого через схемы объединения подсоединены к соответствующим разрядам регистра, выходы которого соединены с входами сумматора, выход триггера знакового разряда сумматора соединен с входом дешифратора.

Наиболее близким к предлагаемому является устройство для вычисления квадратного корня, содержащее счетчик циклов, дешифратор и коммутатор, выход которого соединен с информационными входами сумматора, выход знакового разряда которого соединен с первым входом блока управления, первый выход которого подключен к управляющему входу коммутатора, а второй выход блока управления является выходом результата устройства, первый и второй входы синхронизации устройства, соединены с входом счетчика циклов и входом управления сумматора и являются одновременно вторым и третьим входами блока управления.

Недостатком известных устройств. являются значительные аппаратурные затраты.

Цель изобретения — сокращение аппаратурных затрат.

Поставленная цель достигается тем,40 что устройство для вычисления квадрат- ного корня, содержащее счетчик циклов и сумматор, содержит регистр сдвига и регистр результата, содер-. жащий П триггеров (где П вЂ” разряд- 4> ность регистра), информационные входы триггеров регистра результата соединены с выкодом переноса сумматора, тактовый вход s --го триггера регистра результата (< - =З,П ) соединен с входом установки -нуля (< -2)-го триг гера регистра результата и с выхо1 дом -го разряда счетчика циклов, тактовые входы первого и второго триггеров регистра результата соеди- 55 нены с выходами соответственно первого и второго, разрядов счетчика циклов, выход (П+1)-ro разряда которого

18 2 соединен с входами установки нуля (П-1)-ro u q-ro триггеров регистра результата, выходы триггеров регистра результата соединены соответственно с разрядными входами первого сгагаемого сумматора, (й+1)-й разрядный вход первого слагаемого которсго соединей с шиной логической единицы устройства, разрядные входы второго слагаемого сумматора соединены соответственно с разрядными выходами регистра сдвига, разрядные входы которого соединены с выходами разрядов сумматора.

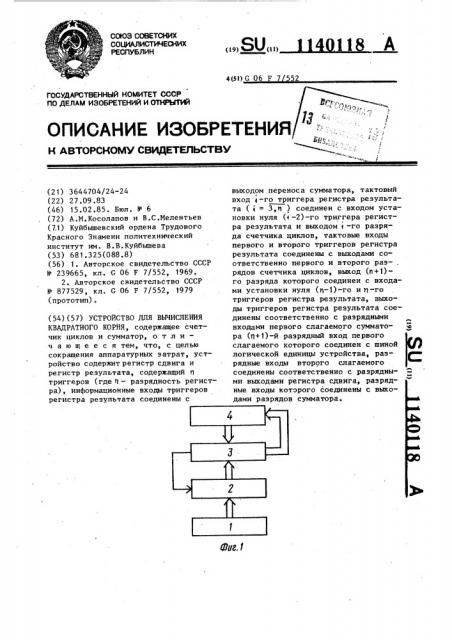

На фиг. 1 представлена блок-схема устройства для вычисления квадратногс корня,,на фиг. 2 — схема регистра.

Устройство (фиг. 1) содержит счетчик 1 циклов, регистр 2 результата, сумматор 3 и регистр 4 сдвига.

Регистр 2 (фиг. 2) содержит триггеры 5, вход б установки нуля и ин-. формационный вход 7.

Для вычисления квадратного корня из числа, содержащего П двоичных разрядов, с П -разрядной точностью кольцевой счетчик 1 циклов, регистр

2, сумматор 3 и регистр 4 сдвига должны иметь по (П+1) разрядов.

Вычисление квадратного корня осуществляется следующим образом.

Подкоренное выражение заносится в регистр 4 сдвига.

В исходном состоянии в старшем (левом) разряде (П+1) кольцевого счетчика 1 циклов записана единица, а в старшем разряде (П+1) регистра

4 сдвига — ноль.

Единица из разряда (П+1) счетчика 1 переписывается в (П+t)-е разряды регистра 2, а в остальных разрядах регистра 2 записаны нули, кроме старшего (левого) разряда (и+1), в котором всегда записана единица.

Сначала вычисляют квадратный корень из старших двух цифр подкоренного выражения. Для этого с помощью сумматора 3 производится сложение содержимого регистра 2 и содержимого регистра сдвига 4. Если на выходе сумматора 3 образуется сигнал переноса (единица), то первая цифра корня равна единице, если сигнала переноса нет,то она равна нулю.

Для получения второй цифры корня производится сдвиг кольцевого счетчика циклов I на один разряд впра-во. При этом первая цифра корня за3 1140 носится в обратном коде в и -й разряд регистра 2, а единица из !1-го разряда счетчика 1 переписывается в (!1-2)-й разряд регистра 2. Если первая цифра корня — единица, то в сумматоре 3 сформирован остаток, который переписывается в регистр 4 сдвига, если цифра корня — ноль, подкоренное выражение, записанное в регистре 4, остается без изменения. !0

Затем производится сдвиг регистра 4 на один разряд влево.

Далее процесс вычисления выполняется как и для первой цифры корня.

После получения второй цифры корня производится сдвиг кольцевого счетчика 1 циклов на один разряд вправо.

В (0-1).-й разряд регистра 2 записывается вторая цифра корня. Единица из (П-1)-ro разряда счетчика 1 пере- 20 писывается в (Vl-3) -й разряд регистра 2. Затем производится сдвиг регистра 4 на один разряд влево и определяется третья цифра корня.

После выполнения !1 циклов в реги.стре 2 будет записан результат вычисления квадратного корня в обратном коде.

Пример вычисления квадратного корня из числа О, 101010

Исходное состояние кольцевого счетчика 1 циклов; 1000000.

1-й цикл 0+1 !! И -1 и-2 и-3 и-4 и-5

Регистр 4: О 1 О 1 О 1 О

Регистр 2: . 1 1 1 О О 0 О

Сумматор 3: О О 1 1 О 1 О

На выходе переноса сумматора 3 единица. После выполнения суммирования содержимых регистров 4 и 2 произ-40 водится сдвиг кольцевого счетчика циклов на один разряд вправо. При этом формируется код: 0100000. Остаток из сумматора 3 переписывается в регистр сдвига 4. После этого произ- 45 водится сдвиг регистра 4.

2-й цикл

Регистр 4: О 1 1 О 1 0 О

Регистр 2: 1 О 1 1 О О О уе

Сумматор 3: О О О 1 1 О О

На выходе переноса сумматора 3 единица. После суммирования произво18 4 дится сдвиг счетчика 1. При этом формируется код: 0010000.

Остаток из сумматора 3 переписывается в регистр 4 сдвига. После этого производится сдвиг регистра 4.

3-й цикл.

Регистр 4: О О 1 1 О О О

Регистр 2: 1 О 0 1 1 О О

Сумматор 3: 1 100 100

На выходе переноса сумматора 3 ноль. После суммирования производится сдвиг счетчика 1. При этом формируется код: 0001000. Содержимое регистра сдвига 4 не изменяется. После этого производится сдвиг регистра 4.

4-й цикл.

Регистр 4: О 1 1 О О О 0

Регистр 2: 1 0 О 1 1 1 О

Сумматор 3: 1 1 1 1 1 1 0

На выходе переноса сумматора 3 ноль.. После суммирования производится сдвиг счетчика 1. При этом формируется код: 0000100. Поеле этого производится сдвиг регистра 4.

5-й цикл.

Регистр 4: 1 1 О О 0 О О

Регистр 2: 1 О О 1 1 1 1

Сумматор 3: О 1 О 1 1 1 1

На выходе переноса сумматора 3 единица. После суммирования производится сдвиг счетчика:1. При этом формируется код: 0000010. Остаток Hs сумматора 3 переписывается в регистр сдвига 4. После этого производится сдвиг регистра 4.

6-й цикл.

Регистр 4: 1 0 1 1 1 1 О

Регистр 2: 1 О О 1 1 О 1

Сумматор3: 010 10 1

На выходе переноса сумматора 3 единица. После суммирования производится сдвиг счетчика 1 ° При -этом формируется код: 0000001.

Для вычисления квадратного корня ,"из числа, содержащего двоичные pasряды, с !! -paspapHnA точностью требуется П циклов.

В предлагаемом устройстве сокращены аппаратурные затраты.

1140118

g+f и и+1 и

Составитель А. Казанский

Редактор Л.Пчелинская Техред А.Бабинец Корректор А.Зимокосов

Заказ 265/38 Тираж 7 lO . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий .

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППН "Патент", г. Ужгород, ул. Проектная, 4