Запоминающее устройство /его варианты/

Иллюстрации

Показать всеРеферат

1. Запоминакяцее устройство, содержащее блок памяти и выходной регистр , информационные входы которого соединены с соответствукнцими выходами блока памяти, выходы выходного регистра являются информационными выходами устройства, а управляющий вход выходного регистра является управляющим входом устройства, о тличающееся тем, что, с целью повышения информационной емкости устройства, в него введены генераторы кода 1 и триггер, причем выход генератора кода 1 соединен с установочным входом триггера, управляю1ций вход которого соединен с управляющим входом выходного регистра . 2. Запоминающее устройство, содержащее блок памяти и выходной регистр; информационные входы которого соединены с соответствующими выходами блока памяти, выходы выходного регистра являются информационными выходами устройства, а управляющий вход выходного регистра является управляющим входом устройства, отличающееся тем, что, с целью повышения информационной емкости устрой (Л ства, в него введены инвертор и тригс гер, причем вход инвертора соединен с входом старшего разряда выходного а регистра, вЬкод инвертора соединен с установочным входом триггера, управляющий вход которого соединен с управляющим входом выходного регистра .

СОЮЗ СОВЕТСКИХ

tNUNI

РЕСПУБЛИК

4(51) G 11 С 11 00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ COOP

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТЖ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ll 481DPCNOMV CàÈÌòèëüñ é

I >. (21) 3359576/18-24 (22) 04.12.81 (46) 15.02.85. Бюл. Ф 6 (72) В.А. Тур (53) 681.327.6(088.8) (56) 1. Авторское свидетельство СССР

У, 739646, кл. G 11 С 11/00, 1979.

2. Архитектура СМ-1 — техническая документация на ЭВМ СМ-1 (прототип). (54) ЗАПОМИНА10ЩЕЕ УСТРОЙСТВО (ЕГО

ВАРИАНТЫ) . (57) 1. Запоминающее устройство, содержащее блок памяти и выходной регистр, информационные входы которого соединены с соответствующими выходами блОка памяти ВыхОДы ВыходнОГО регистра являются информационными выходами устройства, а управляющий вход выходного регистра является управляющим входом устройства, о тл и ч а ю щ е е с я тем, что, с целью повышения информационной емкости устройства, в него введены,SU„„1140167 А генераторы кода "1" и триггер, причем выход генератора кода "1" соеди- нен с установочным входом триггера, управляющий вход которого соединен с управляющим входом выходного регистра.

2. Запоминающее устройство, содержащее блок памяти и выходной регистр, информационные входы которого соединены с соответствующими выходами блока памяти, выходы выходного регистра являются информационными выходами устройства, а управляющий вход выходного регистра является управляющим входом устройства, о т л и ч аю щ е е с я тем, что, с целью повы- Я шения информационной емкости устройства, в него введены инвертор и триггер, причем вход инвертора соединен ( с входом старшего разряда выходного регистра, вйход инвертора соединен Я с установочным входом триггера, управляющий вход которого соединен О с управляющим входом выходного ре- М гистра, 1140167

Изобретение относится к вычислительной технике, конкретно к вычислительным машинам с двоичным представлением информации.

Известно запоминающее устройство, 5 содержащее накопитель, схемы И, дешифратор, формирователь адреса, коммутатор адреса и коммутатор ошибки $1) °

Наиболее близким к изобретению по технической сущности является устройство 1 2 .

Цель изобретения — повышение информационной емкости устройства.

Цель достигается тем, что в запо15 минающее устройство, содержащее.. блок памяти и выходной .регистр, информационные входы которого соединены с соответствующими выходами блока памяти, выходы выходного регистра

20 являются информационными выходами устройства, а управляющий вход выходного регистра является управляющим входом устройства, дополнительно введены генератор кода "1" и триггер, причем выход генератора кода "1" соединен с установочным входом триггера, управляющий вход которого соединен с управляющим входом выходного регистра.

Согласно второму варианту в запоминающее устройство, содержащее блок памяти и выходной регистр, информационные входы которого соединены с соответствующими выходами бло- Ы ка памяти, выходы выходного регистра являются информационными выходами устройства, а управляющий вход выходного регистра является управляющим входом устройства, дополнитель- 4О но введены инвертор и триггер, причем вход инвертора соединен с входом старшего разряда выходного регистра, выход инвертора соединен с установочным входом триггера, управляющий вход4 которого соединен с управляющим входом выходного регистра.

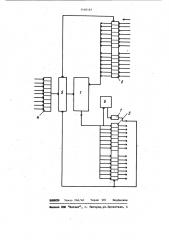

На чертеже представлена схема предлагаемого устройства.

Запоминающее устройство, выполненное согласно первому варианту, содержит блок 1 памяти, регистр 2 приема числа, выходной регистр 3, регистр 4 адреса, блок 5 управления, генератор 6 кода "1", триггер 7.

Согласно второму варианту устройство содержит блок 1 памяти, регистр

2 приема числа, выходной регистр 3, регистр 4 адреса, блок 5 управления, инвертор 6 и триггер 7.

Предлагаемое запоминающее устройство работает следующим образом.

Информация иэ регистра 2 приема . (без информации о старшем разряде мантиссы) поступает в блок 1 памяти по адресу, содержащемуся в регистре 4 адреса. При считывании иэ блока памяти по указанному в регистре

4 адресу информация поступает в регистр 3 выдачи числа, а генератор кода "1" или инвентор 6 по содержимому знакового разряда регистра выдачи, к входу которого он подключен, восстанавливает информацию о.старшем разряде мантиссы и заносит по сигналу триггера 7 в регистр 4.

За счет разгрузки устройства от необходимости хранить зависимую от состояния других ячеек информацию появляется возможность сохранить информацию еще об одном младшем разряде мантиссы, что обуславливает повышение информативной емкости, Использование изобретения, например, в вычислительной технике, позволит в блоке памяти той же разрядности хранить числа вдвое большей точности, что значительно повысит эффективность использования устройства, особенно в классе мини- и микро-ЭВМ, где разрядность ячеек памяти невелика.

»4Oi6S

ВНИИПИ Заказ 266/40 Тираж 584 Подписное

Филиал ППП "Патент", г. Ужгород,ул.Проектная, 4