Усилитель-формирователь выходных сигналов постоянных запоминающих устройств на моп-транзисторах

Иллюстрации

Показать всеРеферат

УСИЛИТЕЛЬ-ФОРМИ{ ОВАТЕЛЬ ВЫХОДНЫХ СИГНАЛОВ ПОСТОЯННЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ НА МОП-ТРАНЗИСТОРАХ , содержащий триггер, первый выход которого соединен с входом первого инвертора, второй выход - с входом второго инвертора, ключевой транзистор, включенньм между точкой соединения истоков ключевых транзисторов триггера и общей шиной устройства , затвор ключевого транзистора соединен с шиной тактового сигнала , выходной усилительный каскад, прямую и инверсную шины ввода данных , отличающийся тем, что, с целью повышения быстродействия , в него введены третий инвертор , нагрузочный транзистор, первый и второй переключающие транзисторы, первый и второй парафазные усилительные каскады, причем первый вход первого парафазного усилительного каскада соединен с входом первого инвертора , а второй вход - с выходом этого инвертора5 первый вход второго парафазного усилительного каскада соединен с входом второго инвертора , а второй вход - с выходом этого инвертора, причем выходы первого и второго парафазных усилительных каскадов соединены соответственно с первым и вторым входами выходного усилительного каскада, а нагрузочные транзисторы триггера соединены через (/) нагрузочньй транзистор с шиной питания , первый выход триггера через первый переключающий трназистор соединен с инверсной шиной ввода данных , а второй выход через второй переключающий транзистор - с прямой шиной ввода данных, при этом затворы 4 первого и второго переключающих транзисторов соединены с выходом третьего инвертора, вход которого соединен с шиной тактового сигнала. СП

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

4(5!) Н 03 К 19 08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ ./ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3586017/24-21 (22) 27.04.83 (46) 15.02.85. Бюл. ¹- 6 (72) А.Г. Солод, А.H. Копытов и С.В. Высочина (53) 621.374(088.8) (56) 1. Патент США № 4280065, кл. 307-473, 21,07.8 1.

2. "Электротехника", 1978, ¹ 7, т. 51, с. 36, рис. 5 (прототип). (54) (57) УСИЛИТЕЛЬ-ФОРМИРОВАТЕЛЬ BblХОДНЫХ СИГНАЛОВ ПОСТОЯННЫХ ЗАПОМИНА10ЩИХ УСТРОЙСТВ НА ИОП-ТРАНЗИСТОРАХ, содержащий триггер, первый выход которого соединен с входом первого инвертора, второй выход — с входом второго инвертора, ключевой транзистор, включенный между точкой соединения истоков ключевых транзисторов триггера и общей шиной устройства, затвор ключевого транзистора соединен с шиной тактового сигнала, выходной усилительный каскад, прямую и инверсную шины ввода данных, отличающийся тем, что, с целью повышения быстродействия, в него введены третий инвер„„SU „„И 40245 А тор, нагрузочный транзистор, первый и второй переключающие транзисторы, первый и второй парафазные усилитель" ные каскады, причем первый вход первого парафазного усилительного каскада соединен с входом первого инвертора, а второй вход — с выходом этого инвертора, первый вход второго парафазного усилительного каскада соединен с входом второго инвертора, а второй вход — с выходом этого инвертора, причем выходы первого и второго парафазных усилительных каскадов соединены соответственно с первым и вторым входами выходного усилительного каскада, а нагрузочные транзисторы триггера соединены через нагрузочный транзистор с шиной питания, первый выход триггера через первый переключающий трназистор соединен с инверсной шиной ввода данных,,а второй выход через второй переключающий транзистор — с прямой шиной ввода данных, при этом затворы первого и второго переключающих транзисторов соединены с выходом третьего инвертора, вход которого соединен с шиной тактового сигнала. ф

1 1140

Изобретение относится к импульсной технике и может быть использовано, например, в качестве выходного усилителя постоянных запоминающих уст.ройств.

Известен формирователь выходных сигналов, содержащий первый элемент

И-НЕ, второй элемент И-НЕ, выход которого соединен с входом инвертора, выход которого соединен с входом вы- 10 ходного каскада (1, Недостатками устройства являются ограниченность функциональных возможностей и сложность изготовления.

Наиболее близким к предлагаемому является усилитель-формирователь выходных сигналов постоянных запоминаю- щих устройств на ИОП-транзисторах, содержащий триггер, первый выход которого соединен с входом первого ин- gp вертора, второй выход — с входом второго инвертора, ключевой транзистор, включейный между точкой соединения истоков ключевых транзисторов триггера и общей шиной устройства, à затвор25 ключевого транзистора соединен с шиной тактового сигнала, выходной усилительный каскад, прямую и инверсную шины ввода данных (21 .

Недостатком данного устройства яв-Зр ляется низкое быстродействие.

Цель изобретения — повышение быстродействия.

Поставленная цель достигается тем, что в усилитель-формирователь выходных сигналов постоянных запоминающих устройств на ИОП-транзисторах, содержащий триггер, первый выход которого соединен с входом первого инвертора, второй выход — с входом второго ин- 40 вертора, ключевой транзистор, включенный между точкой соединения истоков ключевых транзисторов триггера и общей шиной устройства, а затвор . ключевого транзистора соединен с 45 шиной тактового сигнала, выходной усилительный каскад, прямую и инверсную шины ввода данных, введены третий инвертор, нагрузочный транзистор, первый и второй переключающие тран- 50 зисторы, первый и второй парафазные ,усилительные каскады, причем первый вход первого парафазного усилительного каскада соединен с входом первого инвертора, а второй вход " с 55 выходом этого инвертора, первый вход второго парафазного усилительного каскада соединен с входом второго ин245 вертора, а второй вход — с выходом ° этого инвертора, причем выходы первого и второго парафазных усилительных каскадов соединены соответственно с первым и вторым входами выходного усилительного каскада, а нагрузочные транзисторы триггера соединены через нагрузочный транзистор с шиной питания, первый выход триггера через первый переключающий транзистор соединен с инверсной шиной ввода данных, а второй выход через второй переключающий транзистор — с прямой шиной ввода данных, при этом затворы первого и второго переключающих транзисторов соединены с выходом третьего инвертора, вход которого соединен с шиной тактового сигнала. !

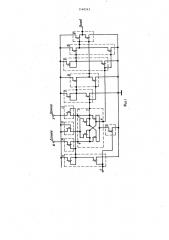

На фиг. 1 приведена принципиальная электрическая схема устройства; на фиг. 2 — эпюры, поясняющие работу устройства.

Устройство содержит триггер 1, первый выход 2 которого соединен с

1 входом первого инвертора 3, второй выход 4 — с входом второго инвертора 5, ключевой транзистор 6, включенный между истоками ключевых транзисторов триггера 1 и общей шиной устройства, а затвор ключевого тран- . зистора соединен с шиной 7 тактового сигнала, выходной усилительный каскад

8, инверсную и прямую шины 9 и 10 ввода данных, третий инвертор 11,нагрузочный транзистор 12, первый и второй переключающие транзисторы 13 и 14, первый и второй парафазные усилительные каскады 15 и 16, причем первый вход первого парафазного усилительного каскада 15 соединен с входом первого инвертора 3, а второй вход - с выходом этого инвертора, первый вмод второго парафазного усилительного каскада соединен с входом второго инвертора 5, а второй вход — с выходом этого инвертора, причем выходы первого и второго парафазных усилительных каскадов соединены соответственно с первым и вторым входами выходного усилительного каскада, а нагрузочные транзисторы триггера соединены через нагрузочный транзистор 12 с шиной питания, первый выход триггера 1 через первый переключающий транзистор 13 соединен с инверсной шиной 9 ввода данных, а второй выход через второй переключающий транзистор - с прямой

3 11402 шиной 10 ввода данных, при этом затворы первого и второго переключающих транзисторов 13 и 14 соединены с выходом третьего инвертора 11, вход которого соединен с шиной тактового сигнала.

Устройство работает следующим образом.

В исходном состоянии с выхода дифференциального каскада на вход уснли- 1О теля-формирователя выходных сигналов

ПЗУ на МОП-транзисторах-(фиг. 1) поступают входные сигналы "Данное" (шина 9, фиг. 2б) и "Данное" (шина

10, фиг. 2а) в виде положительного потенциала. При этом на вход шины 7 тактового сигнала (фиг. 2в) также . цоступает положительный потенциал. При этом инвертор 11 открыт и на затворах переключающих транзисторов 2б, 13 и 14 (фиг. 2 г д) устанавливается нулевой потенциал, транзисторы закрыты и входные сигналы "Данное" и

"Данное" не поступают на вход усилителя.Ключевой транзистор 6 при этом открыт и истоки ключевых транзисторов триггера 1 подсоединены к общей шине.

Считывание информации с шин 9 "Данное" и 10 "Данное" на выходы 2 и 4 триггера 1 начинается с гого момента, когда на шине 7 тактового сигна- ла устанавливается нулевой потенциал (момент времени 11 на фиг. 2).

Допустим, на шине 9 сигнал уменьшается, а на шине 10 — увеличивается.

Транзистор 6 закрыт. Истоки ключевых транзисторов триггера 1 отсоединены от общеу шины. На обоих выходах 2 и 4 триггера 1 устанавливается положительный потенциал, кото- 4О рый устанавливается на выходах инверторов 3 и 5(фиг. 2е, з) и на выходах парафазных каскадов 15 и 16 . (фиг. 2ж,и) нулевой потенциал. Ha . выходе выходного каскада 8 сохраня- 4 ется предыдущее состояние. При этом на выходе инвертора 11 устанавливается положительный потенциа „ который открывает переключающие транзисторы 13 и 14, и информация с шин

"Данное" 9 и "Данное" 10 передается на выходы триггера 1. На выходе 2 положительный потенциал уменьшается, а на выходе 4 — увеличивается. При

45 4 поступлении следующего положительного тактового сигнала.с шины 7 (момент времени 1Z "à фиг. 2) транзистор 6 открывается, а на выходе инвертора 11 устанавливается нулевой потенциал, который закрывает переключащие тран-. зисторы 13 и 14, отсоединяя шины "Дан" ное" 9 и "Данное" 10 от выходов 2 и

4 триггера 1, уменьшая тем самым паразитную емкость нагрузки триггера. Через открытый транзистор 6 истоки ключевых транзисторов триггера 1 подсоединяются к общей шине, что вызывает понижение положительного потенциала на выходе 2 до величины напряжения запирания инвертора 3 и парафазного каскада 15. На выйоде 4 триггера 1 при этом положительный потенциал увеличивается, вызывая еще большее отпирание инвертора 5 и парафазного каскада 16. На выходе (фиг.2и) парафазного каскада 16 устанавливается .нулевой потенциал, а на выходе (фиг. 2ж) парафазного каскада 15 — положительный потенци- ал, который вызывает отпирание выходного каскада 8 и на его выходе (фиг. 2к) устанавливается нулевой потенциал. Работа схемы при изменении.полярности входного сигнала

"Данное" и "Данное" ничем не отличается от предыдущего случая за исключением того, что при поступлении положительного тактового сигнала положительный потенциал устанавливается на выходе парафазного .каскада 16, а нулевой — на .выходе парафазного каскада 15 и на выходе усилителя-формирователя устанавлива- . ется положительный потенциал..

При размещении выходнь|х усилителей-формирователей ПЗУ на кристалле при современных его размерахЖ бх6 мм паразитная емкость соединительных шин выхода дифференциального каскада и входа усилителя-формирователя составляет примерно d пФ, в то время как собственная паразитная емкость выходов триггера выходного каскада составляет 0,16 пФ. Таким образом, отключение соединительных шин в момент переключения триггера с помощью дополнительного инвертора позволяет уменьшить время переключения в 7 раз.

1140245 ф

1140245

8(а) 1(е)

/ й(к) Составитель А. Горбачев

Техред М.Гергель Корректор О. Луговая

Редактор Г1. Петрова тираж 872- Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Заказ 272/44

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4