Автоматический режекторный фильтр

Иллюстрации

Показать всеРеферат

1. АВТОМАТИЧЕСКИЙ РЕЖЕКТОРНЫЙ ФИЛЬТР, содержащий перестраиваеваемый фильтр, первый усилитель-ограничитель , последовательно соединенные сумматор и второй усилитель-органичитель и последовательно соединенные фазовый дискриминатор и интегратор, причем первый вход сумматора и вход перестраиваемого фильтра объединены и являются первым входом автоматического режекторного фильтра, первый выход перестраиваемого фильтра является выходом автоматического режекторного фильтра, второй выход перестраиваемого фильтра подключен к входу первого усилителя-органичителя, выход интегратора соединен с управляющим входом перестраиваемого фильтра, а последующие Ц входов сумматора являются соответствующими входами двтоматического режекторного фильтра, отличающийся тем, что, с целью повьшения эффективности подавления помехи, введены блок коммутации фазы, первый инвертор и второй инвертор, причем выход первого инвертора соединен с первым входом блока коммутации фазы, выход первого усилителя-органичителя подключен к второму входу блока коммутации фазы и входу первого инвертора, выход второго инвертора соединен с третьим входом блока коммутации фазы, выход второго усилителя-ограничителя подключен к входу второго инвертора и четвертому входу блока коммутации фазы, а первьш и второй выходы блока коммутации фазы подключены к первому и второму входам фазового дискриминатора. 2. Фильтр по п. 1, о т j и чающийся тем, что блок коммутации фазы содержит первьм, второй, третий и четвертый В-триггеры, первьм и BTopofi элементы ИЛИ, причем D и R входы первого D-триггера и С-вход третьего D -триггера объединены и являются первым входом блоka коммутации фазы,) и R -входы вто; рого D триггера и С-вход четвертого-D-триггера объединены и являются вторым входом блока коммутации фазы,С вход второго D -триггера и D и R .входы четвертогоD-триггера объедине. 00 вы и являются третьим входом блока коммутации фазы, С -вход первого Г-триггера и D и R -входы третьегб D-триггера объединены и являются четвертым входом блока коммутации фазы, выходы первого и второго)-триггеров подключены к входам первого элемента :ИЛИ, выходы третьего и четвертого Г-триггеров подключены к входам второго элемента ШШ, а выходы первого и второго элементов ИЛИ являются первым и вторым выходами блока коммутации фазы соответственно.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

4(зц G 01 S 7/36

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbfTHA (21) 3577506/24 — 09 (22) 14 ° 04.83 (46) 28.02.85. Вюл. № 8 (72) Н.В.Иванов-Шидловский, M.À.Àðõèïîâ, Ю.Г.Чистов и В.a,Âîëков (53) 621.396.933:527.8(088.8) (56) 1. Авторское свидетельство СССР

¹- 324715, кл. Н 04 К 3/00, 1970.

2. Авторское свидетельство СССР

¹ 675382, кл. H 04 B 1/10, 1977 (прототип). (54) (57) 1. АВТОМАТИЧЕСКИЙ РЕЖЕКТОРНЫЙ ФИЛЬТР, содержащий перестраиваеваемый фильтр, первый усилитель-ограничитель, последовательно соединенные сумматор и второй усилитель-органичитель и последовательно соединенные фазовый дискриминатор и интегратор, причем первый вход сумматора и вход перестраиваемого фильтра объединены и являются первым входом автоматического режекторного фильтра, первый выход перестраиваемого фильтра является выходом автоматического режекторного фильтра, второй выход перестраиваемого фильтра подключен к входу первого усилителя-органичителя, выход

:интегратора соединен с. управляющим входом перестраиваемого фильтра, а последующие 8 входов сумматора являются соответствующими входами автоматического режекторного фильтра, отличающийся тем, что, с целью повышения эффективности подавления помехи, введены блок коммутации фазы, первый инвертор и второй инвертор, причем выход первого инвер. тора соединен с первым входом блока

ÄÄSUÄÄ 1142805 А коммутации фазы, выход первого усилителя-органичителя подключен к второму входу блока коммутации фазы и входу первого инвертора, выход второго инвертора соединен с третьим входом блока коммутации фазы, выход второго усилителя-ограничителя подключен к вхоцу второго инвертора и четвертому входу блока коммутации фазы, а первый и второй выходы блока коммутации фазы подключены к первому и второму входам фазового дискриминатора.

2. Фильтр по п. 1, о т s. u ч а ю шийся тем, что блок коммутации фазы содержит первый, второй, третий и четвертый 2 -триггеры, первый и второй элементы ИЛИ, причем

)) и R входы первого 2 -триггера и

С -вход третьего 2 -триггера объединены и являются первым входом блоа коммутации фазы,2 и К -входы вто

ro D триггера и С -вход четвертого"3-триггера объединены и являются вто- рым входом блока коммутации фазы, C . вход второго 23 -триггера и D u R— ,входы четвертого 2 -триггера объедине. ны и являются третьим входом блока коммутации фазы, С -вход первого

D-триггера и D u R -входы третьегб

D-триггера объединены и являются четвертым входом блока коммутации фазы, выходы первого и второго2 -триггеров подключены к входам первого элемента

ИЛИ, выходы третьего и четвертого

3-триггеров подключены к входам второго элемента ИЛИ, а выходы первого и второго элементов ИЛИ являются первым и вторым выходами блока коммутации фазы соответственно.

1 1142805 э

Изобретение относится к радиотех-, нике и может быть использовано s системах навигации, например в аппаратуре импульсно-фазовой радионавигационной системы типа "Лоран-С".

Известен автоматический режекторный фильтр, используемый для подавления узкополосных помех в радионавигационных системах, в состав которого входит генератор копии помехи (11 . 10 Однако известное устройство является весьма сложным.

Наиболее близким техническим решением и изобретению является автоматический режекторный фильтр, содержащий перестраиваемый фильтр, первый усилитель-органичитель, последователь но соединенные сумматор и второй усилитель-ограничитель и последовательно соединенные фазовый дискриминатор и интегратор, причем первый вход сумматора и вход перестраиваемого фильтра объединены и являются первым входом автоматического режекторного фильтра перВый ВыхОд перестраиВаемО го фильтра является выходом автоматического режекторного фильтра, второй выход перегтраиваемого фильтра подключен к входу первого усилителя-ограничителя, выход интегратора соеди30 неп с управляющим входом перестраивае мого фильтра, а последующие N входов сумматора являются соответствующими входами автоматического режекторного фильтра f2)

Однако ири возникновении фазовых искажений в первом и втором усилителях- ограничителях нарушается баланс фазового детектора, смещается частота настройки перестраиваемого фильтра и уменьшается эффективность подавления помехи.

Цель изобретения — повышение эффективности подавления помехи.

Для достижения цели в автоматический режекторный фильтр, содержащий пе рестраиваемый фильтр, первый усилитель-ограничитель, последовательно соединенные сумматор и второй усилитель- ограничитель и последовательно соединенные фазовый дискриминатор и интегратор, причем первый вход сумматора и вход перестраиваемого фильт. ра объедипены и являются первым входом автоматического режекторного фильтра, первый выход перестраиваемо 55 го фильтра является выходом автомати ческого режекторного фильтра, второй выход перестраиваемого фильтра подключен к входу первого усилителя-ог-, раничителя, выход интегратора соеди..нен с управляющим входом перестраиваемого фильтра, а последующие входов сумматора являются соответствующими входами автоматического режекторного фильтра, введены блок коммутации фазы, первый ннвертор и второй инвертюр, причем выход первого инвертора соединен с первым входом блока коммутации фазы, выход пер вого усилителя-ограничителя подключен к втор му входу блока коммутации фазы и входу первого инвертора, выход второго инвертора соединен с третьим входом блока коммутации фазы, выход второго усилителя-ограни„чителя подключен к входу второго инвертора и четвертому входу блока коммутации фазы, а первый и второй выходы блока коммутации фазы подключены к первому и второму входам фазового дискриминатора.

Блок коммутации фазы содержит первый, второй, третий и четвертый

2-триггеры, первый и второй элементы

ИЛИ, причем 3 и К -входы первого

2-триггера и С -вход третьего 2 -триггера объединены и являются первым входом блока коммутации фазы, Q u

1-входы второго D-триггера и С -вход четвертого 3-триггера объединены и являются вторым входом блока коммутации фазы, С -вход второго Q -триггера и )) и R -входы четвертого Н-триггера объедпнены и являются третьим входом блока коммутации. фазы, С -вход первого2 -триггера и 0 и к -входы третьего О -триггера объединены и являются четвертым входом блока коммутации фазы, выходы первого и второго 2-триггеров подключены к входам первого элемента ИЛИ, выходы третьего и четвертого 3 -триггеров подключены к входам второго элемента ИЛИ, а выходы первого и второго элементов

ИЛИ являются первым и вторым выходами блока коммутации фазы соответственно.

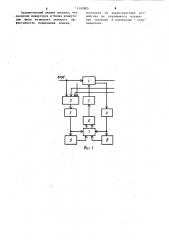

На фиг. 1 представлена структур,ная электрическая схема автоматического режекторного фильтра, на фиг.

2 — пример выполнения блока коммутации фазы, на фиг. 3 — то же, перестраиваемого фильтра, на фиг. 4 эпюры, поясняющие работу блока ком

1мутации фазы.

Автоматический режекторный.фильч р (фиг. 1) содержит перестраиваемый фильтр 1, сумматор 2, интегратор 3, 3 1142 первый усилитель-ограничитель 4, второй усилитель-ограничитель 5, фазовый дискриминатор 6, блок 7 коммутации фазы; первый инвертор 8, второй инвертор 9, блок 7 коммутации фазы (фиг. 2) содержит первый 2-триггер 10

5 второй 3 -триггер 11, третий 2-триггер 12, четвертый 2-триггер 13, первый элемент ИЛИ 14, второй элемент

ИЛИ 15. Перестраиваемый фильтр (фиг.

3) содержит полосовой фильтр 16, уси10 литель 17 и вычитатель 18.

Автоматический режекторный фильтр работает следующим образом.

Пусть на первом входе автоматического режекторного фильтра при15 сутствует узкопог Ьсная помеха, которая поступает на перестраиваемый фильтр 1 и на сумматор 2. На остальные входы сумматора 2 могут поступать сигналы с выходов других автоматических режекторных фильтров, если по условиям работы необходимо осуществлять подавление нескольких разнесенных по частоте помех, что реализуется последовательным включением нескольких автоматических режекторных фильтров.

С выхода сумматора 2 помеха через второй усилитель-ограничитель 5 поступает на блок 7 коммутации фазы, на который, кроме того, поступает сигнал .с второго выхода перестраиваемого фильтра 1.

Таким образом, сигналы с входа перестраиваемого фильтра 1 и с его 35 второго выхода после первого и второго усилителей-ограничителей 4, 5 и блока 7 коммутации фазы поступают на вход фазового дискриминатора 6.

При этом начинает уменьшаться раз- » ность фаз помехи на входе и втором выходе перестраиваемого фильтра 1, а следовательно» будет уменьшаться и сигнал управления на выходе фазового дискриминатора 6, который после усреднения в интеграторе 3 поступа- . ет на управляющий вход перестраиваемого фильтра 1.

В момент настройки перестраиваемого фильтра 1 на помеху сигнал управ- 50 ления на выходе фазового дискриминатора 6 исчезает, и процесс перестройки заканчивается.

Благодаря наличию блока 7 коммутации фазы паразитный сигнал управ- M ления, возникающий за счет несимметрии уровня .ограничения первого и второго усилителей-ограничителей 4, 5, 805 4 периодически меняет знак и в среднем равен нулю, что позволяет значительно уменьшить ошибки в настрой- ке перестраиваемого фильтра 1, вызванные данной несимметрией, и тем .аамым повысить эффективность подав» ления помехи.

Блок 7 коммутации фазы работает следующим образом.

D- òðèããåð срабатывает по счетному

-входу по положительному фронту, а устанавливается в "0" по нулю входного сигнала.

При этом на С -вход первого и второго 2-триггеров 10 и 11 гэступает сигнал с выхода первого усилителя-ограничителя 4, а на 0 и Р -входы — с выхода второго усилителя-ограничителя

5. На С -вход третьего и четвертого

2-триггеров 12 и 13 поступает сигнал с выхода второго усилителя-ограничителя 5, а на 2 и Р -входы — с выхода первого усилителя-ограничителя 4.

По фронту одного из сигналов 2— триггер устанавливается в положение, соответствующее потенциалу другого сигнала, в этот момент присутствующего на 2 -входе и затем устанавливается в нулевое состояние, когда на Я -входе появляется нулевой потенциал. На фиг. 4 (а-О) представлены эпюры сигналов в характерных точках блока 7 коммутации фазы (при несимметричном ограничении сигнала; в пер. вом или втором усилителях-ограничителях 4, 5). Из этих эпюр следует, что при наличии искажений входного сигнала на выходе блока 7 коммутации при настройке автоматического режекторного фильтра на частоту помехи появляется два импульса различной полярности, причем среднее значение выходного сигнала равно нулю.

Перестраиваемый фильтр 1 (фиг.3) работает следующим образом.

Помеха поступает на полосовой фильтр 16, частота настройки которого может изменяться. Полосовой фильтр

16 выделяет помеху, которая поступа- ет на второй выход перестраиваемого фильтра 1 и на усилитель 17, а далее на вычитатель 18. Параметры схемы выбираются таким образом, чтобы на выходе вычитателя 18 помехи компенсировались, т.е. при настройке перестраиваемого фильтра 1 на частоту по; мехи последняя подавляется на первом выходе перестраиваемого фильтра 1 и выделяется на его втором выходе.

1142805

Сравнительный анализ показал, что, введение инверторов и блока коммутацйи фазы позволяет повысить эффективность подавления помехи, поскольку на характеристики уст- ройства не сказываются искажения сигналов в усилителях — ограничителях.

1142805

Фиг З 1142805

3НЯИПИ Заказ 732/40 Тираж 748 Подписное !

Филиал ППП "Патент", г.Укгород, ул.Проектная, 4