Полупроводниковое запоминающее устройство

Иллюстрации

Показать всеРеферат

1. ПОЛУПРОВОДНЖОВОЕ ЗАПОМИНАКШЩЕ УСТРОЙСТВО, содержащее матрицу элементов памяти, каждый из которых состоит из статического триггера и двух управляющих элементов, выполненных на транзисторах, дешифратор строк, дешифратор столбцов, усилители записи, ключевые усили ели, причем затворы транзисторов управляющих элементов каждой строки соединены с выходами дешифратора строк, входы которого являются одними адресными входами устройства, стоки первого и второго транзисторов управляющих элементов каждого столбца соединены с выходами соответствующего усилителя записи, вход которого является информационным входом устройства , а управляющий вход соединен с соответствующим выходом дешифратора столбцов, входы которого являются другими адресными входами устройства, управляющие входы ключевых усилителей соединены с соответствующими выходами дешифратора столбцов, а выходы являются информационным выходом устройства, отличающееся тем, что, с целью расширения области применения устройства за счет совмещения функций оперативного и постоянного запоминаюш:их устройств, в него введены логические элементы и в каждый элемент памяти - два элемента связи, вьтолненных на транзисторах, причем стоки первого и второго транзисторов элементов связи соединены с истоками транзисторов соответствующих управляющих элементов, истоки с соответствующими входами статического триггера, а затворы являются дополнительным входом устройства, входы каждого логического элемента соединены с выxoдa ш соответствующего усилителя записи, управляющий Л вход - с дополнительным входом устройства , а выход - с входом соответствующего ключевого усилителя. 2. Устройство по п. 1, о т л ичающееся тем, что логический элемент содержит нагрузочньш транзистор р-типа и три ключевых транзистора п-типа, причем сток нагрузочного транзистора р-типа соединен с шиной питающего напряжения, истох является выходом логического элемента и соединен со стоками первого и второго ключевых транзисторов , Г)-типа, истоки которых соединены со стоком третьего ключевого транзистора п-типа, исток которого и затвор нагрузочного транзистора р-типа соединены с шиной нулевого потенциала , затвор первого ключевого транзистора п-типа является управляющим входом, а затворы второго и третьего ключевых .транзисторов и-типа - входами логического элемента.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ .

РЕСПУБЛИН (!9) (! !) ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

fO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТЖ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСНОМЪ СВИДЕТЕЛЬСТВУ

I (21) 3576022/24-24 (22) 12.04.83 (46) 28.02.85. Бюл. !! 8 (72) Б.В.Барашенков и Г.В.Павлова (53) 681.327.66(088.8) (56) 1. МикроЭВМ "Электроника Cs" и их применение. Под ред. В.М.Пролейко. N., "Советское радио", 1980, с. 27-32.

2. Горн Л.С., Хазанов Б.И. Элементы микромощных цифровых устройств.

M Атомиздат, 1980, с. 33-37 (прототип) . (54)(57) I. ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАК61ЕЕ УСТРОЙСТВО, содержащее матрицу элементов памяти, каждый из которых состоит из статического триггера и двух управляющих элементов, выполненных на транзисторах, дешифратор строк, дешифратор столбцов, усилители записи, ключевые усилители, причем затворы транзисторов управляющих элементов каждой строки соединены с выходами дешифратора строк, входы которого являются одними адресными входами устройства, стоки первого и второго транзисторов управляющих элементов каждого столбца соединены с выходами соответствующего усилителя записи, вход которого является информационным входом устройства, а управляющий вход соединен с соответствующим выходом дешифратора столбцов, входы которого являются другими адресными входами устройства, .управляющие входы ключевых усилителей соединены с соответствующими выходами дешифратора столбцов, а выходы являются информационным выходом устройства, о т л и ч а ю щ е е с я

4(5!) С 11 С 17/00; G 11 С 11/00 тем, что, с целью расширения области применения устройства за счет совмещения функций оперативного и постоянного запоминающих устройств, в него введены логические элементы и в каждый элемент памяти — два элемента связи, выполненных на транзисторах, причем стоки первого и второго транзисторов элементов связи соединены с истоками транзисторов соответствующих управляющих элементов, истоки— с соответствующими входами статического триггера, а затворы являются дополнительным входом устройства, входы каждого логического элемента соединены с выходами соответствующего усилителя записи, управляющий вход — с дополнительным входом устройства, а выход — с входом соответствующего ключевого усилителя.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что логический элемент содержит нагрузочный транзистор р -типа и три ключевых транзистора и -типа, причем сток нагрузочного транзистора р-типа соединен с шиной питающего напряжения, исток является выходом логического элемента и соединен со стоками первого и второго ключевых транзисторов !!-типа, истоки которых соединены со стоком третьего ключевого транзистора п-типа, исток которого и затвор нагрузочного транзистора р-типа «ф» соединены с шиной нулевого потенциала, затвор первого ключевого транзистора и -типа является управляющим входом, а затворы второго и третьего ключевых .транзисторов и -типа — входами логического элемента.

1142861

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано при построении микроЗВМ, имеющих в своем составе оперативное и постоянное запоминающее устройства.

Известно полупроводниковое запоминающее устройство (ЗУ), содержащее микросхемы оперативного и постоянного ЗУ, каждая из которых содержит накопитель и схемы управления: дешифраторы строк и столбцов и устройство считывания (1 ).

Недостатком такого ЗУ является аппаратная избыточность схем управ- 15 пения и отдельных элементов накопи1О теля ..

Наиболее близким к предлагаемому является оперативное запоминающее устройство, содержащее накопитель 2О для хранения оперативной информации, дешифраторы строк и столбцов, блоки записи и считывания (2) .

Недостатком устройства является невозможность использования его для 25 хранения постоянной информации, что ограничивает область применения ЗУ.

Цель изобретения — расширение области применения ЗУ за счет совмещения функций оперативного и посто-- gp. янного запоминающих устройств и обеспечения возможности одновременного хранения независимых оперативной и постоянной информаций в каждом элементе памяти.

Поставленная цель достигается тем, что в полупроводниковое запоминающее устройство, содержащее матрицу элементов памяти, каждый из которых состоит из статического триггера 4О и двух управляющих элементов, выполненных на транзисторах, дешифратор строк, дешифратор столбцов, усилители записи, ключевые усилители, причем затворы транзисторов управляющих элементов каждой строки соединены с выходами дешифратора строк, входы которого являются одними адресНыми входами устройства, стоки первого и второго транзисторов управляющих элементов каждого столбца соединены с выходами соответствующего усилителя записи, вход которого является информационным входом устройства, а управляющий вход соеди-SS

: нен с соответствующим выходом дешифратора столбцов, входы которого яв ляются другими адресными входами устройства, управляющие входы ключевых усилителей соединены с соответствующими выходами дешифратора столбцов, а выходы являются информационным выходом устройства, введены логические элементы и в каждый элемент памяти — два элемента связи, выполненных на транзисторах, причем стоки первого и второго транзисторов элементов связи соединены с истоками транзисторов соответствующих управляющих элементов, истоки — с соответствующими входами статического триггера, а затворы являются дополнительным входом устройства, входы каждого логического элемента соединены с выходами соответствующего усилителя записи, управляющий входс дополнительным входом устройства,. а выход — с входом соответствующего ключевого усилителя.

При этом каждый логический элемент содержит нагрузочный транзистор р òèïà и три ключевых транзистора п-типа, причем сток нагрузочного транзистора р-типа соединен с шиной питающего напряжения, исток является выходом логического элемента и соединен со стоками первого и второго ключевых транзисторов и -типа, истоки которых соединены со стоком третьего ключевого транзистора п-ти-, па, исток которого и затвор нагрузочного транзистора р-типа соединены с шиной нулевого потенциала, затвор первого ключевого транзистора и-типа является управляющим входом, а затворы второго и третьего ключевых транзисторов п-типа — входами логического элемента.

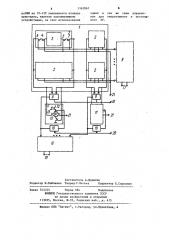

На чертеже изображена схема одного разряда предлагаемого запоминающего устройства.

Запоминающее устройство содержит матрицу 1 элементов памяти (ЭП) 2, состоящих из статического триггера З первого и второго элементов связи, выполненных на транзисторах 4 и 5, первого и второго управляющих транзисторов б и 7, усилители 8 записи, дешифратор 9 строк, дешифратор 10 столбцов, логический элемент 11, нагрузочный транзистор 12 логического элемента, первый, второй и третий ключевые транзисторы 13, 14 и 15 логического элемента, ключевой усилитель 16, одни и другие адресные входы 17 и 18, информационный

142861 4 зисторы 6 и 7 и транзисторы 4 и 5.

Второй ключевой транзистор 14 логического элемента 11 открыт сигналом

11 11

1 на входе 21. На выходе логического элемента устанавливается инверсия напряжения на инверсной шине столбца, и через ключевой усилитель 16 выбранного столбца она поступает на информационный выход устрой10 ства.20.

В режиме считывания постоянной информации первый и второй транзисторы 4 и 5 ЭП 2 закрыты сигналом"0" на дополнительном управляющем вхо{5 де 21.

В режиме считывания оперативной информации состояние шин столбцов определяется состоянием выбранного

ЭП 2, когда открыты управляющие транПри использовании предлагаемого устройства в однокристалльной мик3 1 вход 19, информационный выход 20, дополнительный управляющий вход 21.

Устройство работает в четырех режимах: запись, считывание оперативной информации, считывание постоянной информации, хранение информации. Оперативная информация хранится в статическом триггере 3 ЭП.

Хранение оперативной информации обес печивается устойчивостью состояния триггера 3 при поступлении на него напряжения питания. Постоянная информация определяется первым и вторым дополнительными транзисторами 4 и 5 ЭП 2. Программирование достигается размыканием на стадии изготовления устройства заранее предусмотСостояние прямой и инверсной ренных проводящих перемычек, связышин выбранного столбца и соответстваюших сток — исток этих транзистовенно сигналов на затворах первого ров. Эанесение в ЭП 2 единицы (нуля) 20 и третьего ключевых транзисторов 13 информации соответствует наличию " 15 логического элемента 11 опреде(отсутствию) проводящих перемычек лЯетсЯ отсУтствием или наличием пЕРемежду стоком и истоком первого и вто- мычек. ПРи наличии пеРемычек на широго дополнительных транзисторов 4 нах столбца в момент выборки устанав. .и 5 ЭП 2. Таким образом, и оператив- 25 ливается парафазная информация, при ная, и постоянная информации хранят- отсутствии перемычек состояние шин ся на одном и том же ЭП 2 независи- столбцов и сигналы на затвоРах пеРмо друг От друга При Обраще;ии вого и ТРетьего активных ТРанзисток оперативной информации на допол- ров 13 и 15 равны высоким потенцианительн и управляющий вход 21 уст- 0 лам, опРеделЯемым УсилителЯми 8 эа30

ОИ обращении к постоянной информации— закрыт сигналом "0" на входе 2 1. При сигнал "0". парафазной, информации на затворах

В режиме записи оперативной инпервого и третьего ключевых транзисформации на информационный вход 19 торов 13 и 15 логического элемени адресные входы 17 и 18 подается

35 та 11 на его выходе образуется сиг11 11 код числа и код адреса ЭП 2 в кото - нал 1, а пРи Равных высоких порый она должна быть записана . тенциалах — сигнал 0", который чеКод адреса поступает в дешифра- рез ключевой усилитель выбранного тор 9 строк и дешифратор 10 столб- столбца поступают на информацион40 цов происходит BbI60pK8 стрОки H íü Bü îÄ 20 столбца в матрице ЗП, при этом управляющие транзисторы 6 и 7 ЭП 2 откры- преДлагаемом УстРойстве длЯ ты сигналом "1" на их затворах. выполнениЯ фУнкций хРанениЯ как опеВ зависимости от парафазного сигпала Ративнои, так и постоЯнной информана вьоде у,ителя 8 записи на пря- Н Ции " пользУютсЯ ОДНИ " те же элемой и инверсной шинах выбранного менты памЯти. ПРи этом опеРативнаЯ столбца устанавливаются парафазные и постоянная информации не зависят логич ские сигналы Транзисторы 4 и 5 ЭП 2 Открыты сигналом 1 а - применениЯ УСТРойства посколькУ

50 о но и т

1 полнительном управляющем входе 21 .Триггер 3 ЭП 2 принимает состояние, соответствующее значению информации на входе 19. может быть использовано для хранения и постоянной, и оперативной инфарма55 Ций.

1142861

Составитель А,Дерюгин

Редактор И.Рыбченко Техред С.Легеза Корректор Е.Сирохман

Заказ 743/43 Тираж 584 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскай наб., д. 4/5

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная, 4 роЭВМ на 10-15Х уменьшается площадь кристалла, занятая запоминающими устройствами, за счет использования одних и тех же схем управления для оперативного и постоямного ЗУ.