Устройство для вычисления зависимости @

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЗАВИСИМОСТИ у х2+х2+х2 , содержащее первьй и второй сумматоры, первый и второй коммутаторы и первую и вторую схемы сравнения, причем выход первой схемы сравнения соединен с входом управления первого коммутатора, о тличающееся тем, что, с целью сокращения аппаратурных затрат, в него введены первый и второй вычитатели и узел сортировки, первый, второй и третий информационные входы которого соединены соответственно с первым, BToptJM и третьем входами данных устройства, выход большого аргумента узла сортировки подключён к первому информационному входу первого коммутатора и первого вычитателя, выход первого вычитателя соединен с первым информационным входом первого сумматора, выход большого аргумента узла сортировки подключен к второму информационному входу первого вычитателя и первому информационному входу первой схемы сравнения со сдвигом на три разряда в сторону младших разрядов , выход среднего аргумента узла сортировки соединен с вторым информационным входом первого сумматора и первой схемы сравнения со сдвигом на один разряд в сторону младших разрядов , второй информационный вход первого коммутатора соединен с выходом первого сумматора, выход меньшего аргумента узла сортировки соединен с первым информационным входом второго сумматора и в,торой схемы сравнения со сдвигом на один разряд в сторону младших разрядов, выход первого сумматора подключен первым информащ онным входом второго вычитателя и втогрого коммутатора, выход второго коммутатора соединен с выходом результата устройства, разрядные выходы первого коммутатора подключены к вторым информационным входам второго вычитасл теля и второй схемы сравнения со 00 сдвигом на три разряда в сторону 4 младших разрядов, выход второго вычитателя соединен с вторым информационным входом второго сумматора, управляющий вход которого соединен с вы- . ходом второй схемы сравнения.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„Я0„„1145341

4(51) G 06 F 7 552

-:ГA .: ; »» - ." xf, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

««»л»» . "; . ««» «»

«4:Ю»« д»» ». «ЦИ,Ю% 3ЮИЯВХ: Ь

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbfTMA (21) 3668558/24-24 (22) 30. 11. 83 (46} 15. 03. 85. Бюл. № 10 (72) Е.Я.Ваврук, Л.Б.Заячкивская, P.C.Ëàáÿê и В.M.Ðàâñêèé (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР № 752332, кл. G 06 F 7/552, 1979.

2. Авторское свидетельство СССР № 1010621, кл. G 06 F 7/552, 1981 (прототип). (54)(57} УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ з«»висимосхи y=fx» «»+x», co«»epaa»»»ee первый и второй сумматоры, первый и второй коммутаторы и первую и вторую схемы сравнения, причем выход первой схемы сравнения соединен с входом управления первого коммутатора, о тл и ч а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, в него введены первый и второй вычитатели и узел сортировки, первый, второй и третий информационные входы которого соединены соответственно с первым, вторым и третьем входами данных устройства, выход большого аргумента узла сортировки подключен к первому информационному входу первого коммутатора и первого вычитателя, выход первого вычитателя соединен с первым информационным входом первого сумматора, выход большого аргумента узла сортировки подключен к второму информационному входу первого вычитателя и первому информационному входу первой схемы сравнения со сдвигом на три разряда в сторону младших разрядов, выход среднего аргумента узла сортировки соединен с вторым информационным входом первого сумматора и первой схемы сравнения со сдвигом на один разряд в сторону младших разрядов, второй информационный вход первого коммутатора соединен с выходом первого сумматора, выход меньшего аргумента узла сортировки соединен с первым информационным входом второго сумматора и второй схемы сравнения со сдвигом на один разряд в сторону младших разрядов, выход первого сумматора подключен первым информационным входом второго вычитателя и вто-,. рого коммутатора, выход второго коммутатора соединен с выходом результата устройства, разрядные выходы первого коммутатора подключены к вторым д информациоцным входам второго вычитателя и второй схемы сравнения со сдвигом на три разряда в сторону младших разрядов, выход второго вычи-, тателя соединен с вторым информацион-.; ным входом второго сумматора, управ- ляющий вход которого соединен с выходом второй схемы сравнения.

1145341

Изобретение относится к вычислительной технике и может испольэоваться в специализированных вычислительных устройствах для оперативного вычисления корня квадратного из суммы квадратов трех чисел.

Известно устройство для вычисления функцни у 1х +х, содерхещее регистр первого операнда, два счетчика порядка, блок управления и дешиф- 10 ратор, входы которого подключены к разрядным выходам первого счетчика порядка, а выход — к разрядным входам счетчика второго операнда, выход переполнения которого подключен 1$ к входу первого счетчика порядка 111.

Недостатками этого устройства являются ограниченные функциональные возможности — вычисляется корень квадратный только суммы двух чисел, 20 и относительно низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для вычисления функции

z1x тхя, содержащее три схени срев-ji нения, два коммутатора, два сумматора, шесть сдвигателей и элемент И, причем входы аргументов подключены к входам двух коммутаторов, а к че, тырем входам четырех сдвигателей под-З0 ключены четыре входа задания постоян" ной BBJIHMHHbf cpBHra f2).

Недостатком известного устройства являются большие анпаратурные затраты.

Цель изобретения — сокращение ап35 паратурных затрат.

Поставленная цель достигается тем, что в устройстве для вычисления вевисииости y=fx +x +x содержещее з 40 первый и второй сумматоры, первый и второй коммутаторы, и первую и вторую схемы сравнения, причем выход первой схемы сравнения соединен со входами управления первого коммутатора, введены первый и второй вычитатели и узел сортировки, первый, второй и третий информационные входы которого соединены соответственно с первым, вторым и третьим входами данных устройства, выход большего аргу$0 мента узла сортировки подключен к первому информационному входу первого коммутатора и первого вычитателя, выход первого вычитателя соединен с первым информационным входом первого сумматора, выход большего аргумента узла сортировки подключен к второму информационному входу первого вычитателя и первому информационному входу первой схемы сравнения со сдвигом на три разряда в сторону младших разрядов, выход среднего аргумента узла сортировки соединен со вторым информационным входом первого сумматора и первой схемы сравнения со сдвигом на один разряд в сторону младших разрядов, второй информационный вход первого коммутатора соединен с выходом первого сумматора, выходы меньшего аргумента узла сортировки соединен с первым информационным входом второго сумматора и второй схемы сравнения со сдвигом на один разряд в сторону младших разрядов, выход первого коммутатора, подключен к первым информационным входам второго вычитателя и второго коммутатора, выход второго коммутатора соединен с выходом результата устройства, раз-. рядные выходы первого коммутатора подключены ко вторым информационным входам второго вычитателя и второй схемы сравнения со сдвигом на три разряда в сторону младших разрядов, выход вычитателя соединен со вторым информационным входом второго сумматора, выход которого подключен ко второму информационному входу второго коммутатора, управляющий вход которого соединен с выходом второй схемы сравнения.

Зависимость y=1x>+xf+xf прецстевляется в виде у у, +х, и вычисление разбивается на два этапа

1х, у шах 7 1, 1

812!2

- х +-(x у у=шах 7 1 — у„+ -(х,1при условии хрх >хз.

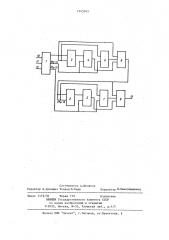

На чертеже приведена функциональная схема устройства.

Устройство содержит узла 1 сортировки, первый 2 н второй 3 вычитатели, первый 4 и второй 5 сумматоры, первую 6 и вторую 7 схемы сравнения, первый 8 и второй 9 коммутаторы, первый, второй и третий входы данных

10, 11 и 1 2 устройства, выход 13 результата устройства.

Устройство работает следующим образом.

На входы 10, 11, 12 устройства и соответственно на входы узла 1 сортировки поступают числа.

На выходе узла 1 на первом выходе получаем х,, на втором х, на третьем х, при условии, что х <х <х

2 s т.е. на первом выходе — большее число, на третьем — самое меньшее.

С первого выхода узла 1 сортировки число х, поступает на первые входы первого вычитателя, на вторые входы первого вычитателя поступает чис- 1ð ло х„, сдвинутое на три разряда в сторону младших разрядов, т.е. 1/8 х,. На первом вычитателе 2 получаем

7 х — - x — х . С выхода первого вы1 8 1 8 читателя 2 число 7/8 х, поступает на первые входи первого сумматора 4, на вторые входы которого поступает

2 число x,,сдвинутое на единицу в сто рону младших разрядов, т.е. 1/2 х . На выходе первого сумматора 4 получа7 ем - х + - х . Одновременно на пер8 2 вой схеме 6 сравнения сравниваются значения 1/8 х, и 1/2 х>. Если 1/2 х <д а1/8 х„схемы б сравненйя вырабатывает сйгнал управления коммутатором .

8, который открывает первые входы первого коммутатора 8, т.е. Hà его выходе получаем значение у x 1.

1145341 4

Если 1/2 х )1/8 x„, сигнал управления не вырабатывается и на выходе первого коммутатора 8 получаем y = (х (+ - (x

7 1

8 " 2 2

Вторые вычитатели 3, сумматор 5, схемы 7 сравнения и коммутатор 9 работают аналогичным образом. х.е. . на выходе второго вычитателя 3 у

1 7

- — у — у на выходе второго сум8 8 матора 5 получаем 7/8 у, +1/2 t хД, на выходе второго коммутатора 9 полуI У1

1 ,чаем у=шах 7 1 у + - х ) . .Ошибка вы8 2 э числения промеауточного результата равна у, 33, а общая ошибка вычисления у 2-3WX.

Расчет ошибок произведен на ЭВМ

И-4030.

Применение предлагаемого устройства вместо устройства — прототипа позволило существенно уменьшить аппаратурные затраты, щжмерно в 1,5 раза.

Кроме того, такой принцип построе" ния устройства позволяет вычислять зависимость типа у х, +х +,; .,+х с ошибкой вычисления Еф 3 {и-1)Х и минимальными аппаратурнычи затратами.

1 145341

Составитель А.Шуляков

Редактор А.Долинич Техред М.Надь г

Корректор И-Максимишинец

Филиал ППП "Патент", г.Ужгород, ул.Проектная, ф

Заказ 1173/36 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, И-35, Раушская наб., д.4/5