Частотный модулятор

Иллюстрации

Показать всеРеферат

ЧАСТОТНЫЙ МОДУЛЯТОР, содержащий шины модулируемой и модулирую , щей частот, а также делитель модулирующей частоты и делитель модулируемой частоты на триггерах, о т,л ичающийся тем, что, с целью расширения рабочего диапазона частот. в него дополнительно введены коммутатор и триггер, причем делитель модулирующей частоты выполнен в виде реверсивного счетчика, делитель модулируемой частоты выполнен в виде сдвигового регистра с перекрестными связями между триггерами, шина модулируемой частоты подключена к синхронизирующему входу делителя модулируемой частоты, выходы которого подключены к информационным входам коммутатора , управляющие входы которого соединены с выходами делителя модулирующей частоты, а выход - с выходной шиной и синхронизирующим входом а триггера, информационный вход которого соединен с шиной модулирующей частоты, а выход - со счетным входом делителя модулируннцей частоты, управ ляющий вход которого соединен с шиной Направление счета.

„„SU„„1145473 А

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

1дц Н 03 К 7/О

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3628972/24-21 .(23) 21.07.84 .,(46) 15.03.85. Бюл. ¹ 10 (72) Г.И. Каплун и В.P. Кузнецов (71) Дальневосточный ордена Трудового Красного Знамени политехнический институт им. В.В. Куйбьппева .,(53) 621.374.38(088.8) (56) 1. Илиодоров В. Дробные делите ли и умножители частоты. Радио", № 9, 1981, с. 59.

2. Авторское свидетельство СССР

¹ 534860, кл. H 03 К 7/00, 1975 (прототип)., (54)(57) ЧАСТОТНЬЙ МОДУЛЯТОР, содержащий шины модулируемой и модулирую, щей частот, а также делитель модулирующей частоты и делитель модулируемой частоты на триггерах, о т л и. ч а ю шийся тем, что, с целью расширения рабочего диапазона частот, в него дополнительно введены коммутатор и триггер, причем делитель модулирующей частоты выполнен в виде реверсивного счетчика, делитель модулируемой частоты выполнен в виде сдвигового регистра с перекрестными связями между триггерами, шина модулируемой частоты подключена к синхронизирующему входу делителя модулируемой частоты, выходы которого подключены к информационным входам коммутатора, управляющие входы которого соединены с выходами делителя модулирующей частоты, а выход — с выходной шиной и синхронизирующим входом а триггера, информационный вход которого соединен с шиной модулирующей частоты, а выход — со счетным входом делителя модулирующей частоты, управляющий вход которого соединен с шиной "Направление счета".

11.45473

Изобретение относится к импульсной технике и может быть использовано при конструировании генераторов с управляемой частотой.

Известны устройства для формирования модулированной последовательности импульсов, содержащие соединенные последовательно суммирующий блок и делитель частоты для получения выходной частоты равной сумме модули- 10 руемой и модулирующей частот или соединенные последовательно элемент запрета и делитель частоты для полу- чения выходной частоты, равной разности модулируемой и модулирующей частот

Недостатками данного устройства являются узкий рабочий диапазон выходной частоты, связанный с тем, что импульс модулирующей частотыдол- 20

1жен располагаться между импульсами модулируемой частоты, а также сложность конструкции и синхронизации обоих частот при работе устройства в режиме суммирования и вычитания частот.

Наиболее близок к предлагаемому по технической сущности является частотный модулятор, содержащий шины модулируемой и модулирующей частот, делитель модулируемой частоты на триггерах, делитель модулирующей частоты, формирователи импульсов и элемент запрета, причем выходы триггеров модулирующей частоты через формирователи импульсов подключены к установочным входам, триггеров делителя модулируемой частоты, вход которого соединен с выходом элемента запрета, вход которого соединен с шиной

4G модулируемой частоты, а управляющий вход и вход делителя модулирующей частоты соединены с шиной модулирующей частоты. Делитель модулируемой частоты делит модулируемую частоту, 45 а при приходе импульса модулирующей частоты, срабатывает делитель модулирующей частоты, вызывая через формирователи установку в соответствующее положение триггеров делителя модулируемой частоты, при этом этот импульс блокирует прохождение через элемент запрета импульса модулируемой частоты (21 .

Недостатками известного устройства являются узкий рабочий диапазон частоты, вызванный последовательным срабатыванием триггеров обоих делителей, что вызывает снижение максимальной модулируемой частоты по сравнению с предельной частотой срабатывания триггеров, а также регулирование частоты только в области суммы обоих частот.

Цель изобретения — расширение ра-бочего диапазона частот, путем исключения последовательного срабатывания делителей и обеспечения суммы и разности модулируемой и модулирующей частот.

Поставленная цель достигается тем, что в частотный модулятор, содержащий шины модулируемой и модулирующей частот, делитель модулирующей частоты и делитель модулируемой частоты на триггерах, дополнительно введены коммутатор и триггер, причем делитель модулирующей частоты выполнен в виде реверсивного счетчика, делитель модулируемой частоты выполнен как сдвиговый регистр с Перекрестными связями между триггерами, шина модулируемой частоты подключена к синхронизирующему входу делителя модулируемой частоты, выходы которбго подключены к информационным входам коммутатора управляющие входы которого соединены с выходами делителя модулирующей частоты, а выход — с

3 вьжодной шиной и синхронизирующим входом триггера, информационный вход, которого соединен с шиной модулирующей частоты, а выход — со счетным входом делителя модулирукнцей частоты, управляющий вход которого соединен с шиной "Направление счета .

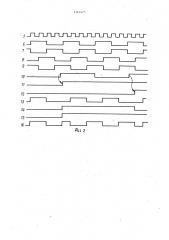

На фиг.1 представлена структурная схема частотного модулятора; на фиг.2 — временные диаграммы его работы; на фиг.3 — пример реализации частотного модулятора на микросхемах серии 155 для и = 2.

Частотный модулятор содержит делитель 1 модулируемой частоты, коммутатор 2, делитель 3 модулирующей частоты и триггер 4, причем синхронизирующий вход делителя 1 модулируемой частоты соединен с шиной модулируемой частоты, а его выходы — с информационными входами коммутатора 2, управляющие входы которого соединены с выходами делителя 3 модулирующей частоты, а выход — с синхронизирующим входом триггера 4, информационный вход которого соединен с шиной модулирующей частоты, а выход — со счетным входом делителя модулирующей час11454

50

3 тоты, управляющий вход KoTopoI соединен с шиной "Направление счета", На фиг.2 приведены импульсы 5 модулируемой частоты, импульсы 6 и 7 »а прямом и инверсном выходах триггера делителя 1 модулируемой частоты, импульсы 8 и 9 на прямом и инверсном выходах второго триггера делителя 1 модулируемой частоты, импульсы 10 модулирующей частоты, импульсы 11 и

12 на выходах первого и второго триггеров делителя 3 модулирующей частоты в режиме вычитания частот, выходные импульсы 13 частотного модулятора в режиме вычитания частот, импульсы 14 и 15 на выходах первого и второго триггеров делителя 3 модулирующей частоты в режиме сложения частот и выходные импульсы 16 частотного модулятора в режиме сложения частот.

При выполнении частотного модулятора на микросхемах серии 155, делитель 1 модулируемой частоты может быть выполнен на микросхемах К 155 25

ТМ2; коммутатор 2 — на микросхемах

К155 ИЕ7 и К155 ЛАЗ, а триггер 4— на микросхеме К155ТМ-2.

Частотный модулятор работает следующим образом.

ЗО

На синхронизирующий вход делителя 1 модулируемой частоты поступают импульсы с частотой f. На прямых и инверсных выходах и триггеров этого делителя образуется последовательность из 2п,сдвинутых прямоугольных

35 напряжений с частотой f/2n, (где n— число разрядов делителя модулируемой частоты). Выходные сигналы этого делителя поступают на информационные входы коммутатора 2. Управляющие входы коммутатора 2 подключены к выI ходам реверсивного делителя 3 модулирующей частоты так, что на выход коммутатора 2 проходит только один

i-и информационный сигнал, поданный

45 на вход коммутатора 2 с номером i определяемым текущим значением кода делителя 3. Выходной сигнал коммутатора 2 подается. на вход синхронизации триггера 4. При поступлении на информационный вход триггера 4 импульса модулирующей частоты триггер

4 перейдет в единичное состояние по

73 4 переднему фронту сигнала на его входе синхронизации. Затем по переднему фронту выходного сигнала триггера 4 изменится код делителя 3, причем в зависимости от сигнала, управляющего направлением счета, к содержимому счетчика будет прибавляться.или вычитаться единица. Добавление единицы к содержимому счетчика 3 вызовет подключение к выходу коммутатора 2 следующего (i+1) -ro информационного сигнала, имеющего запаздывание по отношению к i-му информационному сигналу на время, оавное периоду Т импульсов модулируемой частоты. Это приведет к увеличению положительного полупериода выходного сигнала коммутатора 2 на величину Ту, что эквивалентно запрету прохождения одного импульса модулируемой частоты на вход делителя 1. Среднее значение частоты выходных импульсов коммутатора 2 при этом будет равно (f-F)/(2n).

Аналогично при переводе .реверсивного делителя 3 в режим вычитания среднее значение частоты выходных импульсов коммутатора 2 будет равно (f+F) /(2n) .

Предельная частота модулируемого сигнала f равна предельной частоте срабатывания триггеров делителя 1.

Разрядность делителя 1 определяется из условия, что суммарная задержка срабатывания триггера 4, делителя

3 и коммутатора 2 не превышает величину (n-1)Tg . Действительно время (n-1)Т длится положительный полупериод выходного сигнала коммутатора

2 при работе делителя 3 в режиме вычитания, Частота модулирующего сигнала F должна быть не выше f/(2п).

Введение в частотный модулятор триггера и коммутатора, а так же выполнение его делителей в виде реверсивного счетчика и регистра сдвига с перекрестными связями позволяет увеличить частоту модулируемого сигнала до предельной частоты срабатывания триггеров делителей и, кроме того, осуществлять как режим сложения, так и режим вычитания модулируемой и модулирующей частот, что существенно расширяет рабочий диапазон частот модулятора.

114 54 1 l

Фиг.2

1145473

Составитель Е. Борзов

Редактор Л. Пчелинская Техред Л.Коцюбняк Корректор В. Бутяга

Заказ 1187/42 Тирах 872 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4