Цифровой фильтр

Иллюстрации

Показать всеРеферат

1. ЦИФРОВОЙ ФИЛЬТР, содержащий первый накапливающий сумматор, первый блок памяти, блок синхронизации и последовательно соединенные первый регистр сдвига, первый мультиплексор и второй накапливающий сумматор, отличающийся тем, что, с целью увеличения быстродействия , в него введены последовательно соединенные и включенные между выходами второго и входами первого накапливающих сумматоров первый блок элементов И, второй регистр сдвига, второй блок элементов И, второй блок памяти и второй мультиплексор , вторые информационные входы которого подключены к выходам первого блока памяти , вторые информационные входы первого мультиплексора объединены с его п рвыми информационными входами, причем информационный вход, соответствующий i-му (i 1,2, ...,п) разряду первых информационных входов, соединен с информационным вхо дом, соответствующим (i-Ь 1)-му разряду вторых информационных входов, первый информационный вход которого, соответствующий младшему разряду, соединен с общей щиной, информационные входы первого блока памяти соединены с выходами первого блока элементов И, с первого по шестой выходы блока синхронизации подключены к входу управления первого мультиплексора , к входу управления второго накапливающего сумматора, к объединенным входам управления первого блока элементов И и первого блока памяти, к входу управления второго регистра сдвига, к объединенным входам управления второго блока элементов И и второго блока памяти и к входу управления второго мультиплексора соответственно , при этом входь первого регистра сдвига являются входами, а выходы перkn вого накапливающего сумматора - выходами цифрового фильтра. 2. Фильтр по п. 1, отличающийся тем, что блок синхронизации содержит генератор импульсов, первый и второй таймеры, первый , второй, третий и четвертый делители частоты, входы которых соединены с выхо- , дом генератора импульсов, выхрй первого делителя частоты является первьш выходом блока синхронизации, выход .второго делиО5 теля частоты подключен к входам первого и второго таймеров и является вторым выхо ;о дом блока синхронизации, а выходы перво00 го , третьего делителя частоты, второго таймера и четвертого делителя частоты являются третьим, четвертым, пятым и щестым выходами блока синхронизации соответственно .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„,SU„, 1146798

4(5D Н 03 Н 1704

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

RO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3646653 24-09 (22) 27.09.83 (46) 23.03.85. Бюл. № 11 (72) В. Д. Анисимов и Ю. И. Хасин (71) Институт аналитического приборостроения научно-технического объединения АН

СССР (53) 681.325 (088.8) (56) 1. Антоныч А. Цифровые фильтры. М., «Радио и связь», 1983, с. 297, рис. 14.34.

2. Авторское свидетельство СССР № 904201, кл. Н 03 Н 17/04, 1980 (прототип) . (54) (57) 1. ЦИФРОВОЙ ФИЛЬТР, содержащий первый накапливающий сумматор, первый блок памяти, блок синхронизации и последовательно соединенные первый регистр сдвига; первый мультиплексор и второй накапливающий сумматор, отличающийся тем, что, с целью увеличения быстродействия, в него введены последовательно соединенные и включенные между выходами второго и входами первого накапливающих сумматоров первый блок элементов И, второй регистр сдвига, второй блок элементов И, второй блок памяти и второй мультиплексор, вторые информационные входы которого подключены к выходам первого, блока памяти, вторые информационные входы первого мультиплексора объединены с его первыми информационными входами, причем информационный вход, соответствующий i-му (i = 1,2, ...,п) разряду первых информационных входов, ееединен с информационным входом, соответствующим (i + 1) -му разряду вторых информационных входов, первый информационный вход которого, соответствующий младшему разряду, соединен с общей шиной, информационные входы первого блока памяти соединены с выходами первого блока элементов И, с первого по шестой выходы блока синхронизации подключены.к входу управления первого мультиплексора, к входу управления. второго накапливающего сумматора, к объединенным входам управления первого блока элемен-! тов И и первого блока памяти, к входу управления второго регистра сдвига, к объединенным входам управления второго блока элементов И и второго блока памяти и к входу управления второго мультиплексора соответственно, при этом входы первого регистра сдвига являются входами, а выходы первого накапливающего сумматора — выходами цифрового фильтра.

2. Фильтр по п. 1, отличающийся тем, что блок синхронизации содержит генератор импульсов, первый и второй таймеры, первый, второй, третий и четвертый делители частоты, входы которых соединены с выхо-, дом генератора импульсов, выхрд первого делителя частоты является пером выходом блока синхронизации, выход .второго делителя частоты подключен к входам первого и второго таймеров и является вторым выходом блока синхронизации, а выходы первого таймера, третьего делителя частоты, второго таймера и четвертого. делителя частоты являются третьим, четвертым, пятым и шестым выходами блока синхронизации соответственно.

1146798

Изобретение относится к радиотехнике и может быть использовано в системах цифровой обработки информации.

Известен цифровой фильтр, содержащий накапливающий сумматор, выход которого 5 является выходом цифрового фильтра, последовательно соединенные и подключенные к входу цифрового фильтра первые регистры сдвига, между выходами которых и первыми входами накапливающего сумматора включены первые блоки памяти, последовательно соединенные и подключенные к выходу накапливающего сумматора, вторые регистры сдвига, между выходами которых и вторыми входами накапливающего сумматора включены вторые блоки памяти (1). 15

Недостатком этого цифрового фильтра является большой требуемый объем памяти каждого блока памяти.

Наиболее близким по технической сущности к предлагаемому является цифровой фильтр, содержащий последовательно соединенные формирователь импульсов, адресный счетчик, первый блок памяти, второй регистр сдвига, умножитель, первый накапливающий сумматор, выход которого является выходом цифрового фильтра, последо- 25 вательно соединенные второй блок памяти, комбинационный сумматор, третий блок памяти, первый регистр сдвига, мультиплексор и второй накапливающий сумматор, вход управления которого подключен к выходу формирователя импульсов, а- выход соединен с другим входом умножителя, а также дешифратор, вход которого подключен к первому выходу второго блока памяти, а выход соединен с входами управления треть° его блока памяти и мультиплексора, вторые информационные входы которых объединены и являются входом цифрового фильтра, блок синхронизации, первый выход которого через первый адресный счетчик подключен к второму информационному входу комбинационного сумматора, второй выход блока 40 синхронизации-через второй адресный счетчик соединен с входом второго блока памяти, второй выход которого подключен к входу формирователя импульсов (21.

Однако известный цифровой фильтр обладает недостаточно высоким быстродей- 45 ствием.

Цель изобретения — повышение быстродействия цифрового фильтра.

Цель достигается тем, что в цифровой фильтр, содержащий первый накапливающий сумматор, первый блок памяти, блок. синхронизации и последовательно соединенные первый регистра сдвига, первый мультиплексор и второй накапливающий сумматор, введены последовательно соединенные и включенные между выходами второго и вхо- 55 дами первого накапливающих сумматоров первый блок элементов И, второй регистр сдвига, второй блок элементов И, второй блок памяти и второй мультиплексор, вторые информационные. входы которого подключены к выходам первого блока памяти,.вторые информационные входы первого мультиплексора объединены с его первыми информационными входами, причем информационный вход, соответствующий i-му (i = 1, 2, ..., п) разряду первых информационных входов, соединен с информационным входом, соответствующим (1 + 1) -му разряду вторых информационных входов, первый информационный вход которого, соответствующий младшему разряду, еоединен с общей шиной, информационные входы первого блока памяти соединены с выходами первого блока элементов И, с первого по шестой выходы блока синхронизации подключены к входу управления первого мультиплексора, к входу управления второго накапливающего сумматора, к объединенным входам управления первого блока элементов И и первого блока памяти, к входу управления второго регистра сдвига, к объединенным входам управления второго блока элементов И и второго блока памяти и к входу управления второго мультиплексора соответственно, при этом входы первого регистра сдвига являются входами, а вь ходы первого накапливающего сумматора — выходами цифрового фильтра.

Блок синхронизации содержит генератор имйульсов, первый и второй таймеры, первый, второй, третий и четвертый делители частоты, входы которых соединены с выходом генератора импульсов, выход первого делителя частоты является первым выходом блока синхронизации, выход второго делителя част оты подключен к входам первого и второго таймеров и является вторым выходом блока синхронизации, а выходы первого таймера, третьего делителя частоты, второго таймера и четвертого делителя частоты являются третьим, четвертым, пятым и шестым выходами блока синхронизации соответственноо.

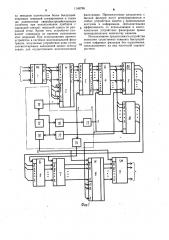

На фиг. 1 приведена структурная электрическая схема цифрового фильтра; на фиг. 2— диаграмма, поясняющая его работу.

Цифровой фильтр содержит первый регистр 1 сдвига, первый мультиплексор 2; второй накапливающий сумматор 3, первый блок 4 элементов И, второй регистр 5 сдвига, второй блок 6 элементов И, второй блок 7 памяти, второй мультиплексор 8, первый накапливающий сумматор 9, первый блок 10 памяти, блок 11 синхронизации, который состоит из генератора 12 импульсов, первого и второго таймеров 13 и 14, первого, второго, третьего и четвертого делителей 15 — 18 частоты.

Цифровой фильтр работает следующим . образом.

Текущая входная выборка сигнала в виде цифрового параллельного кода поступа1!46798 ет на вхоЯ регистра 1 сдвига, где она запоминается до прихода следующей выборки.

3а время д1 дискретизации входного фильтрируемого процесса в цифровом фильтре осуществляется формирование произведений входной выборки на все возможные значения коэффициентов. В общем случае значения коэффициентов можно представить в виде ряда натуральных чисел от 0 до Q, где (,) = 2, à q — разрядность кода представления коэффициентов. Произведения формируются косвенно, т.е. не непосредственно путем умножения кода входной выборки на коды коэффициентов.

Произведения кода входной выборки на нечетные коэффициенты формируются во втором накапливающем сумматоре 3 путем потактного прибавления к коду выборки удвоенного значения кода, поступающего во второй накапливающий сумматор 3 через второй информационный вход первого мультиплексора 2. В результате во втором накапливающем сумматоре 3 образуются коды. после поступления кода входной выборки— код соответствующий парному произведению входной выборки на коэффициент 1, после суммирования данного кода с удвоенным значением кода входной выборки — код соответствующий парному произведению входной выборки на коэффициент 3 и т.д.

Таким образом, половина парных произведений получается путем выполнения такого же количества более простых и более 30 ,быстродействующих операций суммирования во втором накапливающем сумматоре 3.

Коды парных произведений по мере их формирования поступают с выхода второго накапливающего сумматора 3 через первый блок 4 элементов И в первый блок 10 памяти для запоминания произведений кода входной выборки на нечетные коэффициенты и на информационный вход второго регистра 5 сдвига. Код, поступивший на параллельный информационный вход второго ре- 4п гистра 5 сдвига потактно сдвигается по разрядной сетке, т.е. с каждым тактом осуществляется сдвиг кода, который можно интерпретировать, .как выполнение операции умножения на число 2, где j — число тактов сдвига. На фиг. 2 представлена последова- 45 тельность формирования парных произведений входной выборки х; на коэффициент фильтрации. Вторая половина парных произведений получается путем выполнения операций сдвига кодов по разрядной сетке

50 второго регистра 5 сдвига. При этом операции, выполняемые на втором накапливающем сумматоре 3 и во втором регистре 5 сдвига, могут выполняться одновременно.

С выхода второго регистра 5 сдвига код чисел, соответствующих парным произведени.- 55 ям кода выборки на четные коэффициенты, записывается через второй блок 6 элементов И во второй блок 7 памяти. В первом и втором блоках 10 и 7 памяти накаплива.ются парные произведения входных выборок на коэффициенты фильтрации. При помощи блока 11 синхронизации осуществляется считывание парных произведений из первого и второго блоков 10 и 7 памяти через второй мультиплексор 8 в первый накапливающий сумматор 9, в котором осуществляется суммирование парных произведений для получения очередного отсчета свертки. Для повторной фильтрации одной и той же реализации входного сигнала не требуется выполнение дополнительных операций умножения, необходимо лишь изменить при помощи первого и второго таймеров 13 и 14 режимы управления первым и вторым блокам и 10 и 7 памяти.

Первый и второй таймеры 13 и 14 осуществляют также согласование во времени процедур вычисления (формирования) парных произведений и перезаписн парных произведений из второго накапливающего сумматора 3 во второй регистр сдвига 5.

В известном фильтре повышение быстродействия достигается лишь за счет того, что устраняется избыточность при повторных умножениях одного значенч.". выборки (числа) на одинаковые значению коэффициенты, то в предлагаемом устройстве повышение быстродействия достигается и за счет устранения избыточности при выполнении операции умножения — произведение, полученное в предыдущем такте, используется как исходное число для формирования произведения в настоящем такте. Кроме того, предусматривается возможность одновременного формирования двух произведений (произведения на нечетный и четный коэффициенты).

На формирование N произведений входного отсчета на массив коэффициентов требуется

Nty = 0,5Nt + 0,5Nt, где tz„время, требуемое на выполнение операции умножения; — время, требуемое на выполнение операции суммирования;

1ед время, требуемое на выполнение операции сдвига при последовательном формировании произведений, а при параллельном

Ntvw = 0,5N jt, 1 „ или в среднем на одну операцию умножения

ty — — 0,5(t + t ) и

t = 0,5 пах ft, t J соответственно.

Практически, как показали испытания, среднее время на выполнение операции умножения определяется

0,5(t + t ) > t > 0,5 max ft t f

Таким образом, по сравнению с известным фильтром операции умножения (как наиболее трудбемкие) заменяются в два раP

1146798

П за меньшим количеством более быстродействующих операций суммирования и таким же количеством сверхбыстродействующих (особенно при использовании приборов с зарядовой связью) операций сдвига по разрядной сетке. Кроме того, устройство позволяет совмещать во времени выполнение этих операций. При использовании данного устройства в системах многоканальной фильтрации, получаемые устройством коды путем соответствующих накоплений можно использовать для осуществления многополосовой фильтрации. Промежуточные результаты с выхода фильтра могут регистрироваться в любых устройствах памяти с произвольным доступом к информации. Дополнительная эффективность от использования в многоканальных устройствах фильтрации прямо пропорциональна количеству каналов.

Использование предлагаемого устройства позволяет существенно повысить быстродей о ствие цифровых фильтров без ограничения, накладываемого на вид частотной характеристики.

1146798 (cZ-y) Х

5х„ т

Z 5х„

2х

2 УХ;"- Z (2K-1 / Х(. ° . °

22 5х, ... 22(zK Kll)XL L...

2 "/, 2 5Х1

5х„... 2 (2к->)Х 2 Зх фиг. 2

Составитель А. Осипович

Редактор Н. Яцола Техред И. Верес Корректор М. Самборская

Заказ 1379/43 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )K — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4