Устройство для подсчета количества единиц

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ПОДСЧЕТА КОЛИЧЕСТВА ЕДИНЩ, содержащее входной и выходной регистры, преобразователи двоичного кода в код количества единиц, суммирующие узлы, каждый из которых содержит комбинационный сумматор, причем входы преобразователей двоичного кода в код количества единиц соединены с выходами соответствующих групп разрядов входного регистра, отличающееся тем, что, с целью расширения функциональных возможностей за счет организации подсчета количества единиц в различных группах заданной длины, в каждый суммирующий узел введены два коммутатора, 1фичем первая и вторая группы входов комбинационного сумматора i-ro суммирующего узла первого яруса соединены с выходами

СОЮЗ С08ЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

1 у G 06 F 7/50

Ц.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3564157/24-24 (22) 16. 03. 83 (46) 07.04.85. Бюл. В 13 (72) С.С. Букатин и Е.С. Фетюкова (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 450160, кл. С 06 F 5/02, 1972.

Заявка Франции Ф 2454136, кл. G 06 F 7/50, опублик. 1980. (54) (57) УСТРОЙСТВО ДЛЯ ПОДСЧЕТА

КОЛИЧЕСТВА ЕДИНИЦ, содержащее входной и выходной регистры, преобразователи двоичного кода в код количества единиц, суммирующие узлы, каждый из которых содержит комбинационный сумматор, причем входы преобразователей двоичного кода в код количества единиц соединены с выходами соответствующих групп разрядов входного регистра, о т л и ч а ющ е е с я тем, что, с целью расширения функциональных возможностей за счет организации подсчета количества единиц в. различных группах заданной длины, в каздый суммирующий узел введены два коммутатора, причем первая и вторая группы входов комбинационного сумматора i-го суммирующего узла первого яруса

„„SU„„1149246 А соединены с выходами (2i-1)-ro u

2i-го преобразователей двоичного кода в код количества единиц соответственно (i = 1, ..., m/2 m— количество групп разрядов входного регистра), в каждом суммирующем узле первая и вторая группы информационных входов первого коммутатора соединены с первой группой входов комбинационного сумматора и шиной значения "О" устройства соответственно, первая и вторая группы информационных. входов второго коммутатора соединены с выходами и второй группой входов комбина- д ционного сумматора соответственно, первая и вторая группы входов комбинационного сумматора j-го суммирующего узла К-го яруса (К = 2, 8og m j = 1 2ао - ) соединены с выходами вторых коимутаторов (2j-1)-го и 2j-го суммирующих узлов (К-1)-го яруса, выходы 0ииий первых коммутаторов всех суммирую- ф щих узлов и выход второго коммутатора (fog > m)-ro яруса соединены у р с входами выходного регистра, уп- р равляющие входы коимутаторов Х-го яруса (Ф = 1, ..., fog а) соединены с й-м входом настройки устройства.

1 i 49246

15

40

55

Изобретение относится к вычислительной технике и предназначено для подсчета количества единиц в двоичных числах.

Целью изобретения является расширение функциональных возможностей за счет организации подсчета количества единиц в различных группах заданной длины.

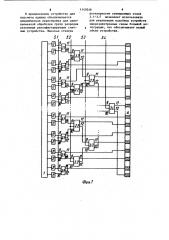

На фиг. 1 приведена структурная схема устройства для подсчета количества единиц; на фиг. 2 — структурная схема суммирующего узла.

Устройство для подсчета количества единиц содержит входной регистр

1, преобразователи 2 двоичного кода в код количества единиц, суммирующие узлы З.t-З.L, выходной ре- гистр 4, управляющие входы 5.1

5.Ь.

Суммирующий узел включает комбинационный сумматор 6, первый коммутатор 7, второй коммутатор 8, вход

9 первого слагаемого, вход 10 второго слагаемого, выходы 11 и 12 суммирующего узла.

Устройство работает следующим образом.

На входной регистр 1 (фиг. 1) помещается двоичное число, в котором (или в заданных группах которо" го) требуется подсчитать количество единиц. С выходов входного регистра 1 информация поступает на входы преобразователей 2 двоичного кода в код количества единиц, с выходов которых полученные коды количества единиц поступают на суммирующие узлы 3.1 первого яруса.

Результат, полученный на выходе

12 суммирующего узла 3.7. 2-го яруса, является одним из слагаемых для суммирующего узла 3(0+1) Kro яруса, где К = 2, ..., log> m, При требоВании формирования результирующих сумм единиц в группах заданной длины только в младших разрядах аналогичных групп разрядов выходного регистра 4 минимальная разрядность группы определяется выражением пмин 7 log> N, где п«минимальная разрядность группы; М вЂ” разрядность входного регистра 1, Группы, в которых одновременно подсчитывается количество единиц, должны быть равной разрядности кратной степени два. Число преобразователей 2 двоичного кода в код количества единиц выбирается и равным „ = m. мии

Разрядность каждого суммирующего узла 3.9 6-ro яруса определяется как 1 + log 2 nìèн . а их количество как

N nìÄÄ 2

Суммирующий узел 3.1 с номером (фиг. 2) принимает по входам 9 и

10 информацию с выходов 12 суммирующих узлов 3.(t — 1) или с выходов преобразователей 2 двоичного кода в код количества единиц для

1 с номерами (2j — 1) и 2j соответственно. Информация с входа

9 поступает на первую группу информационных входов первого коммутатора 7, имеющего разрядность, равную разрядности суммирующего узла

3.1, и первую группу входов комбинационного сумматора 6, Информация с входа 10 поступает на первую группу информационных входов второго коммутатора 8 и на вторую группу входов комбинационного сумматора 6. Сумма, сформированная на выходах комбинационного сумматора 6, поступает на вторую группу информационных входов второго коммутатора 8. Таким образом, при разрешающем потенциале 1" на управляющем входе 5.3 к выходам 11 и 12 суммирующего узла подключаются соответственно вторые входы первого и второго коммутаторов 7 и 8.

Для получения на выходе 11, соединенного с соответствующими разрядами выходного регистра 4, нулевой информации при разрешающем потекциале на управляющем входе 5.1: вторая группа информационных входов соединена с шиной значения "0" устройства..

При отсутствии разрешающего потенциала на управляющем входе 5.( на выходы 11 и t2 суммирующего узла поступает информация с входов первого и второго слагаемых соответственно.

Для формирования в выходном регистре 4 суммы единиц в группах по 2 и„„„„ разрядов (а = О, 1,... ..., log < m) необходимо на все ярусы, для которых 1й а, подать разрешающий потенциал на их управляющие входы 5.Р

В предлагаемом устройстве для подсчета единиц обеспечивается динамическая перестройка для одновременной обработки групп разрядов различные реконфигурируемые счетные устройства. Высокая степень

t349246

Регулярности суммирующих узлов

3. 1-3. позволяет использовать для реализации подобных устройств микроэлектронные схемы больвой интеграции, что обеспечивает малый объем устройства.

1149246

Составитель С. Букетик

Редактор Т. Кугрыиева Техред С.Иигунова

Корректор В. Гирняк

Филиал ППП "Патент", r. Уигород, ул. Проектная, 4

Заказ 1894/34 Тирам 710 Подписное

ВКИИПИ Государственного коиитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауаская наб., д. 4/5