Одноразрядный двоичный сумматор

Иллюстрации

Показать всеРеферат

ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУШ&ТОр, содержащий узел формирования СУ1ФШ и узел формирования переноса , причем узел формирования суммы содержит НДП-транзисторы р-типа с первого по пятый и первый ЬЩП-траизистор п-типа, а узел формирования переноса содержит ЦЦП-траизисторы р-типа с шестого по десятый и второй ВДП-транзисторы л-типа, затворы -первого, второго и третьего ЬЩПтранзистора р-типа соединены соответственно с входами первого, второго и третьего слагаемых сумматора, сток первого ОДП-транзистора р-типа соедаснен с истоком второго ЩП-транзистора р-типа, сток которого соединен со стоком третьего 1Щ1транзистора р-типа, со стоком первого МДП-транзистора п-типа и подключен к инверсному выходу переноса сумматора, исток третьего ВДП-транзистора р-типа соединен со стокаьш четвертого и пятого ОДПтранзисторов р-типа, истоки которых соединены с истоком первого ВДП-транзистора р-типа, а затворы соединены соответственно с входами первого и второго слагаемых сумматора , сток шестого МДП-транзистора р-типа соединен со стоком седьмого НДП-транзнстора р-типа и с истоком восьмого ВДП-транзистора р-типа, затвор которого соединен с входом первого слагаемого .сумматора, а сток подключен к стоку девятого МДП-транзистора р-типа и второго МДП-транзистора п-типа и соединен с инверсным выходом суммы сумматора, затворы седьмого и восьмого МЦП-транзисторов р-типа соединены соответственно с входами второго и первого слагаемых сумматора, исток седьмого i ВДП-транзистора р-типа соедийен (Л с истоком девятого и со стоком десятого ВДП-транзисторов р-типа, затвор шестого ВДП-транзистора р-типа соединен с затвором девятого НЦП-транзистора .р-типа и подключен к стоку второго ВДП-транзистора р-типа, затвор десятого ВДП-транзистора р-типа соединен с входом 4i третьего слагаемого сумматора, а СО исток соединен с истоком шестого ч to ВДП-транзистора р-типа, отли ( чающийся тем, что, с целью со упрощения его конструкции, он содержит одиннадцатый и двенадцатый ВДП-транзисторы р-типа, причем затвор одиннадцатого ВДП-транзистора Р-типа соединен с затвором первого ЩП-тpaнзиcтopa п-типа и подключен к первому входу синхронизации сумматора , исток соединен с истоком первого ВДП-транзистора р-тйпа, а сток подключен к шине питания сумматора, затвор двенадцатого ВДПтранзистора р-типа соединен с затво

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1149249 А

q g G 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ГЮ ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 3661336/24-24 (22) 05. 11. 83 (46) 07.04,85. Бюл. ll 13 (72) С.В. Быков, Л.Н. Корягин, О.И. Гусаков н А.А . Эзерин (53) 681.325.5(088.8) (56) 1. Авторское свидетельство СССР

Ф 943712, кл. 6 06 F 7/50, 1980.

2. Авторское свидетельство СССР

В 1034031, кл. 6 06 Р 7/50, l980 (прототип) . (54) (57) одноРАзРядный двоичный

СУММАТОР, содержащий узел формирования суммы и узел формирования переноса, причем узел формирования суммы содержит МДП-транзисторы р-типа с первого по пятый и первый МДП-тран.зистор п-типа, а узел формирования переноса содержит ФЩП-транзисторы р -типа с шестого по десятый и второй 2ЩП-транзисторы п--типа, затворы

-первого, второго и третьего МДПтранзистора р«тина соединены соответственно с входами первого, второго и третьего слагаемых сумматора, сток первого МДП-транзистора р-типа соединен с истоком второго МДП-транзистора Р-типа, сток которого соединен со стоком третьего 1ЯП транзистора р-типа, со стоком первого МДП-транзистора и -типа и подключен к инверсному выходу переноса сумматора, исток третьего

МДП-транзистора р-типа соединен со стоками четвертого и пятого МДПтранзисторов р-типа, истоки которых соединены с истоком первого

МДП-транзистора р-типа, а затворы соединены соответственно с входами первого и второго слагаемых сумматора, сток шестого МДП-транзистора р -типа соединен со стоком седьмого

МДП-транзистора р -типа и с истоком восьмого МДП-транзистора р- типа, затвор которого соединен с входом первого слагаемого сумматора, а сток подключен к стоку девятого МДП-транзистора р òèïà и второго МДП-транзистора и -типа и соединен с инверсным выходом суммы сумматора, затворы седьмого и восьмого МДП-транзисторов р-типа соединены соответственно с входами второго и первого слагаемых сумматора, исток седьмого д

МДП-транзистора р-типа соединен с истоком девятого и со стоком десятого МДП-транзисторов р -типа, затвор шестого МДП-транзистора р-ти- С па соединен с затвором девятого

МДП-транзистора .р -типа и подключен к стоку второго МДП-транзистора р-типа, затвор десятого ФЩП-транзистора р -типа соединен с входом третьего слагаемого сумматора, а исток соединен с истоком шестого

МДП-транзистора р-типа, о т л ич а ю шийся тем, что, с целью упрощения его конструкции, он содержит одиннадцатый и двенадцатый

МДП-транзисторы р-типа, причем затвор одиннадцатого МДП-транзистора р-типа соединен с затвором первого

МПП-транзистора и-типа н подключен к первому входу синхронизации сумматора, исток соединен с истоком первого МДП-транзистора Р-типа, а сток подключен к шине питания сумматора, затвор двенадцатого МДПтранзистора р-типа соединен с затво1149249

1 ром второго МДП-транзистора и -типа и подключен к второму входу синхронизации сумматора, сток соединен с шиной питания сумматора, а исток

Ф

Изобретение относится к вычислительной технике и может быть использовано при создании больших интегральных схем (БИС) обработки цифровой информации.

5Известен сумматор на ИДП-транзисторах, содержащий узел формирования суммы, содержащий восемь МДП-транзисторов и -типа и восемь МДП-транзисторов р -типа, и узел формирова- 10 ния переноса, содержащий два ИДПтранзистора и -типа и два МДП-транзистора р -типа 1 ).

Недостатком данного сумматора является сложность конструкции, выражающаяся в большом количестве

МДП-транзисторов, используемых в сумматоре.

Наиболее близким к предлагаемому по технической сущности является од" норазрядный двоичный сумматор, содержащий узел формирования суммы и узел формирования переноса, причем узел формирования суммы содержит

ЬДП-транзисторы р -типа с первого по пятый и первый МДП-транзистор

h -типа, а узел формирования переноса содержит МДП-транзисторы р -типа с шестого по десятый и второй

МДП-транзистор и-типа, затворы первого, второго и третьего МДП-транзисторов р -типа соединены соответственно с входами первого, второго и третьего слагаемых сумматора, сток первого NQH-транзистора р-типа соединен с истоком второго МДП-тран35 зистора р-типа, сток которого соединен со стоком третьего МДП-транзистора р-типа, со стоком первого

ИДП-транзистора и--типа и подключен

40 к инверсному выходу переноса сумматора, исток третьего МДП-транзистора . р -типа соединен со стоками четвертого и пятого ИДП-транзисторов р -типа, истоки которых соединены с истоком первого МДП-транзистора соединен с истоком шестого 1ЩП-транзистора р -типа, стоки первого и второго МДП-транзисторов и -типа соединены с нулевой шиной сумматора. р.— типа, а затворы соединены соответственно с входами первого и второго слагаемых сумматора, сток шестого ИДП-транзистора р -типа соединен со стоком седьмого M@II-транзистора р -типа и с истоком восьмого МДП-транзистора р-типа, затвор которого соединен с входом первого слагаемого сумматора, а сток подключен к стоку девятого МДП-транзистора р -типа и второго МДП- транзистора -типа и соединен с инверсным выходом суммы сумматора, затворы седьмого и восьмого ИДПтранзисторов р-типа соединены соответственно с входами второго и первого слагаемых сумматора, исток седьмого ИДП-транзистора р-типа соединен с истоком девятого и со стоком десятого МДП-транзисторов р -типа, затвор шестого 1ЯПтранзистора р -типа соединен с затвором девятого ИДП-транзистора р -типа и подключен к стоку второго

МДП-транзистора р -типа, затвор десятого МДП-транзистора р -типа соединен с входом третьего слагаемого сумматора, а исток соединен с истоком шестого ИДП-транзистора р -типа, сумматор содержит также дополнительно МДП-транзисторы и -типа с третьего по десятый P2g.

Недостатком известного сумматора является сложность конструкции, выражающаяся в большом количестве использованных МДП-транзисторов, Цель изобретения — упрощение конструкции одноразрядного двоичного сумматора.

Поставленная цель достигается тем, что одноразрядный двоичный сумматор, содержащий узел формирования суммы и узел формирования переноса, причем узел формирования суммы содержит МДП-транзисторы р -типа с первого по пятый и первый

МДП-транзистор и -типа, а узел формирования переноса содержит МДПтранзисторы р-типа с шестого по десятый и второй МДП-транзисторы

q -типа, затворы первого, второго и третьего МДП-транзисторов р -типа соединены соответственно с входами первого, второго н третьего слагаемых сумматора, сток первого 1ЩПтранзистора р -типа соединен с исто- 10 ком второго МДП-транзистора р -типа, сток которого соединен со стоком третьего МДП-транзистора р -типа, со стоком первого ЬЩП-транзистора ь -типа и подключен к инверсному вы- 15 ходу переноса сумматора, исток третьего ИДП-транзистора р -типа соединен со стоками четвертого и пятого МДП-транзисторов р-типа, истоки которых соединены с истоком 20 первого ЬЩП-транзистора р -типа, а затворы соединены соответственно с входами первого и второго слагае.мых сумматора, сток шестого МДПтранзистора р-типа соединен со 25 стоком седьмого МДП-транзистора р -типа и с истоком восьмого ИППтранзистора р"типа, затвор которого соединен с входом первого слагаемого сумматора, а сток подключен З0 к стоку девятого МДП-транзистора р -типа и второго ИДП-транзистора -типа и соединен с инверсным выходом суммы сумматора, затворы седьмого и восьмого МДП-транзистора

35 р -типа соединены соответственно с входами второго и первого слагаемых сумматора, исток седьмого

МДП-транзистора р-типа соединен с истоком девятого и со стоком деся- 40 того МДП-транзисторов р --типа, затвор шестого МДП-транзистора р -типа соединен с затвором девятого ИДП-транзистора р-типа и подключен к стоку второго МДП-транзис- 45 тора р-типа, затвор десятого

ИДП-транзистора Р-типа соединен с входом третьего слагаемого сумматора, а исток соединен .с истоком шестого МДП-транзистора р-типа

50 сумматор содержит одиннадцатый и двенадцатый ИДП-транзисторы р-типа, причем затвор одиннадцатого

1149249 1

МДП-транзистора р -типа соединен с затвором первого ИДП-транзистора ь -типа и подключен к первому входу синхронизации сумматора, исток соединен с истоком первого МДП-транзистора р -типа, а сток подключен к шине питания сумматора, затвор двенадцатого MfQI-транзистора р -типа соединен с затвором второго МДПтранзистора и --типа и подключен к второму входу синхронизации сумматора, сток соединен с шиной питания сумматора, а .исток — с истоком шестого МДП-транзистора. р -типа, стоки первого и второго МДП-транзисторов и -типа соединены с нулевой шиной сумматора.

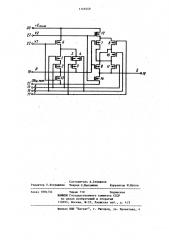

На чертеже представлена принципиальная схема одноразрядного двоичного сумматора.

Сумматор содержит МДП-транзисторы

1-12 р --типа, 1ЩП-транзисторы 13 и 14 и -типа, входы слагаемых 15-17, выход 18 переноса, выход 19 суммы, шину 20 питания, нулевую шину 21, а также первый и второй входы 22 и 23 синхронизации.

Сумматор работает следукнцим образом.

На вход 22 подается сигнал уровня логической "1", при этом на выходе 15 и на затворах транзисторов

7 и 9 накапливается отрицательный заряд. Далее подаются сигналы слагаемых на входы 15-17, и узел формирования переноса на транзисторах

1-б и 13 вырабатывает инверсный сигнал переноса на выходе 18. На вход 22 при этом подается сигнал уровня логического "0". Далее на вход 23 поступает сигнал уровня логической "1" и на выходе 19 накапливается отрицательный потенциал.

Затем на вход 23 подается сигнал логического "0", и узел форьмрования суммы на транзисторах 7-12 вырабатывает инверсное значение суммы на выходе 19.

По сравнению с известным предлагаемый сумматор содержит на 30Х меньше ИДП-транзисторов, что вызывает также повышение надежности сумматора.

1149249

22

Заказ 1894/34

27

71

16

Составитель А.Стеиаиов

Редактор Т.Кугрыиева Техред С.Mиrуиeea . . Корректор И.Иуска

Тираж 710 Подиисиое

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауиккая наб., д. 4/5

Филиал ППИ "Патент", г. Ужгород, ул. Проектная, 4