Цифровой анализатор спектра

Иллюстрации

Показать всеРеферат

ЦИФРОВОЙ АНАЛИЗАТОР СПЕКТРА, содержащий преобразователь частоты, вход которого является информационным входом анализатора, первый и второй цифровые фильтры, умножитель на весовую функцию,, выход которого подключен к информационному входу блока вычисления быстрого преобразования Фурье, информационный выход которого подключен к входу квадратичного детектора , отличающийся тем, что, с целью упрощения анализатора, он содержит умножитель и блок постоянной памяти коэффициентов, информационный выход которого подключен к первому входу умножителя, выход которого является информационньш выходом анализатора, а выход квадратичного детектора подключен к второму входу умножителя, причем первый и второй Вход цифровые фильтры содержат Р узлов фильтрации (где Р - отношение всей полосы к полосе анализа), каждый из которых содержит М регистров и М сумматоров (где М - порядок фильтра), при этом выход i-го (, М-1) сумматора 1-го (i 1,P) узла фильтрагщи подключен к первому входу (i+1)-ro сумматора и информационному входу (i + O-ro регистра, информационный выход которого подключен к второму входу (f+O-ro сумматора, первьй вход первого сумматора подключен к информационному выходу первого регистра, а второй вход первого сумматора К-го (,Р) узла фильтрации соединен с (Л информационным входом первого регистра К-го узла фильтрации и подключен к вькоду М-го сумматора (К-1)-го узла фильтрации, при этом вторые входы сумматоров первых узлов фильтрации первого и второго цифровых фильтров соединены с информационными входами первых регистров первых узлов фильтра JI ции соответственно первого и второго цифровых фильтров и подключены к выЮ ходам соответственно реальной и мнимой частей числа преобразователя частоты, а выходы М-х сумматоров Р-х узлов фильтрации первого и второго цифровых фильтров подключены к входам соответственно реальной и мнимой частей числа умножителя на весовую функцию.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

4(50 G 06 F 15/332

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ".:

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3491479/24-24 (22) 08.09.82 (46) 07.04.85 Бюл. У 13 (72) И.Е.Петров, Л.В.Сабаев, Е.К.Костецкая и Т.Н.Федоровская (53) 681.32(088.8) (56) 1. Рабинер Л., Гоулд Б. Теория ,и применение цифровой обработки сигналов, М,, "Мир", 1978, с. 7128, 2. Применение цифровой обработки сигналов. Под ред, З.Оппенгейма. М., "Мир", 1982, с. 79 (прототип). (54)(57) ЦИФРОВОЙ АНАЛИЗАТОР СПЕКТРА, содержащий преобразователь частоты, вход которого является информационным входом анализатора, первый и второй цифровые фильтры, умножитель на весовую функцию,. выход которого подключен к информационному входу блока вычисления быстрого преобразования

Фурье, информационный выход которого подключен к входу квадратичного детектора, отличающийся тем, что, с целью упрощения анализатора, он содержит умножитель и блок постоянной памяти коэффициентов, информационный выход которого подключен к первому входу умножителя, вьмод которого является информационным выходом анализатора, а выход квадратичного детектора подключен к второму входу умножителя, причем первый и второй цифровые фильтры содержат Р узлов фильтрации (где P — отношение всей полосы к полосе анализа), каждый из которых содержит М регистров и М сумматоров (где M — порядок фильтра), при этом выход 1 -го (= 1, М-1) сумматора 1 -го (1 1,Р) узла фильтрации подключен к первому входу (i +1)-го сумматора и информационному входу (1+1)-го регистра, информационный выход которого подключен к второму вхоI ду (+1)-го сумматора, первый вход первого сумматора подключен к информационному выходу первого регистра, а второй вход первого сумматора К-го (К=2,P) узла фильтрации соединен с информационньм входом первого региот Щ ра К-ro узла фильтрации и подключен к выходу М"ro сумматора (К-1)-го узла C фильтрации, при этом вторые входы сумматоров первых узлов фильтрации первого и второго цифровых фильтров соединены с информационными входами " первых регистров первых узлов фильтра ции соответственно первого и второго цифровых фильтров и подключены к выходам соответственно реальной и мнимой частей числа преобразователя частоты, а выходы М-х сумматоров P-x узлов фильтрации первого и второго цифровых фильтров подключены к входам соответственно реальной и мнимой частей числа умножителя на весовую функцию.

1149274

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре, осуществляющей спектральную обработку электрических сигналов в реальном масштабе времени. 5

Известно устройство, содержащее блок преобразования Фурье, два выхода которого через квадратары соединены с входом сумматора, выход которого соединен с линейным или нелиней- 10 ным регистратором (1), Недостаток устройства — недостаточная разрешающая способность, Наиболее близким по технической сущности к предлагаемому является устройство, содержащее преобразователь частоты, вход которого является информационным входом анализатора, два цифровых фильтра, состоящие из умножителей, накапливающих суммато- 20 ров и коммутаторов, умнажитель на весовую функцию, выход которога подключен к входу блока быстрого преобразования Фурье, выход которого подключен к входу квадратичного детектора (2) .

Недостатком известного устройства является его сложность из-за использования большого числа умножителей и накапливающих сумматоров. ЗО

Цель изобретения — упрощение анализатора спектра, Поставленная цель достигается тем, чта в анализатор спектра, содержащий преобразователь частоты, вход которо-З га является информационным входом анализатора, первый и второй цифровые фильтры, умнажитель на весовую функцию, выход которого подключен к информационному входу блока вычисле- о ния быстрого преобразования Фурье, информационный выход которого подключен к входу квадратичного детектора, отличающийся тем, что с целью упрощения анализатора, введены умножитель и блок постоянной памяти коэффициентов, информационный выход которого подключен к первому входу умнажителя, выход которого является информационным выходом анали- go затора, а выход квадратичного детектора подключен к второму входу умнажителя, причсм первый и второй цифровые фильтры содержат P узлов фильтрации (где P — отношение всей полосы к полосе анализа), каждый из которых содержит М регистраторов и И сумматоров (где M — гарядак Фильтра), при этом выход j -га (i =1 M-f) сучмтора

j -го (< =1,Р) узла фильтрации подключен к первому входу (+1)-го сумматора и информационному входу (+1)-ro регистра, информационный выход которого подключен к второму входу (1+1)— га сумматора, первый вход первого сумматора — к информационному выходу первого регистра, а второй вход первого сумматора K-ro (К=2,Р) узла фильтрации соединен с информационным входам первого регистра К-го узла фильтрации и подключен к выходу И-го сумматора (К-1) -го узла фильтрации, при этом вторые входы сумматоров первых узлов фильтрации первого и второго цифровых фильтров соединены с информационными входами первых регистров первых узлов фильтрации соответственна первого и второго цифровых фильтров и чадключень к выходам соответственно реальной и мнимой частей числа преобразователя частоты, а выходы И-х сумматоров Р-х узлов фильтрации первого и второго цифровых фильтров — к входам соответственно реальной и мнимой частей числа умножителя на весовую функцию.

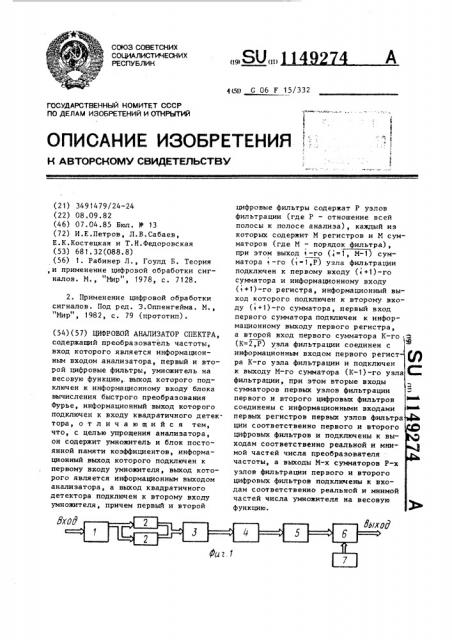

На фиг. 1 представлена блок-схема анализатора спектра; на фиг. 2 структурная схема цифрового фильтра.

Ус ройство состоит из последовател . с соединенных между собой преобразава.еля 1 частоты, двух цифровых фильтров 2, умножителя 3 на весовую функцию, блока 4 вычисления быстрого преобразования Фурье, квадратичного детектора 5, умножителя б и блока 7 постоянной памяти коэффициентов, Цифровой фильтр 2 (фиг. 2) состоит иэ Р последовательна соединенных узлов 8 фильтрации, каждый из которых содержит M сумматоров 9 и столько же регистров 10 задержки.

Устройство работает следующим образом.

При поступлении на вход устройства с тактом Т входных комплексных выборок, они поступают на информационный вход преобразователя 1 частоты, осуществляющего перенос спектра входного процесса в область нижних частот по следующему алгоритму

«(е1=, (е1 е """ где х „(е), х (е) — комплексные выборки соответственно

11492 на входе и на выходе преобразователя частоты; е — текущий номер выработки;

4) — центральная частота зоны анализа;

И !

1О

Т „, Рк — соответственно такт и частота квантования входного комплексного процесса.

С выхода преобразователя 1 частоты косинусная и синусная составляющие поступают с тактом Т соответственно на входы первого и второго цифровых фильтров 2.

Число Р узлов 8 фильтрации зависит от отношения величины эоны анализа к полной полосе. Число М сумматоров 9 и связанных-с ними регистров

10 задержки в каждом узле 8 фильтрации зависит от порядкового номера узла 8 фильтрации и от требуемой формы амплитудно-частотной характеристики (АЧХ) цифрового фильтра 2 АЧХ одного узла 8 фильтрации определяется выражением:

М, Мр

H +itl = 2 со 7 f l „ где р — номер узла фильтрации;

Mp — число сумматоров в р-м узле фильтрации;

Š— текущая частота;

Г „ — частота поступления инфор" р мации на вход р-го узла фильтрации; ! 2Р 1 40

F =2F F - —;Т - — F вк,P Р> Р T P F вх.Р 2Р-.Т

P k

М последовательно соединенных между собой сумматоров 9 с регистрами

10 задержки позволяют сузить полосу 45 частот входного процесса и получить малое значение коэффициента передачи узла 8 фильтрации на частотах, близких к частоте Рвх р/2. Благодаря этому съем информаций с выхода р-ro ys- 50 ла 8 фильтрации можно производить с частотой, вдвое меньшей, чем F „

Таким образом, съем информации с вх,р. р-ro узла 8 фильтрации осуществляется в 2 раэ реже, чем поступление р входной информации на вход первого узла 8 фильтрации (Тр=2 Тк). АЧХ

ip цифрового фильтра, имеющего P прсле74 4 довательно соединенных узлов фильтрации, определяется иэ соотношения

Мр к.f ..2P Мр

Н(1) = П 2 cog

P=! к

Поточная органиэация структуры цифрового фильтра обеспечивает высокое быстродействие, определяемое тактом поступления входной информации на первый сумматор, осуществляющий сложение двух входных отсчетов, один из которых непосредственно поступает на первый вход сумматора, а другой — с задержкой íà Tk на регистре задержки на второй вход. Такт работы последующих узлов 8 фильтрации может быть выбран соответственно ниже в

2 раэ, так как частота поступлер-! ния входной информации последовательно от одного узла 8 фильтрации к другому уменьшается в два раза.

Разреженная по времени информация с выходов цифровых фильтров поступает на входы умножителя 3, работающего по алгоритму (n)= x(n) С (), где С(п) — действительные выборки из весовой функции, что обеспечивает получение требуемой формы АЧХ фильтров спектроанализатора.

С выхода умножителя 3 взвешенные выборки поступают на вход блока 4 вычисления быстрого преобразования

Фурье, реализующего алгоритмы я-! 2

) N""к

Ц (и) = >("(н) е ! =0

) где п и К вЂ” номер соответственно входных и выходных отсчетов;

И вЂ” количество отсчетов, поступающих на вход блока 4; у (k) — комплексная выборка на выходе К-ro фильтра.

С выходов блока 4 выходные отсчеты у (k) последовательно во времени поступают на вход квадратичного детектора 5, реализующего следующий алгоритм

5(к) = где S(k) — значение огибающей на выходе К-ro фильтра.

5 .1- Я . Р(Ц, 9 З

70 10

Ри Z

Составитель А, Баранов

Редактор В.Данко Техред 3,Палий Корректор В . Гирняк

Заказ 1895/35 Тираж 710 Подпис но е

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4

С выхода квадратичного детектора

5 информация поступает на один из входов умножителя 6, осуществляющего выравнивание коэффициентов передачи в каждом фильтре по следующему алгоритму где R(k) — коэффициенты выравнивания, хранящиеся в блоке

7 постоянной памяти коэффициентов и поступающие на второй вход умножителя 6.

5 Введение умножителя и блока постоянной памяти в устройство, а также построение цифровых фильтров на основе простых узлов фильтрации позволяют значительно упростить устройство в случае, когда полоса анализа уже всей полосы.