Формирователь с тремя состояниями на выходе

Иллюстрации

Показать всеРеферат

ФОРМИРОВАТЕЛЬ С ТРЕМЯ СОСТОЯНИЯМИ НА ВЫХОДЕ, содержащий КМДПИнвертор, вход которого подключен к первому входу формирователя, два блокирующих п-канальных МДП-транзистора , истоки которых соединены с общей шиной, а затворы подключены к второму (блокирующему) входу формирователя , выходной биполярный п-р-п-транзистор , база которого соединена с6 стоком первого блокирующего транзистора, а коллектор подключен к шине питания, выходной п-канальный МДП-транзистор, затвор которого соединен со стоком второго блокирующего транзистора, исток подключен к общей шине, а сток соединен с эмиттером выходного биполярного п-р-п-транзистора и выходом формирователя, отличающийся тем, что, с целью повышения быстродействия , в него введены две пары КМДПтранзисторов , состоящих из ри п-канальных транзисторов, причем стоки первой пары КМДП-транзисторов подключены к базе биполярного транзистора, а истоки - к выходу инвертора, затвор р-канального транзистора первой пары КМДП-транзисторов соединен с вторым (блокирующим) входом формирователя, затвор п-канального транзистора этой же пары КМДПi транзисторов соединен с третьим входом формирователя, стоки второй пары КМДП (Л транзисторов подключены к затвору выходного п-канального КМДП-транзистора, а истоки - к первому входу формирователя , затворы ри п-канальных транзисторов второй пары КМДП-транзисторов подключены соответственно к затворам ри п-канальных транзисторов первой пары КМДП-транзисторов. 4 оо со Х)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

4(59 Н 03 К 19/00 а - «а

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ!

ОПИСАНИЕ ИЗОБРЕТЕНИЯ л

° ь х

М ASTOPGMOMY СВИДЕТЕЛЬСТВУ (21) 3539293/24-21 (22) 11.01.83 (46) 07.04.85. Бюл. № 13 (72) А. И. Радугин, В. А. Галенко, Б. И.,Каплан и Н. И. Отюцкий (53) 621.374.33 (088.8) (56) 1. Патент Японии № 56-33896, кл. Н 03 К 19/00, 1975.

2. Патент Японии № 56-7331, кл. Н 03 К 19/00, 1975.

3. Патент США № 4280065, кл. Н 03 К 19/00, 1972. (54) (57) ФОРМИРОВАТЕЛЬ С ТРЕМЯ

СОСТОЯНИЯМИ НА ВЫХОДЕ, содержащий КМДП-инвертор, вход которого подключен к первому входу форм и рователя, два блокирующих п-канальных МДП-транзистора, истоки которых соединены с общей шиной, а затворы подключены к второму (блокирующему) входу формирователя, выходной биполярный п — р — п-транзистор, база которого соединена сд стоком первого блокирующего транзистора, а коллектор подключен к шине питания, выходной п-канальный МДП-транзистор, затвор

„.Я0„„1149399 А которого соединен со стоком второго блокирующего транзистора, исток подключен к общей шине, а сток соединен с эмиттером выходного биполярного и — р — n-транзистора и выходом формирователя, отличающийся тем, что, с целью повышения быстродействия, в него введены две пары КМДПтранзисторов, состоящих из р- и и-канальных транзисторов, причем стоки первой пары КМДП-транзисторов подключены к базе биполярного транзистора, а истоки— к выходу инвертора, затвор р-канального транзистора первой пары КМДП-транзисторов соединен с вторым (блокирующим) входом формирователя, затвор и-канального транзистора этой же пары КМДПтранзисторов соединен с третьим входом @

Р формирователя, стоки второй пары КМДПтранзисторов подключены к затвору выходного и-канального КМДП-транзистора, а истоки — к первому входу формирователя, затворы р- и п-канальных транзисторов второй пары КМДП-транзисторов под- 3 ключены соответственно к затворам р- и и-канальных транзисторов первой пары

КМДП-транзисторов.

1149399

Изобретение относится к электронике, вычислительной технике и может быть использовано при создании больших интегральных схем на МДП приборах.

Известна преобразующая схема с тремя выходными состояниями на полевых транзисторах, содержащая входной элемент

ИЛИ-НЕ, инвертор и выходной формирователь, состоящий из пяти транзисторов (! ).

Известна также схема преобразования с трехуровневым выходным сигналом, содержащая входные элементы ИЛИ-НЕ, И-НЕ и выходной формирователь, состоящий из четырех транзисторов (2).

Недостатками преобразующих схем являются сложность выходных формирователей и малое быстродействие.

Наиболее близким к изобретению по технической сущности является формирователь с тремя состояниями, состоящий из

КМДМ-инвертора, двух логических схем, выполняющих функцию элементов ИЛИ-НЕ и состоящих из четырех дополняющих транзисторов каждая, выходных транзисторов— биполярного п — р — n и п-канального полевого, причем эмиттер выходного транзистора подключен к стоку полевого выходного транзистора и к выходу устройства, база подключена к выходу первой логической схемы, на входы которой подаются блокирующий и входной сигналы, коллектор подключен к шине питания, исток полевого выходного транзистора подключен к общей шине, а затвор — к выходу второй логической схемы, на входы которой подаются блокирующий сигнал и инвертированный входной сигнал с выхода инвертора (3).

Недостатками известной схемы являются ее сложность и малое быстродействие, так как управление выходными транзисторами осуществляется через два последовательно включенных р-канальных транзистора логических схем.

Цель изобретения — упрощение схемы и повышение быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее КМДП-инвертор, вход которого подключен к первому входу формирователя два блокирующих п-канальных МДП-транзистора, истоки которых соединены с общей шиной, а затворы подключены к второму (блокирующему) входу формирователя, выходной биполярный п — р — п-транзистор, база которого соединена со стоком первого блокирующего транзистора, а коллектор подключен к шине питания, выходной п-канальный МДП-транзистор, затвор которого соединен со стоком второго блокирующего транзистора, исток подключен к общей шине, а сток соединен с эмиттером выходного биполярного п — р — п транзистора и .выходом формирователя, введены две пары КМДП-транзисторов, состоящих из р- н п-канальных транзисторов, причем стойки первой пары КМДПтранзисторов подключены к базе биполярного транзистора, а истоки — к выходу инвертора, затвор р-канального транзистора первой пары КМДП-транзисторов соединен с вторым (блокирующим) входом формирователя, затвор п-канального транзистора этой же пары КМДП-транзисторов соединен с третьим входом формирователя стоки второй лары КМДП-транзисторов подключены к затвору выходного и-канального КМДП-транзистора, а истоки — к первому входу формирователя, затворы р- и п-канальных транзисторов второй пары КМДП транзисторов подключены соответственно к затворам р- и и-канальных транзисторов первой пары КМДП-тран5

15 зисторов.

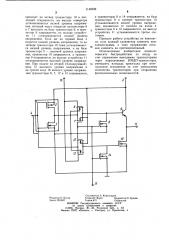

На чертеже представлена принципиальная электрическая схема формирователя с тремя состояниями на выходе.

Устройство содержит КМДП-ичвертор 1, выполненный на транзисторах 2 и 3, причем затворы транзисторов подключены к пер20 вому входу устройства 4, сток транзистора 2 подключен к шине 5 питания, а исток соединен со стоком транзистора 3 и являет25 ся выходом инвертора, подключенным к истокам первой пары КМДП-транзисторов транзисторы 6, 7, 12, 13 открываются.

Если теперь на первый вход 4 подается высокий уровень напряжения, то через открытые транзисторы 12 и 13 этот сигнал

6 и 7, стоки которых объединены и подключены к стоку первого блокирующего транзистора 8 и к базе биполярного и — р — птранзистора 9, коллектор которого подключен к шине 5 питания, а эмиттер соединен со стоком выходного и-канального

МДП транзистора 10 и подключен к выходу

35 устройства 1 1. Истоки второй пары КМДПтранзисторов 12 и 13 подключены к первому входу устройства 4, а их стоки объединены и подключены к затвору выходного п-канального МДП-транзистора 10 и к стоку второго блокирующего транзистора 14, затвор которого соединен с затворами рканальных транзисторов 7 и 12, с затвором транзистора 8 и подключен к второму входу устройства 15, затворы п-канальных транзисторов 6 и 13 подключены к третье45 му входу устройства 16, истоки транзисторов 3, 8, 14, 10 подключены к общей шине, подложки транзисторов 12 и 7 подключены к шине 5 питания, а подложки транзисторов 13 и 6 подключены к общей шине.

Устройство работает следующим образом.

При подаче на второй (блокирующий) вход 15 низкого уровня напряжения и на третий вход 16 высокого уровня напряжения транзисторы 8 и 14 закрываются, а

1149399

Составитель А. Комиссаров

Редактор О. Бугир Техред И. Верес

Заказ 1918/42 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 проходит на затвор транзистора 10 и последний открывается, нэ выходе инвертора устанавливается низкий уровень напряжения, который через открытые транзисторы 6 и 7 проходит на базу транзистора 9, и транзистор 9 закрывается, на выходе устройства 11 устанавливается низкий уровень напряжения. Если же на первый вход 4 подается низкий уровень напряжения, то на затворе транзистора 10 тоже устанавливается низкий уровень напряжения, а на базе транзистора 9 — высокий уровень напряжения, транзистор 10 закрывается, а транзистор 9 открывается, на выходе устройства 11 устанавливается высокий уровень напряжения. При подаче на второй (блокирующий) вход 15 высокого уровня напряжения и на третий вход 16 низкого уровня напряжения транзисторы 6, 7, 12 и 13 закрываются, а транзисторы 8 и 14 открываются, на базе транзистора 9 и затворе транзистора 10 устанавливаются низкие уровни напряжения, независимо от сигнала на входе 4, транзисторы 9 и 10 закрываются, на выходе устройства 11 устанавливается третье состояние.

Принцип работы устройства не изменится, если каждый транзистор заменить ком10 плементарным, а знак напряжения питания изменить на противоположный.

Использование изобретения позволит повысить быстродействие по входу за счет управления выходными транзисторами через параллельные КМДП-транзисторы, уменьшить площадь кристалла при интегральном исполнении за счет уменьшения количества транзисторов при сохранении функциональных возможностей.