Устройство для определения математического ожидания погрешности аналого-цифровых преобразователей

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ ПОГРЕШНОСТИ АНАЛОГО-ЦИФРОВЫХ ПРЕОБРАЗОВАТЕЛЕЙ, содержащее источник входного сигнала, выход которого соединен с первой выходной шиной и первым входом образцового аналого-цифрового преобразователя, второй вход которого соединен с входом линии задержки и второй выходной шиной, а выход - с первым входом блока сравнения кодов, второй вход которого соединен с выходом реверсивного счетчика, а первый выход - с первым входом реверсивного счетчика, второй вход которого соединен с первой входной шиной, третий вход - с входом линии задержки, а четвертый вход - с выходом генератора импульсов, входом делителя частоты и первым входом первого счетчика, выход которого соединен с первым входом блока памяти , первый триггер, первый вход которого соединен с шиной «Пуск, второй вход - с выходом второго счетчика, а выход - с первым входом первого элемента И, отличающееся тем, что, с целью повышения его точности и уменьшения времени поверки , в него введены блок суммирования, делитель на два, сумматор, вторая линия задержки , второй элемент И, второй триггер, первый вход которого соединен с выходом второго счетчика, а второй вход - с выходом второй линии задержки и вторым входом блока памяти, выход которого соединен с первым входом блока суммирования, второй вход которого соединен с выходом i первого счетчика, а выход через делитель на два - с первым входом сумматора, выход (Л которого соединен с третьей выходной шиной , а второй вход - с входом второго счетчика и выходом второго элемента И, первый вход которого соединен с выходом второго триггера, а второй вход - с вторым выходом блока сравнения кодов, первый выход которого соединен с вторым входом первого счетчика, третий вход которого соединен с выходом первого элемента И и входом первой линии задержки, 4 выход которой соединен с входом второй линии задержки, причем второй вход первого ) элемента И соединен с выходом делителя.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

4159 Н 03 М 1/10

: 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3553202/24-21 (22) 17.02.83 (46) 07.04.85. Бюл. № 13 (72) А. И. Заико (71) Уфимский ордена Ленина авиационный институт им. Серго Орджоникидзе (53) 681.325 (088.8) (56) 1. Авторское свидетельство СССР № 337932, кл. Н 03 К 13/02, 28.10.69.

2. Авторское свидетельство СССР № ?38149, кл. Н 03 К 13/02, 09.01.78. (54) (57) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ

ПОГРЕШНОСТИ АНАЛОГО-ЦИФРОВЫХ

ПРЕОБРАЗОВАТЕЛЕЙ, содержащее источник входного сигнала, выход которого соединен с первой выходной шиной и первым входом образцового аналого-цифрового преобразователя, второй вход которого соединен с входом линии задержки и второй выходной шиной, а выход — с первым входом блока сравнения кодов, второй вход которого соединен с выходом реверсивного счетчика, а первый выход — с первым входом реверсивного счетчика, второй вход которого соединен с первой входной шиной, третий вход — с входом линии задержки, а четвертый вход — с выходом генератора импульсов, входом делителя частоты и первым входом первого счетчика, выход кото„, (1„„1149407 д рого соединен с первым входом блока памяти, первый триггер, первый вход которого соединен с шиной «Пуск», второй вход— с выходом второго счетчика, а выход — с первым входом первого элемента И, отличающееся тем, что, с целью повышения его точности и уменьшения времени поверки, в него введены блок суммирования, делитель на два, сумматор, вторая линия задержки, второй элемент И, второй триггер, первый вход которого соединен с выходом второго счетчика, а второй вход — с выходом второй линии задержки и вторым входом блока памяти, выход которого соединен с первым входом блока суммирования, второй вход которого соединен с выходом первого счетчика, а выход через делитель на два — с первым входом сумматора, выход которого соединен с третьей выходной шиной, а второй вход — с входом второго счетчика и выходом второго элемента И, первый вход которого соединен с выходом второго триггера, а второй вход — с вторым выходом блока сравнения кодов, первый выход которого соединен с вторым входом первого счетчика, третий вход которого соединен с выходом первого элемента И и входом первой линии задержки, выход которой соединен с входом второй линии задержки, причем второй вход первого элемента И соединен с выходом делителя.

1149407

Изобретение относится к измерительной технике и может быть использовано для автоматической поверки аналого-цифровых преобразователей при произвольных случайных и детерминированных сигналах в различных условиях эксплуатации.

Известно .устройство для поверки аналого-цифровых преобразователей, содержащее источник входного сигнала, выход Которого соединен с первыми входами образцового и поверяемого аналого-цифровых 10 преобразователей и через умножитель частоты с первым входом вентиля пуска, вторым. входом связанного с выходом триггера пуска, первый вход которого подключен к выходу счетчика измерений, а второй вход—

15 к первому выходу переключателя, второй выход которого соединен с первым входом элемента ИЛИ, а вход через кнопку — с входной шиной устройства. Второй вход элемента ИЛИ соединен с выходом вентиля пуска и с входом первого делителя час- 20 тоты, выход которого подключен к входу счетчика измерений. Выход элемента ИЛИ соединен с вторыми входами поверяемого и образцового аналого-цифровых преобра- зователей, а выход второго делителя частоты — с входами счетчика показаний (1).

Недостатками устройства являются необходимость периодического входного сигнала, низкая точность и большое время поверки аналого-цифровых преобразователей.

Наиболее близким к изобретению является устройство для измерения характеристик аналого-цифровых преобразователей, содержащее источник входного сигнала, выход которого соединен с первой выходной шиной и с первым входом образцового аналого-цифрового преобразователя, второй вход которого соединен с входом линии задержки и второи выходнои шиной, а выход соединен с первым входом блока сравнения кодов, второй вход которого соединен с выходом реверсивного счетчика, первый и второй выходы соединены соответственно с первым и вторым входами реверсивного счетчика, а третий — с входом генератора импульсов, третий вход реверсивного счетчика соединен с выходом генератора импульсов и входом делителя частоты, выход элемента ИЛИ через линию задержки соединен с четвертым входом реверсивного счетчика, пятый вход которого соединен с первой входной шиной устройства и первым входом блока памяти, первый вход элемента И соединен с выходом триггера, первый вход которого соединен с выходом переключателя, второи выход которого соединен с первым входом элемента ИЛИ, а вход через кнопку соединен с второй входной шиной устройства, второй вход элемента ИЛИ соединен с выходом элемента И, выход элемента ИЛИ сое30

55 динен с вторым входом образцового аналого-цифрового преобразователя и второй выходной шиной, выход делителя частоты соединен с входом первого счетчика, синхронизатор подключен своим выходом к второму входу элемента И, а входом — к четвертому выходу устройства сравнения кодов и к первому входу задатчика максимальной погрешности, второй вход которого соединен с выходом генератора, а выходы задатчика максимальной погрешности, образцового и поверяемого аналого-цифровых преобразователей подключены к входам блока памяти, при этом выход элемента И подключен к входу второго счетчика, выход которого подключен к управляющему входу делителя частоты и второму входу триггера (2).

Недостатками известного устройства являются малая точность и большое время поверки. Малая точность объясняется тем, что, во-первых, при суммировании погрешностей в счетчике погрешностей не учитывается знак погрешности, во — вторых, запуск аналого-цифровых преобразователей осуществляется неравномерно во времени, так как шаг дискретизации следующего измерения зависит от величины погрешности предыдущего измерения, поэтому осреднение по количеству измерений неэквивалентно осреднению по времени, необходимому для определения статистических характеристик погрешности; в-третьих, не учитывается коррелированность погрешностей соседних измерений, поскольку погрешность между измерениями считается равной погрешности предыдущего измерения. Для достижения требуемой точности поверки приходится увеличивать количество измерений и время поверки.

Цель изобретения — повышение точности устройства и уменьшение времени поверки.

Поставленная цель достигается тем, что в устройство для определения математического ожидания погрешности аналого-цифровых преобразователей, содержащее источник входного сигнала, выход которого соединен с первой выходной шиной и первым входом образцового аналого-цифрового преобразователя, второй вход которого соединен с входом линии задержки и второй выходной шиной, а выход — с первым входом блока сравнения кодов, второй вход которого соединен с выходом реверсивного счетчика, а первый выход — с первым входом реверсивного счетчика, второй вход которого соединен с первой входной шиной, третий вход — с входом линии задержки, а четвертый вход — с выходом генератора импульсов, входом делителя частоты и первым вХодом первого счетчика, выход которого соединен с первым входом блока памяти, первый триггер, первый вход которо1149407

3 го соединен с шиной «Пуск», второй вход— с выходом второго счетчика, а выход — с первым входом первого элемента И, введены блок суммирования, делитель на два, сумматор, вторая линия задержки, второй элемент И, второй триггер, первый вход которого соединен с выходом второго счетчика, а второй вход — с выходом второй линии задержки и вторым входом блока памяти, выход которого соединен с первым входом блока суммирования, второй вход to которого соединен с выходом первого счетчика. а выход через делитель на два — с первым входом сумматора, выход которого соединен с третьей выходной шиной, а второй вход — с входом второго счетчика и выходом второго элемента И, первый вход которого соединен с выходом второго триггера, а второй вход — с вторым выходом блока сравнения кодов, первый выход которого соединен с вторым входом первого счетчика, третий вход которого соединен с выходом первого элемента И и входом первой линии задержки, выход которой соединен с входом второй линии задержки, причем второй вход первого элемента И соединен с выходом делителя.

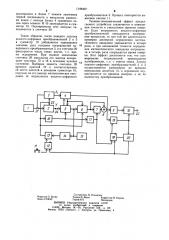

На чертеже изображена функциональ- ная схема предлагаемого устройства.

Устройство содержит источник 1 входных сигналов, который через образцовые аналого-цифровые преобразователи 2 и 3 подключены к первому входу блока 4 сравнения кодов, реверсивный счетчик 5. Второй вход и первый выход блока 4 сравнения кодов соединены соответственно с выходом реверсивного счетчика 5 и вторыми входами реверсивного счетчика 5 и первого счетчика 6. Выход первого счетчика 6 через з блок 7 памяти непосредственно подключен к первому и второму входам блока 8 суммирования, соединенного выходом через делитель 9 на два к первому входу сумматора 10. Кнопка 11 соединена с первым входом первого триггера 12, подключенного выходом к первому входу элемента И 13.

Второй вход элемента И 13 через делитель 14 импульсов соединен с третьим входом реверсивного счетчика 5, первым входом первого счетчика 6 и выходом генера- 4 тора 15 импульсов. Выход элемента И 13 подключен к вторым входам образцового и поверяемого аналого-цифровых преобразователей 2 и 3 и третьему входу первого счетчика 6, а также через первую линию 16 задержки к четвертому входу реверсивного 50 счетчика 5 и входу второй линии 17 задержки. Выход второй линии 17 задержки соединен с вторым входом блока 7 памяти и вторым входом второго триггера 18, подключенного к второму входу второго элемента И 19. Второй выход блока 4 сравнения кодов через второй элемент И 19 соединен с вторым входом сумматора 10, 4 входом второго счетчика 20. Выход второго счетчика 20 подключен к первому входу второго триггера 18 и второму входу первого триггера 12. Устройство имеет первую 21, вторую 22 и третью 23 выходные шины, входную шину 24.

Устройство работает следующим образом.

Поверяемый аналого-цифровой преобразователь подключают следующим образом: первый вход — к первой выходной шине, второй вход — к второй выходной шине, а выход — к входной шине устройства.

Случайный или детерминированный сигнал произвольной формы с выхода источника 1 подается на входы образцового 2 и поверяемого 3 аналого-цифровых преобразователей.

В исходном состоянии сумматор 10, триггеры 12 и 18 и счетчик 20 находятся в нулевом состоянии, элементы И 13 и 19 закрыты. При нажатии кнопки 11 триггер 12 переводится в единичное состояние и открывается элемент И 13. Первый же импульс с выхода делителя 14 запускает аналого-цифровые преобразователи 2 и 3 и сбрасывает счетчик 6 на нуль. По окончании преобразования первое показание Xi аналого-цифрового преобразователя 2 поступает на вход блока 4 сравнения кодов.

Через время задержки линии 16, которое выбирается больше времен преобразования аналого-цифровых преобразователей 2 и 3, первое показание У, поверяемого преобразователя 3 заносится в счетчик 5 и через него подается на второй вход блока 4 сравнения кодов, который выделяет знак первой погрешности (У, — Х, ), фиксирует знак в счетчике 6 и открывает его вход. Одновременно блок 4 открывает вход вычитания счетчика 5 при Х > У ) и вход сложения при Х (У, . При Х, =У, входы счетчиков 5 и 6 остаются закрытыми.

При Х, АУ импульсы генератора 15 заполняют счетчик 5 до тех пор, пока его показания не становятся равными Х,, Блок 4 сравнения кодов при этом выдает импульс, который не проходит закрытый элемент И 19. В счетчике 6 записывается алгебраическое значение первой погрешности поверяемого аналого-цифрового преобразователя 3. Спустя время задержки линии 17, после начала заполнения счетчика 6, это значение погрешности переписывается в блок 7 памяти. Одновременно в единичное состояние переводится триггер 18 и открывается элемент И 19.

Аналогично второй после пуска импульс делителя 14 запускает аналого-цифровые преобразователи 2 и 3 и выделяет в счетчике 6 алгебраическое значение второй погрешности поверяемого аналого-цифрового преобразователя 3. Оно осредняется с

11

S хранящимся в блоке 7 памяти значением первой погрешности и импульсом равенства кодов с выхода блока 4 сравнения кодов через элемент И 19 записывается в сумматор 10. Одновременно этот импульс записывается в счетчике 20.

Таким образом, после каждого запуска аналого-цифровых преобразователей 2 и 3 в сумматор 10 добавляется осредненное значение двух соседних погрешностей поверяемого преобразователя 3, а в счетчике 20 фиксируется число таких шагов, т.е. время осреднения. При полном заполнении счетчика 20 импульсов его выхода возвращает триггеры 12 и 18 в исходное нулевое состояние. Выбирая емкость счетчика 20 времени кратной 10 и соответствующее ей место запятой в декадном сумматоре 10, получим на его выходе математическое ожидание m погрешности аналого-цифрового

49407 преобразователя 3, Процесс повторяется на.жатием кнопки 11.

Технико-экономический эффект предлагаемого устройства заключается в повышении точности и уменьшении времени поверки. Если погрешность аналого-цифровых преобразователей описывается винеровским процессом, то при той же длительности проверки дисперсия определения математического ожидания уменьшается в четыре раза, а при неизменной точности определения математического ожидания погрешности в четыре раза сокращается время поверки. Этот эффект достигается тем, что суммирование погрешностей производится алгебраически, т. е. с учетом знака. Запуск

15 аналого-цифровых преобразователеи 2 и 3 осуществляется равномерно во времени импульсами делителя 14, и осреднение осуществляется по времени поверки, а не по количеству преобразований.

Составитель И. Романова

Редактор О. Бугир Техред И. Верес Корректор Н. Король

Заказ 1918 42 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 7К вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4