Делитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ, содержащий статический регистр и генератор импульсов, выход которого соединен с входом фазосдвигающего элемента, выходы которого подключены к первой группе входов электронного коммутатора, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом триггера, а выход - со счетньм входом счетчика импульсов, выход которого соединен, с выходной шиной, отличающийся тем, что, с целью повьшения быстродействия , в него введен кольцевой сдвиговый регистр, информационные входы которого соединены с информационными входами статического регистра и входной шиной, вход синхронизации - с выходом счетчика импульсов, группа выходов - с второй группой входов электронного коммутатора, а дополнительню выход - с первым входом триггера, второй вход которого под (Л ключен к выходу электронного коммутас тора. СП (jff/e.f

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) 4(у) H 03 K 23/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР .

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3462858/24-21 (22) 02.07.82 (46) 15.04.85. Вюл. В 14 (72) В.Ф. Ворожеев и А.И. Панов (53) 621.374(088.8) (56) Лейнов N.Ë., Качалуба В.С., Рыжков А.В. Цифровые делители частоты на логических элементах. M., "Энергия", 1975, с. 121.

2. "Приборы и техника эксперимента", 1981, h"- 5, с. 119-122. (54) (57) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ

ИМПУЛЬСОВ, содержащий. статический регистр и генератор импульсов, выход которого соединен с входом фазосдвигающего элемента, выходы котброго подключены к первой группе входов электронного коммутатора, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом триггера, а выход — со счетным входом счетчика импульсов, выход которого соединен с выходной шиной, отличающийся тем, что, с целью повышения быстродействия, в него введен кольцевой сдвиговый регистр, информационные входы которого соединены с информационными входами статического регистра и входной шиной, вход синхронизации — с выходом счетчика импульсов, группа выходов — с второй группой входов электронного коммутатора, а дополнительный выход — с первым входом ® триггера, второй вход которого подключен к выходу электронного коммутатора. С

1 11507

Изобретение относится к вычислительной технике, в частности к делителям частоты с переменным коэффициентом деления,. предназначенным для использования в различной радиоэлект- ронной аппаратуре, например, в качестве датчиков интервалов времени, умножителей опорной частоты в схемах фазовой автоподстройки частоты и т.д, Цель изобретения — повышение быст-1О родействия.

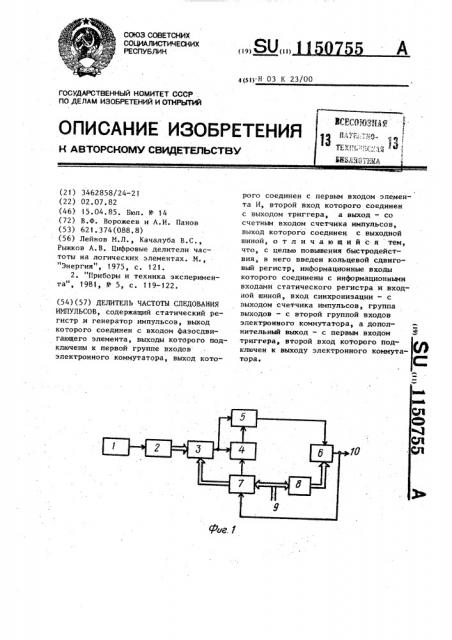

На фиг.1 показана блок-схема предложенного делителя частоты; на фиг.2— временные диаграммы его работы.

Делитель содержит генератор 1 им- 15 пульсов, фазосдвигающий элемент 2, электронный коммутатор 3, триггер 4, элемент .И 5, счетчик 6 импульсов, регистр хранения кода целой и дробной частей коэффициента деления, образо- 20 ванный кольцевым сдвиговым и статическим регистрами 7 и 8 соответственно, входную и выходную шины 9 и 10 соответственно.

Выход генератора 1 импульсов под-25 ключен к входу фазосдвигающего элемента 2, который своими выходами соединен с первой. группой входов электронного коммутатора 3, вторая группа входов которого соединена с

30 группой выходов кольцевого сдвигового регистра 7, а выход — с входами триггера 4 элемента И 5, второй вход которого соединен с выходом триггера

4, а выход — со счетным входом счетчика 6 импульсов, установленные входы которого подключены к выходам статического регистра 8, а выход— со входом синхронизации кольцевого сдвигового регистра 7 и выходной ши-ной 10 устройства. Информационные входы регистров 7 и 8 соединены с входной шиной 9 устройства, дополнительный выход кольцевого сдвигового регистра 7 соединен с первым входом триггера 4.

Генератор 1 импульсов предназначен для выработки импульсов с частотой f = 50,0 ИГц и выполнен в виде кварцевого генератора на интегральных схемах серии 500.

Фазосдвигающий элемент 2 служит для формирования импульсов с частотой генератора 1 импульсов, равной

50,0 ИГц, сдвинутых по фазе на вели55 чины вЂ, вЂ, вЂ,..., вЂ, где число дискретностей m = 10, à и принимает значения от 1 до 10. Фазосдвигающий эле55 1 мент 2 выполнен в виде коммутируемой линии калиброванных задержек, в качестве элементов задержек использованы микросхемы сепии 100 К.

Электронный коммутатор 3 предназначен для подключения одного из элементов задержек (в нашем случае одного из десяти) фазосдвигающего элемента 2 к входам триггера 4 и логического элемента И 5. Коммутатор 3 представляет собой мультиплексор на

10 входов с дешифрацией задержек и выполнен на микросхемах К500

ИД164М.

Триггер 4 и элемент 5 совместно предназначены для организации пропуска импульса генератора 1 импульсов в моменты времени, программируемые кольцевым сдвиговым регистром 7.

Триггер 4 и логический элемент И 5 выполнены на микросхемах серии 500.

Счетчик 6 импульсов выполнен в виде программируемоro вычитающеro счетчика, работающего в режиме делителя частоты с переменным коэффициентом деления и предназначенного для формирования импульсов, соответствующих заданному коэффициенту деления. В качестве счетчика 6 импульсов использованы микросхемы К 500ИЕ 137.

Кольцевой сдвиговый регистр 7 и статический регистр 8 совместно образуют регистр хранения кода целой и дробной частей коэффициента деления. При этом кольцевой сдвиговый регистр 7 предназначен для записи и хранения информации о величине дробной части коэффициента деления, а также команд о необходимости пропуска импульса и подключения через электронный коммутатор 3 выбранного элемента задержки фазосдвигающего элемента 2. Кольцевой сдвиговый регистр 7 в общем случае имеет n+1 разряд по ширине, где и определяет значение задержки, выбираемой электронным коммутатором 3 в данный момент времени, и один разряд определяет момент, в который нужно сделать пропуск импульсов. Число и определяется соотношением

Ъ 1о8 (, 1 где х — минимальное значение дробной части коэффициента деления.

Число разрядов регистра 7 по глубине равно величине знаменателя дробной части коэффициента деления.

3 1150755 4

Статический регистр 8 служит для импульсы с частотой записи и хранения информации о величи- формация о величина не целой части коэффициента деления сов с выхода кольце и выполнен р-разрядным, где р опре- регистра 7 поступае деляется соотношением ронного коммутатора р), log М, где М вЂ” коэффициент деления целой части. !0

Кольцевой сдвиговый и статический регистры 7 и 8 выполнены на микросхемах серии 500 (К500ИР14 1) .

В приведенном примере регистр хра- нения кода целой и дробной частей коэффициента деления образован 5разрядным кольцевым сдвиговым регист ром 7 (Рг1-Рг5) и 10-разрядным статическим регистром 8.

Делитель частоты работает следую- 20 щим образом.

Пусть необходимо сформировать выходные импульсы с коэффициентом деления К = 3,3 при дискретности дробной части m - =10. При частоте импульсов генератора 1 f = 50 МГц величина дискретности дробной части равна

Т где Т вЂ” период частоты генератора !

1 импульсов, равный— . 50 МГц 30

20 нс. Тогда — = = 2 нс.

m 10

Как видно из временных диаграмм, для того, чтобы сформировать выходные импульсы с коэффициентом деления

К = 3,3, необходимо каждый третий

35 импульс генератора 1 импульсов (см. фиг.2 а) сдвигать после кажцого сформированного выходного импульса ,на 6 нс (см.. фиг. 2 5). При этом по .40 входной шине 9 в кольцевой сдвкговый регистр 7 иэ программного устройства (не показано) заносится информация о величинах задержек при формировании требуемого коэффициента деле» ния, а в статический регистр 8 - информация о величине целой части коэффициента деления. Для К 3,3 значения задержек составляют 6, 12, 18, 4, 10, 16» 8, 14, О, 6, 12 нс и т.д., т.е. через ш импульсов (в на50 шем случае m = 10) эти значения повторяются,.

На вход фазосдвигающего элемента

2 а генератора импульсов поступают

f = 50 ИГц. Инх задержек импульвого сдвигового т на вход элект3, посредством которого осуществляется подключение соответствующего элемента задержки фазосдвигающего элемента 2. При переходе величины задержки через нуль (О) на выходе электронного коммутатора 3 оказывается лишний (четвертый). импульс, который на счетчик 6 импульсов не должен пройти. Гашение таких импульсов производится триггером 4 и логическим элементом И 5 по программе, хранящейся в кольцевом сдвиговом регистре 7. При поступлении иэ регистра 7 на вход триггера 4 ™О" на его выходе устанавливается состояние "1" и элемент И 5 пропускает импульсы на.счетчик 6 импульсов без гашения. При поступлении в триггер

4 "1" открывается вход элемента И 5 по заднему фронту переднего импульса.

В счетчике 6 импульсов в каждом такте производится перезапись коэффициента деления целой части, хранящейся в статическом регистре 8, и в момент очистки счетчика 6 на его выходе будет сформирован импульс переноса с заданным коэффициентом деления К = 3,3, который (импульс) поступает на выходную шину

10 устройства (фиг. 2 в).

При формировании выходных импульсов с коэффициентом деления К = 3,8 также необходимо сдвигать каждый третий импульс, с той лишь разницей, что в процессе формирования повторяются значения задержек 8, 6, 4, 2, О нс (см. фиг. 2 г, д).

Таким образом, данный делитель частоты использует принцип повторяемости информации о величинах задержек при формировании дробного коэффициента деления. Информация о требуемых величинах задержек предварительно записывается в кольцевой сдвиговый регистр и используется в .-.оследующем при формировании выходных импульсов с заданным коэффициентом деления.

Это позволяет исключить из схемы де лителя накапливающий сумматор H тем самым повысить его быстродекствие.

1150755 а

Р а г а

/7расйлжеж е

0

1 фиг. 2

Составитель О. Кружилина

Редактор В. Ковтун Техред Т.Дубинчак Корректор Л. Пилипенко

Заказ 2174/44 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4