Синхронный делитель частоты на 11 на @ -триггерах

Иллюстрации

Показать всеРеферат

СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ НА II НА :к-ТРИГГЕРАХ, содержащий четыре DK- -триггера и два логических .элемента И, счетные входы всех Пктриггеров соединены с тактовой шиной устройства, входы R всех JK триггеров соединены с шиной сброса устройства, выходы четвертого JK триггера являются выходными шинами устройства, прямой выход первого Л1стриггера соединен с входом J второго - -триггера, прямой выход которого соединен с первым входом первого логического элемента И, выход которого соединен с входом D четвертого 3k -триггера, отличающийся тем, что, с целью упрощения устройства, вход 3 первого ЗК триггера соединен с инверсным выходом четвертого JK -триггера, вход К - с прямым выходом второго -Тк триггера и с входом 3 третьего jK-триггера, инверсный выход соединен с вторым входом первого логического элемента И, вход К второго JK-триггера соединен с инверсным выходом третьего Зк -триггера и (Л первым входом второго логического элемента И, второй вход которого соединен с инверсным выходом второго : К-триггера, а выход - с входом к четвертого зк.-триггера, вход k третьего Jk -триггера соединен с прямым выходом четвертого ЗК -триг гера. ел о ч| ел 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТ ИЧЕСНИХ

РЕСПУБЛИК

4(sl) Н 03 К 23/24

ОПИСАНИЕ ИЗОБРЕТ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3649507/24-21 (22) 10.10.83 (46) 15.04.85. Бюл. К - 14 (72) В.И.Мяснов (53) 621.374(088.8) (56) 1. Букреев И.H., Мансуров Б.M., Горячев В.И. Микроэлектронные схемы цифровых устройств. М., Советское радио", 1975.

2. Будинский Я. Логические цепи в цифровой технике". Пер. с чешского под ред. Б.А.Калабекова. М., "Связь", 1977 (прототип), (54) (57) СИНХРОННЪ|И ЛЕЛИТЕЛЬ ЧАСТОТЫ

HA (I НА Э к -ТРИГГЕРАХ, содержащий четыре 3к -триггера и два логических .элемента И, счетные входы всех Эктриггеров соединены с тактовой шиной устройства, входы R всех 3K— триггеров соединены с шиной сброса устройства, выходы четвертого 3ктриггера являются выходными шинами устройства, прямой выход первого 3k.— триггера соединен с входом 3 второго -пк -триггера, прямой выход которого соединен с первым входом первого логического элемента И, выход которого соединен с входом Э четвертого 3К -триггера, о т л и ч а ю— шийся тем, что, с целью упрощения устройства, вход 3 первого Э триггера соединен с инверсным выходом четвертого 3К -триггера, вход

К вЂ” с прямым выходом второго 3к— триггера и с входом 3 третьего

3к-триггера, инверсный выход соединен с вторым входом первого логического элемента И, вход К второго

3к-триггера соединен с инверсным выходом третьего 3к -триггера и первым входом второго логического элемента И, второй вход которого соединен с инверсным выходом второго

3к-триггера, а выход — с входом К четвертого 3К -триггера, вход k третьего 3к -триггера соединен с прямым выходом четвертого ЗК -триг" гера.

50759

Недостатками данного делителя частоты являются его сложность, а также то, что эта схема несинхронная.

Наиболее близким к предлагаемому является синхронный делитель частоты на 11 на ЗК -триггерах, работающий в .коде 8-4-2-1.

Известный синхронный делитель содержит четыре ЭК -триггера, два логических элемента И и два И-НЕ, счетные входы всех 31<-триггеров соединены между собой и с входной шиной устройства, входы р. всех триггеров соединены между собой и с шиной сброса устройства, 3 вход первого 3к -триггера соединен с выходом первого элемента -HF., два входа которого соединены с прямыми выходами второго и четвертого 3К триггеров соответственно, k вход первого 3К -триггера соединен с шиной логической единицы, 3 вход второго - .К -триггера соединен с прямым выходом первого триггера, К вход второго 3К -триггера соединен с выходом второго элемента И-НЕ, два входа которого соединены с .инверсными выходами первого и четвертого

3к-триггеров соответственно, J и К входы третьего 3К -триггера соединены с выходом первого элемента И, два входа которого соединены с прямыми выходами первого и второго 3Ктриггеров соответственно, 3 вход четвертого 3К -триггера соединен с выходом второго элемента И, три входа которого соединены с прямыми выходами первого, второго и третьего 3K -триггеров соответственно, вход четвертого 3К -триггера соединен с прямым выходом второго 3к..триггера, прямой выход четвертого

3К-триггера является выходом делителя (2 j.

Недостатком известного делителя является сложность, приводящая к низкой надежности и большой потребляемой мощности за счет большого количества элементов и цепей.

Цель изобретения — упрощение устройства.

z Q

3 2

1 в

К4=1 РзК =0 т >

1 11

Изобретение относится к цифровой технике и может быть использовано, например, при построении хронизаторов, цифровых синтезаторов частоты, электромузыкальных инструментов и т.д

Известен делитель частоты на 11, содержащий 5 3k -триггеров $1).

° 5

Поставленная цель достигается тем, что в синхронном делителе частоты на 11 на К -триггерах, содержащем четыре J< -триггера и два логических элемента И, счетные входы всех 3к -триггеров соединены с тактовой шиной устройства, входы всех К -триггеров соединены с шиной сброса устройства, выходь1 четвертого Зк -триггера являются выходными шинами устройства, прямой выход первого 3К -триггера соединен с входом Э второго 3К -триггера, прямой выход которого соединен с первым входом первого логического элемента И, выход которого соединен с входом 3 четвертого 3к -триггера, вход 3 первого Эк -триггера соединен с инверсным выходом четвертого 3(< -триггера, вход I< — с прямым выходом второго 3к -триггера ,и с входом 3 третьего 3к-триггера, инверсный выход .соединен с вторым входом первого логического элемента

И, вход К второго 3к -триггера соединен с инверсным выходом третьего

3k-триггера и первым входом второго логического элемента И, второй вход которого соединен с инверсным выходом второго 3К -триггера, а выход— с входом К четвертого 3К -триггера, вход К третьего 3К -триггера соединен с прямым выходом четвертого 3К— триггера.

При такой схеме соединения логические уравнения для 3 и К входов всех триггеров синхронного делителя частоты на 11 будут следующими:

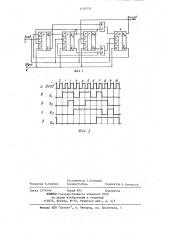

На фиг. 1 приведена структурная схема синхронного делителя частоты на 11 íà 3К -триггерах; на фиг.2— временные диаграммы устройства, где обозначено: а — входной сигнал на тактовой шине; б, в, г, д — сигнал на прямых выходах 3К -триггеров при поступлении входных импульсов с номерами с О по 10-й.

Синхронный делитель -частоты на 11 на 3К -триггерах содержит четыре

3К-триггера 1,2,3 и 4 и два логических элемента И 5, 6, счетные входы всех 3К -триггеров соединены с тактовой шиной 7 устройства, входы всех Эк -триггеров соединены с шиной

9 "0«

На о ний для стояния

3 =« !«

1" снова нии л огич е ских ур а вне3 и К входов триггеров совходов равны

32=«0";

« Il «« 3=

Поскольку ЗК -триггер по последующему импульсу (на фиг. 1 и 2 триггеры переключаются по отрицательному., перепаду сигнала на счетном входе) при 3 ="0" и К ="0" не изменяет своего состояния, при 3 ="!" и

К="1" — переключается в противопо3 11507 сброса устройства, выход четвертого

3К -триггера является выходом устройства, прямой выход триггера 1 соединен с входом 3 триггера 2, прямой выход которого соединен с первым входом элемента И 5, выход которого соединен с входом 3 триггера 4, вход

3 триггера 1 соединен с инверсным выходом триггера 4 вход K — - с прямым выходом триггера 2 и с входом 3 - !О триггера 3, инверсный выход — с вторым входом элемента И 5, вход К триггера 2 соединен с инверсным выходом триггера 3 и первым входом элемента И 6, второй вход которого соединен с инверсным выходом триггера

2, выход — с входом К триггера 4, прямой выход которого соединен с входом К триггера 3.

Работа синхронного делителя час- 2р тоты на 11 Hà 3К -триггерах полностью описывается логическими уравнениями для 3 и К входов его триггеров.

ЭтиМи же уравнениями определяется и схема соединения Э и k входов с соответствующими выходами соответствующих триггеров.

По сигналу "Сброс" на шине 8 все триггеры синхронного делителя частоты на 11 устанавливаются в исходное нулевое положение. При этом (см. диаграммы на фиг,2 б, в, r д при

1 =О), состояния BbIKopoB равны

59 4 ложное состояние, при 3 ="1", К="0" — переключается в состояние логической единицы и при 3 "0" и К ="1" — переключается в состояние логического нуля, то по первому входному импульсу первый триггер переключается в состояние логической единицы (фиг. 2 б), второй триггер подтверждается в состоянии логического нуля (фиг.2 в), третий триггер не изменяет своего состояния (фиг.2 г), четвертый триггер остается в состоянии логического нуля (фиг.2 д). Таким образом, по срезу первого входного импульса только триггер 1 переключается.в состояние логической единицы, а триггеры 2, 3 и 4 остаются в нулевом состоянии, и состояния выходов станут равны

При этом состоянии входов станут равными

3 =,(«

По второму входному импульсу схема переходит в свое второе состояние (см. диаграммы на фиг.2 б, в, г, д при t =2), в котором а„="„« - и ="<" > ="o«

Э 4 3 1 3y< g 0

Рассматривая далее работу предлагаемого синхронного делителя частоты на 11 на Эк -триггерах таким же образом, получим все значения входов и выходов каждого триггера при всех.ь

Из сравнения логических уравнений для 3 и К входов триггеров прототипа и синхронного делителя -частоты на 11 на Лк -триггерах видно, что последний имеет меньшее количество элементов и цепеК, что положительно сказывается на надежности, потребляемой мощности и упрощает схему синхронного делителя частоты на 11 на 3К -триггерах.

1150759 яыя dd

g ЮА ад

8 0

8 Ду д д

Со с тави тель С. Кле вцов

Техред M,Íàäü Корректор В.Синицкая

Редактор В.Ковтун .Заказ 2174/44 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4