Устройство отображения формы электрического сигнала

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ОТОБРАЖЕНИЯ ФОРМЫ ЭЛЕКТРИЧЕСКОГО СИГНАЛА, содержащее матричный газоразрядньй индикатор , подключенный первыми шинами к выходам первого блока коммутации , связанного своими информационными входами с выходами дешифратора развертки, а управляющим входом - с одноименным входом второго блока коммутации , своими выходами подключенного к вторым шинам матричного газоразрядного индикатора, а информационными входами - к выходам формирователя вертикальных отрезков, входы которого соединены с выходами блока смещения по оси Y , аналогоцифровой преобразователь, информационный вход которого является вькодом устройства, а выход подключен к информационному входу блока памяти, адресный вход которого подключен к выходу первого коммутатора, информационными входами подключенного к первому входу первого и выходу второго счетчиков, счетными входами подключенных соответственно к первому и второму выходам генератора тактовых импульсов, первый вход первого счетчика также связан с синхронизирующими входами аналого-цифрового преобразователя и блока памяти, первый коммутатор удтравляющими входами подключен к выходам R5 -триггера, второй коммутатор первым входом соединен с выходом управляемого делителя частоты, связанного одним управляюнщм входом с выходом формирователя кода масштаба, другим - с вторым выходом генератора тактовых импульсов , второй вход второго коммутатора связан с третьим выходом генератора тактовых импульсов, входы Н5-триггера подключены 6-входом к (Л ВХОДУ запуска устройства и управляющему входу первого счетчика, а R-входом - к второму выходу первого счетчика, второй счетчик, подключенный О -входом к выходу формирователя кода смещения по оси X, о т л и чающееся тем, что, с целью повьш1ения информативности отображения формы широкополосных электрических сигналов при их сжатии по оси X, в него дополнительно введены первое и второе буферные запоминающие устройства , первый и второй компараторы кодов, первый и второй элементы ИЛИ, третий счетчик и элемент НЕ, причем информационные входы первого и второго буферных запоминающих устройств объединены и подключены к выходу блока памяти, выходы запоминающих устройств подключены к входам блока смещения по оси Y , синхронизирующие входы каждого буферного запоминающего устройства соеди

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

О A

f

t ф

Э

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3628107/24-21 (22) 21.07.83 (46) 23.04.85. Бюл. )ъ 15 (72) А.Н. Скурский, Я.Л.Буртов, А;Ф.Малахов и С.П. Толпенко (71) Краснодарское отделение Всесоюзного научно-исследовательского института источников тока (53) 621.391.837(088.8) (56) 1. Авторское свидетельство СССР

М 640288, кл. G 01 D 7/00, 22.04.76.

2. Авторское свидетельство СССР

И 542095, кл. С 01 0 7/00, 28.10.74. (54)(57) УСТРОЙСТВО ОТОБРАЖЕНИЯ

ФОРМЫ ЭЛЕКТРИЧЕСКОГО СИГНАЛА, содержащее матричный газоразрядный индикатор, подключенный первыми шинами к выходам первого блока коммутации, связанного своими информационными входами с выходами дешифратора развертки, а управляющим входом — с одноименным входом второго блока коммутации, своими выходами подключенного к вторым шинам матричного газоразрядного индикатора, а информационными входами — к- выходам формирователя вертикальных отрезков, входы которого соединены с выходами блока смещения по оси (, аналогоцифровой преобразователь, информационный вход которого является выходом устройства, а выход подключен к информационному входу блока памяти, адресный вход которого подключен к выходу первого коммутатора, информационными входами подключенного к первому входу первого и выходу второго счетчиков, счетными входами подключенных соответственно к перво4(gi) G 01 D 7/00; С 09 G 3/20 му и второму выходам генератора тактовых импульсов, первый вход первого счетчика также связан с синхронизирующими входами аналого-цифрового преобразователя и блока памяти, первый коммутатор управляющими входами подключен к выходам R -триггера, второй коммутатор первым входом соединен с выходом управляемого делителя частоты, связанного одним управляющим входом с выходом формирователя кода масштаба, другим — с вторым выходом генератора тактовых импульсов, второй вход второго коммутатора связан с третьим выходом генератора тактовых импульсов, входы

)(5-триггера подключены 5 -входом к .входу запуска устройства и управляющему входу первого счетчика, а

)(-входом — к второму выходу первого счетчика, второй счетчик, подключенный О -входом к вь1ходу формирователя кода смещения по оси Х, о т л и-! ч а ю щ е е с я тем, что, с целью повышения информативности отображения формы широкополосных электрических сигналов при их сжатии по оси Х, в него дополнительно введены первое и второе буферные запоминающие уст" ройства, первый и второй компараторы кодов, первый и второй элементы

ИЛИ, третий счетчик и элемент НЕ, причем информационные входы первого и второго буферных запоминающих устройств объединены и подключены к выходу блока памяти, выходы запоминающих устройств подключены к входам блока смещения по оси Y, синхронизирующие входы каждого буферного запоминающего устройства соеди1151820 нены с выходами первого и второго элементов ИЛИ соответственно, первые входы элементов ИЛИ соединены с выходом управляемого делителя частоты, вторые входы элементов ИЛИ соединены с вторым выходом первого счетчика и с первым входом третьего советчика, третьи входы первого и .второго .элементов ИЛИ подключены соот. ветственно к прямому выходу первого компаратора и инверсному выходу второго компаратора кодов, первые . информационные входы обоих компараторов соединены с информационными входами буферных запоминающих устройств, вторые информационные .входы первого и второго компараторов соединены с выходами первого.и второго буферных запоминающих устройств соответственно, а стробирующие входы обоих комнараторов объединены и

Изобретение относится к информационно-измерительной технике.

Известно устройство, содержащее газоразрядную индикаторную панель, блок памяти, линейный интегратор, блок смещения и масштабирования, блок выборки строк, блок ключей,.

) дешифратор столбцов, счетчик горизонтальной развертки, счетчик адреса и эадатчик смещения по оси X (1) .10

Недостатком этого устройства является низкая оперативность визуальной оценки формы широкополосных сигналов.

Наиболее близким к предлагаемо- 15 му по технической сущности является устройство для отображения формы регистрируемого процесса, содержащее матричный газоразрядный индикатор, подключенный первыми шинами 20 к.выходам первого блока коммутации,,связанного своими информационными входами с выходами дешифратора развертки,. а управляющим входом — с одноименным входом второго блока ком-25 мутации, своими выходами подключенного к вторым шинам матричного газоразрядного индикатора, а информационными входами - к выходам формирователя вертикальных отрезков, 30 связаны с вторым выходом генератора тактовых импульсов, адресные входы первого и второго буферных запоминающих устройств объединены и подключены к первому выходу третьего счетчика и входу дешифратора развертки, управляющие входы первого и второго буферных запоминающих устройств объединены и подключены к второму выходу третьего счетчика, счетный выход которого соединен с выходом второго коммутатора, второй выход третьего счетчика соединен с первым управляющим входом второго коммутатора и входом элемента НЕ, выходом подключенного к установочному входу второго счетчика, второму управляющему входу второго коммутатора и управляющим входам первого и второго блоков коммутации. входы которого соединены с выходами блока смещения по оси 1, аналогоцифровой преобразователь, информационный вход которого является входом устройства, а выход подключен к информационному входу блока памяти, адресный вход которого подключен к выходу первого коммутатора, информационными входами подключенного к первому выходу первого и выходу второго счетчика, счетными входами подключенных соответственно к первому и второму выходам генератора тактовых импульсов, первый вход первого счетчика также связан с синхронизирующими входами аналогоцифрового преобразователя и блока памяти, первый коммутатор управляющими входами подключен к выходам

36-триггера, второй коммутатор первым входом соединен с выходом управляемого делителя частоты, связанного одним управляющим входом с выходом формирователя кода масштаба, другим - с вторым выходом генератора тактовых импульсов, второй вход второго коммутатора связан с третьим выходом генератора тактовых импульсов, входы RS-триггера подключены

6-входом к входу запуска устройства

1151820 и управляющему входу первого счет.— чика, а 1 входом — к второму выходу первого счетчика, второй счетчик, подключенныйЮ -входом к выходу формирователя кода смещения по оси )(Г21 .

Недостатком известного устройства является потеря информации о составляющих сигнала при сжатии изображения по оси (, Цель изобретения — повышение ин- 10 формативности отображения формы широкополосных электрических сигналов при их сжатии по оси Х..

Поставленная цель достигается тем, что в устройство, содержащее

15 матричный газоразрядный индикатор, подключенный первыми шинами к выходам первого блока коммутации, связанного своими информационными входами с выходами дешифратора развертки, а управляющим входом — с одноименным входом второго блока коммутации, своими выходами подключенного к вторым шинам матричного газоразрядного индикатора, à информационными входами — к выходам формирователя вертикальных отрезков, входы которого соединены с выходами блока смещения по оси (, аналого-цифровой преобразователь, информационный вход кото- З0 рого является выходом устройства, а выход подключен к информационному входу блока памяти, адресный вход которого подключен к выходу первого коммутатора, информационными входами 35 подключенного к первому входу первого и выходу второго счетчиков, счетными входами подключенных соответственно к первому и второму выходам генератора тактовых импульсов, пер- 40 вый вход первого счетчика также связан с синхронизирующими входами аналого-цифрового преобразователя и блока памяти, первый коммутатор управляющими входами подключен к вы- 45 ходам 35 -триггера, второй коммутатор первым входом соединен с выходом управляемого делителя частоты, связанного одним управляющим входом с выходом формирователя кода масшта- 50 ба, другим — с вторым выходом генератора тактовых импульсов, второй вход второго коммутатора связан с третьим выходом генератора тактовых импульсов, входы хо-триггера подклю- 55 чены 5 --входом к входу запуска устройства и управляющему входу первого счетчика, а К -входом — к второму выходу первого счетчика, второй счетчик, подключенный 0 -входом к выходу формирователя кода смещения по оси 1, дополнительно введены первое и второе буферные запоминающие устройства, первый и второй компараторы кодов, первый и второй элементы ИПИ, третий счетчик и элемент

НЕ, причем информационные входы первого и второго буферных запоминающих устройств объединены и подключены к выходу блока памяти, выходы запоминающих устройств подключены к входам блока смещения по оси У синхронизирующие входы каждого буферного запоминающего устройства соединены с выходами первого и второго элементов ИЛИ соответственно, первые входы элементов ИЛИ соединены с вЫходом- управляемого делителя частоты, вторые входы элементов ИЛИ соединены с вторым выходом первого счетчика и с первым входом третьего счетчика, третьи входы первого и второго элементов ИЛИ подключены соответственно к прямому выходу первого компаратора и инверсному выходу второго компаратора кодов, первые информационные входы обоих компаратоI ров соединены с информационными входами буферных запоминающих устройств, вторые информационные входы первого и второго компараторов соединены с выходами. первого и второго буферных запоминающих устройств соответственно, а стробирующие входы обоих компараторов объединены и связаны с вторым выходом генератора тактовых импульсов, адресные входы первого и второго буферных запоминающих устройств объединены и подключены к первому выходу третьего счетчика и входу дешифратора развертки, управляющие входы первого и второго буферных запоминающих устройств объединены и подключены к второму выходу третьего счетчика, счетный вход которого соединен с выходом второго коммутатора, второй выход третьего счетчика соединен с первым управляющим входом второго коммутатора и входом элемента НЕ, выходом подключенного к установочному входу второго счетчика, второму управляющему входу второго коммутатора и управляющим входам первого и второго блоков коммутации.

1151820

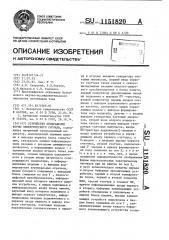

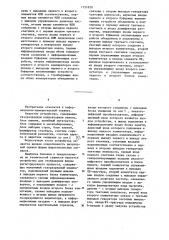

На фиг. 1 представлена блок-схема устройства, на фиг. 2 и 3 — фор- мирование сигналов.

Устройство отображения Формы электрического сигнала содержит ма- 5 тричный газоразрядный индикатор 1, подключенный первыми шинами к выходам первого блока 2 коммутации, связанного своими информационными входами с выходами дешифратора 3 раз- 1О вертки, а управляющим входом — с одноименным входом второго блока 4 коммутации, своими выходами подклю ченного к вторым шинам матричного газораэрядного индикатора, а инфор11 мационными входами — к выходам формирователя 5 вертикальных отрезков, состоящего из элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ 6, элементов 2И-НЕ 7 и дешифраторов 8, входы формирователя верти- 2О кальных отрезков соединены .с выходами блока 9 смещения по оси Y. на основе сумматоров 10 и 11 и формирователя 12 кода смещения, аналогоцифровой преобразователь 13, информационный вход которого является входом устройства, генератор 14 тактовых импульсов, блок 15 памяти, первый коммутатор 16, информационными входами подключенный к перво- ЗО ! му выходу первого счетчика 17, 3S-триггер 18, второй счетчик 19, управляемый делитель 20 частоты, формирователь 21 кода смещения по оси X,,формирователь 22 кода масштаба по оси Х, второй коммутатор 23, первое 24 и второе 25 буферные запоминающие устройства, первый 26 и второй 27 компараторы кодов, элементы ИЛИ 28 и 29, третий счетчик 30 4О и элемент НЕ 31.

Устройство работает следующим образом.

По сигналу "Пуск" первый счетчик

17 обнуляется, триггер 18 переводит- 4> ся в единичное состояние и блок 15 памяти переводится в режим записи.

При этом на информационный вход поступают цифровые коды с выхода аналого-цифрового преобразователя 13, а на адресный вход через первый коммутатор 16 — цифровые коды с первого выхода первого счетчика 17. Аналогоцифровой преобразователь 13, блок

15 памяти и первый счетчик 17 синхро-5> низируются сигналом .с частотой „, поступающим с первого выхода генера.—, тора 14 тактовых импульсов. По занолнении блока 15 памяти на втором выходе первого счетчика 17 формируется сигнал, который, поступая на 8 -вход триггера 18, возвращает его в исходное состояние, при этом блок 15 памяти переводится в режим считывания информации, а его адресный вход через первый коммутатор 16 оказывается подключенным к выходу второго счетчика 19, синхронизируемого сигналом с частотой 1,, поступающим с второго выхода генератора 14 тактовых импульсов ° На вход синхронизации третьего счетчика 30 через второй коммутатор 23 поступает сигнал с частотой 1 ци, / и с управляемого делителя 20 частоты.

Коэффициент деления задается формирователем 22 кода масштаба по оси

При этом на втором выходе третьего счетчика 30 имеет место сигнал логического нуля, что обеспечивает режим записи информации в первом

24 и втором 25 буферных запоминающих устройствах, причем соотношение скоростей изменения адреса блока 15 памяти {1 !,„, ) и буферных запоминающих устройств 24 и 25 (fee /и ) апре деляется требуемым масштабом по оси

4 При каждом изменении адреса буферных запоминающих устройств 24 и

25 на их стробирующие входы через элементь. ИЛИ 28 и 29 поступают сигналы с выхода управляемого делителя

20 частоты, обеспечивая запись цифровых кодов с выхода блока 15 памяти в оба буферных запоминающих уст-! ройства.При последующих изменениях " адреса блока 15 памяти информация с его выхода анализируется компараторами 26 и 27 кодов, стробируемых сигналом с частотой 1 „ц„, при этом, если цифровой код на выходе блока

15 памяти больший, чем записанный ра нее в буферном запоминающем устройстве 24 (или меньший,чем в буферном запоминающем устройстве 25), то на прямом выходе компаратора 26 кодов (или на инверсном выходе компаратора 27 кодов) формируется сигнал, обеспечивающий запись данного кода в соответствующее буферное запоминающее устройство 24 (или 25).

Затем при очередном изменении адреса буферных запоминающих устройств в них опять производится запись цифровых кодов по сигналу с выхода управляемого делителя 20 частоты

7 1151 независимо от состояния компараторов

26 и 27 кодов. Тем самым обеспечивается преобразование зарегистрированной в блоке 15 памяти информации таким образом, что в буферных за- 5 поминающих устройствах 24 и 25 регистрируются соответственно максимальные и.минимальные из каждых 11 кодов, поступающих с выхода блока

15 памяти. По заполнении буферных 10 запоминающих устройств 24 и 25, емкость каждого из которых выбирается равной информационной емкости матричного газоразрядного индикатора 1, на втором выходе третьего 15 счетчика 30. формируется сигнал логической единицы, что обуславливает перевод буферных запоминающих устройств 24 и 25 в режим считывания информации, блоков 2 и 4 20 коммутации — в режим ввода информации в матричный газоразрядный индикатор 1 и подачи на вход синхронизации третьего счетчика 30 через второй коммутатор 23 сигнала с час- 25 тотой f ращ с третьего выхода генератора .14 .тактовых импульсов. При этом выходной код третьего счетчика обеспечивает развертку матричного газоразрядного индикатора 1 по зп оси М и синхронный с разверткой вывод информации из буферных sanoминающих устройств 24 и 25. Формирователь 5 вертикальных отрезков обеспечивает формирование кода котоУ 35 рый, поступая на входы второго блока 4 коммутации, обеспечивает зажигание вертикального ряда точек на панели, причем положение каждого ряда светящихся точек на оси М од- 41 нозначно соответствует коду счетчика 30. Количество точек в каждом вертикальном ряду определяется раз820 ностью хранящихся в ячейках данного адреса буферных запоминающих уст" ройств цифровых кодов, а положение по оси соответствует цифровому коду, формируемому формирователем

12 кода смещения по оси Y и добавляемому посредством сумматоров 10 и

11 к каждому из вводимых. в формирователь 5 вертикальных отрезков отсчету. Таким образом, на матричном индикаторе t индицируется форма зарегистрированного процесса. Затем на втором выходе третьего счетчика

30 появляется сигнал логического нуля, блоки 2 и 4 коммутации нереводятся в режим хранения информации в матричном газоразрядном индикаторе 1, и цикл обработки хранимой в блоке 15 памяти информации и ввода ее в буферное запоминающее устройство повторяется. Необходимый участок сигнала выбирается изменением цифрового кода, поступающего на входы 2 параллельного ввода информации второго счетчика 19 от формирователя 21 кода смещения по оси Х, а требуемый масштаб изображения (1;h) по оси Х вЂ” коэффициент том деления управляемого делителя

20 частоты, который задается формирователем 22 кода масштаба по оси Х, Таким образом, отображение формы широкополоснъм электрических сигналов, реализуемое с помощью предложенного устройства, позволяет оценить форму исследуемого широкополосного сигнала в общем виде при больших коэффициентах сжатия по оси когда информационная емкость массива данных превышает информационную емкость индикатора, т.е ° повысить информативность отображения фор" мы широкополосных сигналов.

/

ФФ

Ру

Фиг f

1! 5!820

Фи З

Составитель В. Королев

Редактор Т. Кугрышева Техред С.Легеза

Корректор А. Зимокосов

Заказ 2309/30 Тираж 703

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал IIIIII "Патент", г. Ужгород, ул. Проектная, 4