Преобразователь кода системы остаточных классов в позиционный код

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ПОЗИЦИОННЫЙ КОД, содержащий входной регистр , группы элементов И, сумматор и выходной регистр, выходы которого являются выходами преобразователя. информационные входы которого соединены с входами входного регистра, отличающийся тем что, с целью повышения быстродействия, в нем сумматор вьшолнен модульным и в него введены группа дешифраторов и группа шифраторов, входы шифраторов соединены с выходами соответствующих дешифраторов группы, входы которых соединены с выходами соответствуницей группы разрядов входного регистра, выходы каждого шифратора группы соединены е первыми входами элементов И соответствующей группы, вторые входы которых соединены с соответствующими входами модульного сумматора. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

4(5ц G 06 F 5/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3519548/24-24 (22) 07. 12.82 (46) 23.04.85. Бюл, ¹ 15 (72) А.П. Бо, r . ., С.Н. Хлевной, Н.И. Червяков и Н.И. Швецов (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

¹ 610102, кл. С 06 F 5/02, 1978.

2. Авторское свидетельство СССР № 594500, кл. G 06 F 5/02, 1977. (54) (57) ПРЕОБРАЗОВАТЕЛЬ КОДА

СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ПОЗИЦИОННЫИ КОД, содержащий входной регистр, группы элементов И, сумматор и выходной регистр, выходы которого являются выходами преобразователя, „„SU„„1151948 А информационные входы которого соединены с входами входного регистра, отличающийся тем, что, с, целью повышения быстродействия, в нем сумматор выполнен модульным и в него введены группа дешифраторов и группа шифраторов, входы шифраторов соединены с выходами соответствующих дешифраторов группы, входы которых соединены с выходами соответствующей группы разрядов входного регистра, выходы каждого шифратора группы соединены с первыми входами элементов И соответствующей группы, вторые входы которых соединены с с соответствующими входами модульного сумматора.

1151948

Изобретение относится к вычислительной технике и предназначено для преобразования кодов, представленных в системе остаточных классов (СОК), в позиционный двоичный код, для сопряжения периферийного обору дования с процессором, функционирующим в С0К.

Цель изобретения - повышение быстродействия преобразователя.

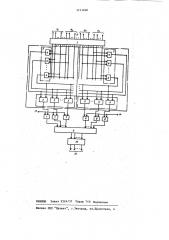

На чертеже приведена структурная .схема предлагаемого устройства,где в качестве примера представлено разбиение преобразователя на два канала.

Предлагаемое устройство содержит входной регистр 1, выходы которого подключены к входам дешифраторов 2 и 3, состоящих из элементов И 4, выходы которых подключены к соответ- 20 ствующим входам шифраторов 5 и 6, а выходы цифраторов через элементы

И 7 и 8 групп подключены к соответствующим входам модульного сумматора

9, выходы которого соединены с вхо- 25 дами выходного регистра 10. Информационные входы 11 и выходы 12 преобразователя соединены .с входами и выходами входного и выходного регистров. Управлякнщне входы 13 и 14 соединены с входами элементов И групп 7 и 8.

Предлагаемое устройство исполь-. зует следующий принцип рабаты.

Пусть задана СОК с основаниями

Р Р,...,Р„ . Для заданной СОК э э ° ° в и ° число А представим в диапазоне

0 — П P,. - 1, остатками

fsq

A(y gy ° ° ° ° dl p

04, Р1Р - 1;

0 - /2 4Р2РЗ вЂ” 1.

Для получения числа А в позиционном коде необходимо выполнить операцию (2) Представим заданную СОК по двум составным основаниям Р, и Р, причем

1j и

Р . Р, m mrl P. Р„

1"-2 и так как на выбранную СОК всегда накладывается условие взаимной простаты выбираемых оснований, то

P и Р представляются только произв ведениями г э P э, ° ° ° ° «P» причем вводим некоторое ограничение, нодожив Р„. Р,, Например, для СОК с ." i основаниями Р «Р <Р P эта достигается тем, что

P1g - «Р, Р э Рг РэРэ

TaK KaK Р, Р, . ° .,Р„- B3aRMHO прас».

1 . тые числа, то и (Р,;, Р ) 1, т,е. также числа. взаимно простые. Нри этом число А представится в новой

С0К остатками

A(Pq А) A(>k q ) (3) и, как легко видеть для приверженного примера, „ = (24, ), Рг (cd ° э), причем р, и д представляются в диа-. пазоне

A = „В + РгВг г„Р„, (4) где BljBi — ортогональные базисы для новой СОК, определяемой из соотношений

В„о (шо1 Р,.);

2j

В, «1 (шос1 P„);

"1

B =0 (mod P );

Bã, 1 (nKa P„) (5) и величикы В1 и В есть постоянные для конкретно заданной СОК;

r — величина ранга числа А.

Таким образом, процесс перевода числа из COK в позиционную систему счисления сводится к сведению числа остатков, которыин представляется число в СОК, к двум остаткам, которые в последующем преобразуются в позиционную систему счисления с помощью метода ортогональных базисов.

Аналогично разбиение системы оснований СОК может быть произведено и на большее число групп.

Предлагаемое устройство работает следующим образом.

В начальный момент времени число

А, представленное остатками1„i,. ...,« „, в одкопоэнционном коде о шинам 11 заносится во входной регистр 1. Состояние выходных шин входного регистра 1 дешифруется дешнфраторами 2 и 3. Причем число входов элементов И 4 определяется количеством основакий, входящих в данную группу. Tare, например, для приведенного примера с четырьмя основаниями с Р1 3, Р2 4 э 5, Р„ 7 разбиение на две группы мождешифратор 2

И 4„ — 0; 0

И4

И4> -2; 2

И4»-0; 3

И 4r — 1; 4

И4 -2; 5

И 4, - 0; 6

И 4 — 1; 0

° ° ° ° ° ° ° ° ° ° °

И4-2;6

10 з 1151 но сделать так: первая (Р„ = 3, Р = 7 ), вторая (Р2 = 4, P> = 5), при этом входы элементов И 4 дешифратора 2 подключаются следующим образом: 5

948 4

Єл = 21, Р Pg = 20, коэффициенты ортогонального базиса равны

В1 = 400 В2 = 21 тогда на выходе шифратора 5 представляется результат в двоичном коде преобразования (400 p, ) mod Р где р„ — остаток от числа по состав.ному основанию Р1Р+.

На выходе шифратора 6 представляется результат в двоичном коде преобразования (21 2 ) mod Р

Дешифратор 3

И4„-D- 0

И4,-1;1 и 4 — 2 2

3 °

И44-3; 3

И 4 — О» 4

И4, — 1; О

И 41 — 2; 1

И 4 - 3» 2

Ф В ° ° ° ° ° ° ° ° ° °

На выходах дешифраторов 2 и.3 коды в диапазонах 0 — (Р P . .— I ) пред- 45

1 j ставляются в однопозиционном коде.

Эти однопоэиционные коды преобразуются с помощью шифраторов 5 и б в двоичный код, соответствующий произведению однопозиционных кодов на 50 выходах дешифраторов 2 и 3 на величины коэффициентов ортогонального базиса для составных оснований

ЄРи Р2Р . Так для приведенного примера Р, = 3, Р2 4, Р3 = 5, 55, Р4 = 7 для составнь1х оснований (И4 -3 4

2о где группа цифр О;О показывает,что один вход элемента И 4, дешифратора

2 подключен к выходной нулевой шине З0 входного регистра 1, соответствукгщей основанию Р„ 3 а вторая цифра показывает, что второй вход эле11 И мента И 4 подключен к шине О

1 входного регистра 1, соответствующей З5 ! основанию Р4, = 7, входы элемента

И 4 дешифратора 2 подключены к шине 1" основания Р, 3 и шине "1" основания P = 7. Аналогичным образом подключаются входы других эле- 40 ментов И 4 дешифратора 2 и дешифратора 3. где p — остаток от числа по составг ному основанию Р2Р .

В данном случае выход элементов

g 4„ дешифратора 2 не подключен ни к одному входу шифратора 5. Выход элемента И 42 подключен к (400 1)

mod 420 = 11001000, входам шифратора 5. Выход элемента 4 подключен к (400 - 2)mod - 420 3801р 10111000, шифратора 5.

Аналогично соединены все оставшиеся выходы дешифратора 2, Таким же образом подключены и выходы дешифратора 3.

Через время большее, чем длительность переходных процессов в дешифраторах 2 и 3 и шифраторах 5 и 6, управляющему входу 13 подается импульс, который открывает группу элементов И 7 и тем самым операнд в двоичном коде, соответствующий величине (p„, В„) mod Р„ заносится в модульный сумматор. После записи первого операнда в модульный сумматор

9, сигнал с входа 13 снимается и подается разрешающий сигнал на вход

14. При этом открывается группа элементов И 8 и величина (Р В2) mod Р„ прибавляется в содержимому модульного сумматора 9. По окончании суммирования результат переносится в выходной регистр 10, с которого по выходам 12 снимается результат преобразования.

Таким образом, процесс преобразования в предлагаемом устройстве сводится в двум тактам преобразования.

1151948

Р ИИПИ Заказ 2324/37 тира у10 П

Филиал ППП Патент г Ужгород ул Проектная 4