Устройство для тестового контроля электромеханических блоков

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ТЕСТОВОГО КОНТРОЛЯ ЭЛЕКТРОМЕХАНИЧЕСКИХ БЛОКОВ, содержащее счетчик, блок регистрации , блок сравнения и блок управления , содержащий генератор одиночных сигналов, генератор тактовых сигналов ,, элемент НЕ и триггер, причем вход сброса и пуска устройства соединены соответственно с нулевым входом триггера и входом генератора одиночньо; сигналов блока управления, выход генератора одиночных сигналов со1вдинев с входами начальной установки счетчика и блока регистрации, информационнь1й вход устройства соединен с первым информационным входом блока регистрации и с первым информащюнHbiM входом блока сравнения, выход которого соединен с входом элемента НЕ блока управления, о т л и ч а ющ е е с я тем,: что, с целью повышения достоверности контроля, в устройство введены таймер, регистр начального адреса, группа элементов И и блок памяти, а в блок управленияпервый и второй элементы задержки, коммутатор, распределитель импульсов , три элемента И и элемент И-НЕ, причем выход генератора одиночных сигналов блока управления через пер|вый элемент задержки соединен с первым единичным входом триггера блока управления, единичный выход триггера блока управления соединен с входом обращения блока памяти и через второй элемент задержки блока управления - с входом запуска таймера и первыми входами элементов И грзплпы , выходы которых являются выходом устройства, выход элемента НЕ блока управления соединен с первыми входами первого и второго элементов И и элемента И-НЕ блока управления, первый, второй и третий информационные выходы блока памяти, выход адреса перехода, выход призйака услов . ного ;гестирова,ния и выкод признака п конца теста блока памяти соединены соответственно с информационным входом таймера, с вторым информационным входом блока сравнения, с вторыми входами элементов И группы, с пер ,вым информационным входом счетчика, с вторыми входами второго элемента И iH элемента И-НБ блока управления, СП с первьм зтаравлякнцйм входом коммутатора блока управления вьрсод реС0 гистра начального адреса соединен oi с вторым информационным входом счетчика , выход которого соединен с ядресным входом блока памяти и йторым информационным входом блока регистрации , выход таймера соединен с вторым управляюпцш входом коммутатора блока управления, шосод коммун татора блока управления соединен с тактовым входом распределителя импульсов , первый, второй, ретий и четвертый вглкоды которого соединены (соответственно с вторым входом первого элемента И, с вторым входом ус

(t9) (t I) СОЮЗ СОВЕТСКИХ ц ЮФЬ

РЕСПУБЛИК

4(51) G 06 F 11/26

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТВЙ (21) 35t9618/24-24 (22) 18 ° 10.82 (46) 23.04.85. Бвл. Ф 15 (72) В.А.Горячев и В.К.Цапулин (53) 681.3(088. 8) (56) Авторское свидетельство СССР

9 792258, кл. G 06 F 11/26, t980.

Авторское свидетельство СССР

N- 615492, кл. С 06 Р 15/46, 1978. (54)(57) УСТРОЙСТВО ДЛЯ ТЕСТОВОГО

КОНТРОЛЯ ЭЛЕКТРОМЕХАНИЧЕСКИХ БЛОКОВ, содержащее счетчик, блок регистрации, блок сравнения и блок управления, содержащий генератор одиночник сигналов, генератор тактовых сигналов,. элемент ИЕ н триггер, причем вход сброса и пуска устройства соединены соответственно с нулевым входом триггера и входом генератора одиночных сигналов блока управления, выход генератора одиночных сигналов соединен с входами начальной установки счетчика и блока регистрации, информационный вход устройства соединен с первым информационным входом блока регистрации и с первым информационным входом блока сравнения, выход которого соединен с входом элемента

НЕ блока управления,.о т л и .ч а вщ е e e я . тем,. что, с целью повышения достоверности контроля, в устройство введены таймер, регистр начального адреса, группа элементов

И и блок памяти, a s блок управления первый и второй элементы задержки, коммутатор, распределитель импульсов, три элемента. И и элемент И-НЕ, причем выход генератора одиночных сигналов блока управления через пер вый элемент задержки соединен с первым единичным входом триггера блока управления, единичный выход триггера блока управления соединен с входом обращения блока памяти и через второй элемент задержки блока управления — с входом запуска таймера и первьми входами элементов И группы, выходы которых являются выходом устройства, выход элемента НЕ блока управления соединен с первыми входами первого и второго элементов И и элемента И-НЕ блока управления, первый, второй и третий информационные выкоды блока памяти, выход адреса перехода, выход признака условного тестирования и вьцюд признака конца теста блока памяти соединены соответственно с информационным входом таймера, с вторым информационным входом блока сравнения, с вторыми входами элементов И группы, с пер1 вым информационным .входом счетчика, с .вторыми входами второго элемента И .и элемента И-HE блока управления, с первым управляющим входом коммутатора блока управления, выход регистра начального адреса соединен с вторым информационным входом счетчика, выход которого соединен с адресным входом блока памяти и вторым информационным входом блока регистрации, .выход таймера соединен .с

-вторым управляющим входом коммутатора блока управления, выход коммутатора блока управления соединен с тактовым входом распределителя импульсов, первый, второй, третий и четвертый выходы которого соединены соответственно с вторым входом íeðваго элемента И, с вторым входом ус

1 тановки нуля триггера, с третьими входом второго элемента И, с вторым единичным входом триггера блока управления, третий и четвертый выходы распределителя импульсов блока управления соединены соответственно с первым входом третьего элемента И и третьим управлякицим входом коммутатора блока управления, выход генератора тактовых сигналов блока управления соединен с информационным входом коммутатора блока управ1151973 ления, выход элемента И-НЕ блока управления соединен с вторым входом третьего элемента И блока управления

> выходы первого, второго и третьего элементов И блока управления соединены соответственно с тактовым входом блока регистрации с входом

J записи и счетным входом счетчика, четвертый управляющий вход коммутатора блока управления соединен с входом сброса устройства.

Изобретение относится к автоматизированному контролю и может быть использовано при тестовом контроле различных электромеханических объектов. %

Цель изобретения — повышение достоверности контроля.

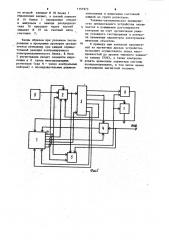

На фиг. 1 показана структурная схема предлагаемого устройства; на фиг.. 2 — структурная схема блока управления.

Устройство содержит .блок 1 управления, счетчик 2, блок 3 памяти, блок 4 сравнения, блок 5 регистрации, таймер 6, группу. элементов И 7, регистр 8 начального адреса. Блок . управления содержит генератор 9 одиночных сигналов, первый элемент 10 задержки, триггер 11, второй элемент

12 задержки, элемент ЙЕ 13, генера- 20 тор 14 тактовьас сигналов, коммутатор 15, распределитель 16 импульсов, элементы И 17 — 19, элемент . И-HK 20, выход.21 модификации адреса, выход 22 загрузки адреса, выход

23 начальной установки, выход . 24 установки контрольного набора, выход 25 разрешения контроля, выход 26 тактовых сигналов заниси.

Устройство работает в двух ре- 30 жимах: условного и безусловного тестирования.

В режиме безусловного тестирования в .блоке 1 управления нри поступлении сигнала пуска с входа генератор:9 одиночных сигналов формирует импульс, который проходит как сигнал начальной установки на входы : начальной установки счетчика 2 и блока 5 регистрации. По сигналу начальной установки в счетчик 2 за, носится адрес первого контрольного набора с регистра 8 начального адреса.

После этого в блоке 1 управления через время, определяемое элементом 10 задержки, взводится триггер 11, единичный сигнал с выхода которого разрешает обращение к блоку

3 памяти. На выходах последнего устанавливается первый контрольный набор.

При этом в таймер 6 с первого

:информационного выхода блока 3 памяти загружается код временного интервала, определяющий промежуток времени, в течение. которого контролируемый электромеханический блок должен выполнить операции, задаваемые входным контрольным набором.

Через время, необходимое для загрузки таймера, на выходе элемента 12 задержки блока 1 управления появляется сигнал, который осуществляет запуск таймера 6 и разрешает прохождение входного контрольного набора с третьего информационного выхода блока 3 памяти через элементы И 7: группы н@ выход устройства.

Ответная реакция контролируемого электромеханического блока, поступившая на вход устройства, сравнивается s блоке 4 сравнения с эталонным набором с второго информацион,,ного выхода блока 3 памяти. При обнулении таймера 6 возникающий на его выходе сигнал переполнения поступает на второй управляющий вход коммутатора 15 блока 1 управления.

1151973 l0

По этому сигналу в блоке 1 управления коммутатор 15 пропускает на свой выход, подключенный к входу распределителя 16, импульсы с генератора

14 тактовых сигналов. Распределитель %

16 распределяет эти импульсы последовательно по своим четырем выходам.

Импульс с первого выхода распределителя 16 стробирует на первом элементе И 17 блока 1 управления сигнал сравнения, который поступает .с выхода блока 4 сравнения через элемент НЕ 13 блока управления. Если

:на выходе, блока 4 сравнения в этот момент имеется сигнал несравнения, то в блоке 1 управления импульс с первого выхода распределителя 16 проходит через первый элемент И i7 на тактовый вход блока 5 регистрации, По этому импульсу в блоке 5 ре- 20 гистрации регистрируется через его первый информационный вход информация, прйсутствующая на входе устройства, н через его второй информационный вход - адрес контрольного на- бора со счетчика 2.

После этого в блоке i управления импульс с второго выхода распределителя 16 сбрасывает триггер ii, снимая сигнал обращения к блоку 3 30 памяти. Импульс с третьего распределителя 16 блока 1 управления проходит через третий элемент И 19 на счетный вход счетчика 2. При этом осуществляется модификация адреса, содержащегося в счетчике 2.

Импульс с четвертого выхода распределителя 16 блока 1 управления вновь взводит триггер 11, формируя очередной сигнал обращения к блоку 3 щ памяти. На выходах блока 3 памяти устанавливается следующий контрольный набор. Одновременно с этим импульс с четвертого выхода распределителя 16 блока 1 управления поступает на третий управляющий вход коммутатора 15. Последний отключает генератор 14 тактовых сигналов от распределителя- 16 импульсов до момента прихода очередного сиг- у нала переполнения таймера 6.

В последнем контрольном наборе на выходе признака конца теста блока 3 памяти присутствует признак конца теста (например, логический

"О"). При считывании последнего контрольного набора сигнал с выхода блока 3 памяти поступает на первый управляющий вход коммутатора 15 блока 1 управления и после снятия сигнала обращения к блоку 3 памяти коммутатор отключает генератор 14 тактовых импульсов от распределителя 16 импульсов.

Работа устройства после этого может быть возобновлена только при поступлении сигнала пуска с входа устройства.

Останов устройства может быть также осуществлен сигналом сброса с входа устройства. При этом триггер 11 блока управления устанавливается в нулевое состояние, снимая сигнал обращения к блоку памяти и коммутатор 15 блока управления отключает генератор 14 тактовых сигналов от распределителя f6.

В режиме условного тестирования работа устройства в части установки начального контрольного набора, осуществления контроля, регистрации результатов контроля и останова устройства по окончании тестиро. вания не отличается от режима безусловного тестирования. Отличие заключается в способе формирование ад.. реса очередного контрольного набора при обнаружении неисправностей в контролируемом .блоке. В контрольных наборах при условном тестировании содержатся признак условного тестирования (например логическая "1"}, которому соответствует выход признака условного тестирования блока памяти, и адрес к следующему контрольному набору, которому соответствует выход адреса перехода блока памяти.

При наличии сигнала на выходе признака условного тестирования блока 3 памяти и сигнала иесравнения на выходе блока 4 сравнения в блоке 1 управления открывается второй элемент И 18 и закрывается низким уровнем с выхода элемента И-НЕ 20 третий элемент И 19.

При этом импульс с выхода распределителя 16 импульсов блока 1 управления проходит через второй элемент И 18 и осуществляет занесение адреса перехода к следующему контрольному набору с выхода адреса перехода блока 3 памяти в счетчик 2.

Если сигнал несравнения на выходе блока 4 сравнения в процессе условного тестирования не возникает . 4.

r" б

1151973

3 то второй элемент И 18 блока управления закрыт, а третий элемент

И 19 блока 1 управления открыт и импульсы с выхода распредели" теля 16 проходят через третий элемент И 19 на счетный вход счетчика 2.

Таким образом при условном тести.ровании в программе проверки организуется ветвлейие при каждой отрица" тельной реакции контролируемого электромеханического блока..В блок

5 регистрации входят элементы индикации и П групп многоразрядных регистров (где O..- -число контрольных наборов) с последовательным режимом заполнения и индикации состояний каждой из групп регистров.

Технико-экономическое преимущество предлагаемого устройства заключается в повыщении достоверности контроля за счет организации режима условного тестирования и контроля временных параметров электромеханических объектов.

1О К примеру при контроле накопителей на магнитных дисках устройство позволяет осуществлять поиск неисправностей до уровня типового элемента замены (ТЭЗ), а также контролиБ ровать временные параметры системы позиционирования, в том.числе время перемещения магнитной головки.

1151973

Составитель И. Сигалов

Редактор Аг. Шандор Техред Т.Фанта Корректор Е.Poamo

Подписное

8Nt

8iyir

ЙаУ

ЮВР

ВхЮ

Заказ ?325/38 Тираж 710

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП ."Патент", r. Ужгород, ул. Проектная, 4

25