Устройство для защиты памяти

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ , содержащее накопитель, регистр адреса, регистр числа, блок сравнения , блок элементов И, причем вход накопителя подключен к выходу регистра адреса, вход которого является адресньм входом устройства , выходы накопителя соединены с входами регистра числа,первый выход которого подключен к одному входу блока элементов И, выход которого является информационным выходом устройства, второй выход регистра числа соединен с первым входом блока сравнения, один выход которого подключен к другому входу блока элементов И, другой выход блока сравнения является контрольньм выходом устройства, отличающееся тем, что, с целью повышения надежности устройства за . счет осуществления контроля последовательности обращения к ячейкам памяти , в него введены дополнительный регистр и элемент И, принем третий выход регистра числа подключен к одному входу элемента И, другой вход , которого является первым управляющим входом устройства, выход,элемен (Л та И соединен с первым входом дополнительного регистра, второй вход которого является вторым управляющим входом устройства, выход дополнительного регистра подключен к второму входу блока сравнения.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУ БЛИН (l9) (1)) ((5)) С 11 С 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТЬ9

ОПИСАНИЕ ИЗОБРЕТЕНИЯ н aBTOPCtlOMV СВИЦЕТНЪСтВУ (21) 3696308/24-24 (22) 31.01.84 (46) 23.04.85. Бюл. Ф 15 (72) А.С.,Горбенко.и В.И.Николаев (53) 681.327(088.8) (56) 1. Авторское свидетельство СССР

У 587510, кл. Q 11 С 29/00, 1976.

2. Каган Б.И. Электронные вычислительщае машины и системы.

M. "Энергия", 1979, с. 452-453, рис. 15-2 (прототип) ° (54) (57) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАИЯТИ, содержащее накопитель, регистр адреса, регистр числа, блок сравнения, блок элементов И, причем вход накопителя подключен к выходу регистра адреса, вход которого является адреснъв(входом устройства, выходы накопителя соединены е входами ре-, гистра числа, первый выход которого подключен к одному входу блока элементов И, выход которого является информационным выходом устройства, второй выход регистра числа соединен с первым входом блока сравнения, один выкод которого подключен к другому входу блока элементов И, другой выход блока сравнения является контрольнвв(выходом устройства, о т л ич а ю щ е е с я тем, что, с целью повышения надежности устройства эа счет осуществления контроля последовательности обращения к ячейкам памяти, в него введены дополнительный регистр и элемент И, прияем третий выход регистра числа подключен к одному входу элемента И, другой вход которого является первым управляющим входом устройства, выход.элемента И соединен с первым входом дополнительного регистра, второй вход которого является вторым управляющим входом устройства, выход дополнительного регистра подключен к второму входу блока сравнения.

1152043

Изобретение относится к запоминающим устройствам.

Известно устройство для защиты памяти, содержащее накопитель, блок контроля, блок управления, регистры, 5 элементы И, дешифратор, формирователь, которое предотвращает искаже1иие информации в памяти, а также несанкционированное чтение информации из защищенных областей памяти j1j .

Недостатком данного устройства является невысокая надежность защиты информации.

Наиболее близким к предлагаемому является устройство для защиты памяти по ключам, содержащее накопитель

° ключевой информации, адресные входы которого подключены к выходам старших разрядов регистра адреса, а 20 шыходы — к входам регистра слова, одни выходы которого подключены к входу блока сравнения, другие вы" ходы регистра слова соединены с первым вхрдом блока элементов И, второй 25 вход которого подключен к выходу блока сравнения f2) .

Недостатком известного устройства является низкая надежность защиты информации, поскольку ошибки адре-30 сации фиксируются только при обращении к ячейкам, находящимся за пределами выделенных программе блоков, и не обеспечивается фиксация ошибок адресации в пределах выделенных про3S

- грамме блоков памяти.

Кроме того, в пределах выделенных блоков памяти последовательность обращения к ячейкам не определена, и пользователь имеет доступ к любой ячейке выделенного блока в любой последовательности. Это также снижает надежность защиты информации и ограничивает функциональные воэможности устройства.

Цель изобретения — повышение надежности защиты информации за счет

:осуществления контроля последовательности обращения к ячейкам памяти.

Поставленная цель достигается тем,50 что в устройство для защиты памяти, содержащее накопитель, регистр адреса, регистр числа, блок сравнения, блок элементов И, причем вход накопителя подключен к выходу регистра 55 адреса, вход которого является адресным входом устройства, выходы накопителя соединены с входами реI гистра числа, первый выход которого подключен к одному входу блока элементов И, выход которого является информационным выходом устройства, второй выход регистра числа соединен с первым входом блока сравнения, один выход которого подключен к другому входу блока элементов И, другой выход блока сравнения является контрольным выходом устройства, введены дополнительный регистр и элемент И, причем третий выход регистра числа подключен к одному входу элемента И, другой вход которого является первым управляющим входом устройства, выход элемента И соединен с первым входом дополнительного регистра, второй вход которого является вторым управляющим входом устройства, выход дополнительного регистра подключен к второму входу блока сравнения.

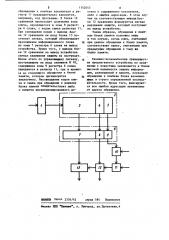

На чертеже представлена структурная схема устройства для защиты памяти.

Устройство содержит регистр 1 адреса, выходы которого подключены к входам накопителя 2, имеющего рабочую зону 3, зону 4 ключей и зону 5 замков. Выходы накопителя соединены с регистром 6 слова, который включает рабочую зону 7, зону 8 ключа и зону 9, замка, Выходы разрядов зоны замка соединены с входами. элемента И 10, выходы которого подключены к входам дополнительного регистра 11, выходы которого соединены с одним из входов блока 12 сравнения, другие входы которого подключены к выходам эоны ключей регистра слова, а выход соединен с одним входом блока 13 элементов И, другие входы которого подключены к выходам разрядов рабочей эоны регистра слова.

Устройство работает следующим образом.

При обращении к блоку памяти адрес из регистра t адреса поступает в накопитель 2. Из рабочей зоны 3 накопителя 2 считывается информаинонное слово на регистр 6 слова.. .)дновременно иэ эоны ключей и зоны 5 замков накопителя ключ и замок считываются и заносятся соответственно в зоны 8 и 9 регистра 6 слова. В регистре 11 в это время содержится код замка, считанный при предыдушем обращении к памяти. Перед, первым

043

ВНЮШИ 3« 2334/42 гяраж 584 Подписное

Филиал ППИ "Патаат", г. Ужгород, ул.Проектная,4

3 1152 обращением к ячейкам накопителя в регистр 11 предварительно заносится, например, код программы. В блоке 12 сравнения происходит сравнение кода ключа, находящегося в зоне 8 регистра 6 слова, с кодом замка регистра 11.

При совпадении кодов с выхода блока 12 сравнения на вход блока 13 поступает сигнал, который обеспечивает прохождение информационного слова 10 иэ зоны 7 регистра 6 слова на выход устройства. Кроме того, -с выхода блока 12 сравнения на выход устройства сигнал нарушения защиты не поступает.

После этого по управляв@уму сигналу, поступающему на вход элемента И 10, содержимое зоны 9 регистра 6 слова передается в регистр 11 где и хранится до следующего обращения к блоку памяти, которое организуется 20 аналогично. Несовпадение кодов ключа и замка при обращении к данному блоку памяти свидетельствует либо о попытке несанкционированного доступа к содержимому накопителя, либо о ощибке адресации. В этом случае на соответствующем выходе блока 12 сравнения формируется . сигнал нарушения защиты, который поступает на выход устройства.

Таким образом, обращение к ячейкам блока памяти возможно лищь в том случае, когда ключ, считанный при данном обращении к блоку памяти, соответствует замку, считанному при предыдущем обращении к тому же блбку памяти.

Технико-экономические преимущества предлагаемого устройства по сравнению с известным заключаются в более высокой надежности защиты информации, размещаемой в памяти, поскольку обращение к ячейкам блока возможно лищь в строго определенной последовательности. Кроме того, фиксируются все ощибки адресации независимо от адреса обращения.