Сумматор по модулю три

Иллюстрации

Показать всеРеферат

СУММАТОР ПО МОДУЛЮ ТРИ, содержащий первый и второй триггеры, прямые выходы которых соединены с соответстнзторр ми выходами сумматора, отличающийся тем, что, .с целью повышения быстродействия, сумматор содержит первый, второй и третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, причем К-входы и тактовые входы первого и второго триггеров соединены с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, Э-входы первого и второго триггеров соединены с выходами соответственно второго и третьего элементов ИСКЛЮЧАЮиЩЕ ИЛИ, первый вход первого элемента ИСКШЧАКМЦЕЕ ИЛИ соединен с первым входом сумматора и с первым входом третьего Элемента ИСКЛ10ЧАЮ1ЧЕЕ ШШ, второй вхрД которого соединен с прямьм выходом первого триггера, второй вход первого элемента ИСКЛЮЧАЮ1ЦЕЕ ИЛИ соединен с вторым входом сумматора и с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом второго триггера. О1 ОЭ СО 1C и

СОЮЗ СОВЕТСНИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИН

4(5Ц Г 06 F 7/49

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВ,Ф

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОтНЕЬГВй (21) 3659088/24-24 (22) 03.11.83 (46) 30.04.85, Бюл. к- 16 (72) H.Ä.Ðÿáóõà и В.С.Комисарук (53) 68 1.325.5(088.8) (56) 1. Авторское свидетельство СГСР

Р 54 1 175, -кл. G 06 F 1 1/00, 1976 .

2. Авторское свидетельство СССР

И - 890393, кл. G 06 F 7/72, 1980 (прототип) . (54) (5?) СУММАТОР ПО МОДУЛИ ТРИ, содержащий первый и второй триггеры, прямые выходы которых соединены с соответствующими выходами сумматора, отличающийся тем, что, .с целью повышения быстродействия, сумматор содержит первый, второй и третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, „„SU„„1153324 причем К-входы и тактовые входы первого и второго триггеров соединены с выходом первого элемента ИСКЛЮЧА10ЩЕЕ ИЛИ, Э -входы первого и второго триггеров соединены с выходами соответственно второго и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом сумматора и с первым входом третьего элемента

ИСКЛЮЧАЮЩЕЕ ИПИ, второй вход которо-го соединен с прямым выходом первого триггера, второй вход первого эле- мента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом сумматора и с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, второй вход которого соединен с прямым выходом второго триггера.

1153324

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах контроля.

Известен сумматор по модулю три, содержащий схемы совпадения, два триггера и два элемента ИЛИ, выходами подключенные к входам триггеров, первый вход первой схемы совпадения совместно с первым входом второй схемы совпадения, а второй вход совместно с первым входом третьей схемы совпадения являются входами сумматора по модулю три, вторые входы второй и третьей схемы совпадения подключены к входу первой схемы совпадения 11.

Недостатком такого сумматора по модулю три является низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является сумматор по модулю три, содержащий первый и второй триггеры, прямые выходы которых соединены с соответствующими выходами сумматора, первый и второй элементы ИЛИ, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, первый вход сумматора соединен с первыми входами первого и второго элементов И, второй вход сумматора соединен с первым входом третьего элемента И и вторым входом первого элемента И, инверсный выход которого соединен с вторыми входами второго и третьего элементов И, выходы. первого и второго элементов ИЛИ соединены соответственно со счетными входами первого и второго триггеров прямой выход первого триггера соединен с первыми входами четвертого и пятого элементов И, выходы которых соединены соответственно с первыми входами второго и первого элементов ИЛИ, выход третьего элемента И соединен с первыми входами шестого и седьмого элементов И и с вторым входом четвертого элемента И, выход второго элемента И соединен с первыми входами восьмого и девятого элементов И и вторыми входами пятого элемента И, инверсный выход первого триггера соединен с вторыми входами шестого, восьмого и девятого элементов И, выход последнего соединен с вторым входом второго элемента ИЛИ, инверсный выход второго триггера соединен с третьими входами четвертого .и пятого элементов И и вторым входом седьмого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, прямой выход второго триггера соединен с третьими входами шестого элемента И и восьмого эле10 мента И, выход которого соединен с третьим входом элемента И, выход шестого элемента И соединен с третьим входом второго элемента ИЛИ 2 3.

Недостатком известного сумматора по модулю три также является низкое

15 быс тродейс твие °

Быстродействие известного сумматора определяется временим последовательного срабатывания элементов самой длинной цепочки, состоящей из

20 первого, третьего, шестого элементов И, второго элемента ИЛИ, второго триггера, пятого элемента И, первого элемента ИЛИ и первого триггера, и Равно Т=бТ„ +2Т „, где Т„ - время срабатывания одного логического элемента; Т „ — время переключения триггера из одного состояния в другое.

Целью изобретения является повышенное быстродействие сумматора по модулю три.

Поставленная цель достигается тем, что сумматор по модулю три, содержащий первый и второй триггеры, З5 прямые выходы которых соединены с соответствующими выходами сумматора, содержит первый, второй и третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, причем Квходы и тактовые входы первого и вто.

"0 рого триггеров соединены с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, 3-входы первого и второго триггеров соединены с выходами соответственно второго и третьего элементов ИСКЛЮ"5 ЧАЮЩЕЕ ИЛИ, первый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом сумматора и с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, второй вход которого соединен с

50 прямым выходом первого триггера, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым. входом сумматора и с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй

55 вход которого соединен с прямым выходом второго триггера.

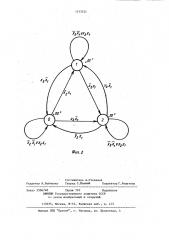

На фиг.1 приведена структурная схема предлагаемого сумматора по

1153324

3 модулю три, на фиг.2 — граф переходов сумматора по модулю три.

Сумматор по модулю три содержит первый 1,и второй 2 триггеры, элементы ИСКЛЮЧАИЩЕЕ ИЛИ 3-5, первый

6 и второй 7 входы, первый 8 и второй 9 выходы.

Работа сумматора по модулю три иллюстрируется графом переходов, приведенным на фиг.2. На графе номера вершин 0,1,2 соответствует значениям суммы по модулю три. Дугами показаны направления переходов при поступлении на входы сумматора по модулю три входной комбинации Х Х „, которая может принимать значения

"00" "01" "101 " 1 1" (X

Э У Э 2 ший с весом 2, а Х, — младший с весом 1 разряды комбинации). Сумма по модулю три кодируется состояниями второго и первого триггеров следующим образом: 0-"00", 1-"01", 2"10", Состояния триггеров обозначены соответственно символами à а (а — старший с весом 2, а — младший с весом 1 разряды суммы) .

В каждом такте работы триггеры находятся в определенном текущем состоянии а а „, соответствующем сумме по модулю три всех поступивших ранее входных комбинаций X X

Затем на первый 6 и. второй 7 входы поступают соответственно значения старшего Х и младшего Х„ разрядов входной комбинации ХэХ,. Под действием этих сигналов триггеры переходят в очередное состояние, которое определяет сумму по модулю три всех входных комбинаций, в том числе и поступивших в данном такте.

Из графа переходов видно, что при поступлении на входы комбинации

Х Х1, значения разрядов в которой . совпадают ("pp" или "11") сумма по модулю трн не изменяется и триггеры не изменяют своих состояний. В этом случае тактовый сигнал на С-входах обоих триггеров равен нулю. В осталь ных случаях тактовый сигнал на С-вхо1р дах триггеров равен 1 и триггеры могут изменять свои состояния при поступлении входных комбинаций.

Для устойчивой работы сумматора по модулю три необходимо, чтобы длительность сигналов входных комбинаций не превышала суммы времен срабатывания. одного триггера и одного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

Условимся считать, что время задержки сигнала в одном элементе И и одном элементе ИЛИ примерно одинаково и равна Т„, а время срабатывания триггера равно 2Т . Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ реализует функцию К=Х Х„чХэХ, и может быть реализован на двух элементах И и одном элементе ИЛИ, При этом время задержки сигнала в элементе ИСКЛЮЧАЮЩЕЕ

ИЛИ равно 2T . Быстродействие даннога сумматора па модулю три определяется временем задержки сигнала в одном элементе ИСКЙОЧАИ61ЕЕ ИЛИ и временем срабатывания триггера и равно

Т=2Тлэ+2Тл =4Тлэ "ак определено ранее, время срабатывания известного сумматора по модулю три равно Т=

=6Тлэ+2Т тг10Т лэ ° Тогда быстродействие предлагаемого сумматора по модулю три по сравнению с прототипом увеличивается в 2,5 раза.

ii53324

ХрХ Мрg

Составитель А.Степанов

Редактор И.Рыбченко Техред С.йовжий

Заказ 250б/40 Тираж 7i0 Подписное

ВНИИПИ Государственного комитета СССР пп делам изобретений и открытий

ii3035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ЛПП "Патент", r. Ужгород, ул. Проектная, 4