Устройство для многоканального контроля

Иллюстрации

Показать всеРеферат

1.УСТРОЙСТВО ДОЯ МНОГОКАНАЛЬНОГО КОНТРОЛЯ по авт.св.№ 841007, отличающееся тем, что, с целью повьшения достоверности контроля , в иего введены блок подтверждения сигналов отклонения к элемент ИЛИ.вьясод иперв вход элементаШШ подключены соответственно между входом блок а записи информации и первым выходом первого блока сравнения,между вторым выходом которого и третьим входом анализатора подключены соответственно первый вход и первый выход блока подтверждения сигналов отклонения , второй вход и второй выход которого подключены соответственно к втот рому выходу распределителя и второму входу элемента ИЛИ. 2.Устройство по п.1, о т л и ч аю щ е е с я тем, что блок подтверждения сигналов отклонения выполнен на триггерах и элементе И,-прямой выход первого триггера соединен с } -входом второго триггера, прямой выход которого соединен с объединеншфш D и 5-входами третьего триггера , инверсный выход которого соединен с первым входом элемента И, 1МХОД первого триггера подключен к шине нулевого потенциала, объеди-, ненные С-входы первого и третьего триггеров и второй вход элемента И, W и С-вход второго триггера являются соответственно первым и вторым входами блока подтверждения сигналов отклонений , выход элемента И и объединенные инверсный выход второго триггера и 5-вход первого триггера являются соответственно первым и вторым О1 ш гходами блока подтверждения сигна00 00 О9 лов отклонения.

(l9) (ll) СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

37 А

4(s» G 08 С 19/28 25/00

x-.

1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И 07HPbFA44 (61) 841007 (21) 3659083/24-24 (22) 03.11.83 (46) 30.04.85. Бюл. Ф 16 (72) 10.И.Васильев, В.Н.Козлов и Л.А.Тимухин (53) 621.398(088..8) (56) 1.Авторское свидетельство СССР

Ф 841007, кл.G 08 С 19/28, 1979 (прототип). (54)(57) 1.УСТРОЙСТВО-ДЛЯ МНОГОКАНАЛЬНОГО КОНТРОЛЯ по авт.св.9 841007, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, s него введены блок подтвер ждения сигналовотклонения иэлемент

ИЛИ,выход инервый вход элементаИ1% подключены соответственно между входом блоказаписи информациии первым выходом первогоблока сравнения, между вторым выходомкоторого и третьим входом анализатора подключены соответственно первый вход и первый выход блока подтверждения сигналов отклонения, второй вход и второй выход которого подключены соответственно к вто; рому выходу распределителя н второму входу элемента ИЛИ.

2,устройство по п.1, о т л и ч аю щ е е с я тем, что блок подтверждения сигналов отклонения выполнен на триггерах и элементе И,.прямой

I выход первого триггера соединен с ф -входом второго триггера, прямой выход которого соединен с объединенными 3 и 5-входами третьего триггера, инверсный выход которого соединен с первым входом элемента И, )вход первого триггера подключен к шине нулевого потенциала, объеди-, ненные С-входы первого и третьего триггеров и второй вход элемента И, и С-вход второго триггера являются соответственно первым и вторым входами блока подтверждения сигналов отклонени, выход элемента И и объединенные инверсный выход второго триггера и 5-вход первого триггера являются соответственно первым и вторым выходами блока подтверждения сигналов отклонения.

1153337

Изобретение относится к телемеханике и предназначено для выполнения функций многоточечного контроля датчиков с примерно равной частотой сигналов датчиков. 5

По основному авт.св.Ф 841007 известно устройство, содержащее последовательно соединенные тактовый генератор, распределитель, коммутатор, анализатор, блок памяти, первый и второй блоки сравнения и блок записи информации, выход которого соединен с вторым входом блока памяти, .выход анализатора соединен также с вторым входом второго блока сравнения, а второй выход анализатора соединен с первым входом блока выдачи сигналов об отклонении, второй вход которого соединен с выходом блока контроля, на вход которого под-20 ключен второй выход распределителя, второй выход блока контроля соединен с вторым входом анализатора, третий вход которого соединен с вторым выходом первого блока сравнения, вто->5 рой вход которого соединен с третьим входом блока контроля.

В устройстве-прототипе реализован дифференциальный контроль частоты сигналов датчиков друг относительно 30 друга, который существенно улучшает характеристики традиционных устройств, осуществляющих контроль частоты сигналов датчиков относительно постоянно заданного значения частоты (1 ).

Однако в устройстве возможно нарушение контроля при случайном сбое в блоке памяти. Например, если при кратковременном пропадании напряже- 40 ния питания. устройства в блоке памяти устанавливается значение частоты, относительно которой сигналы датчиков с номинальной частотой воспринимаются как аномальные, то формируется сигнал отклонения частоты и осуществляется запрет на перезапись в блоке памяти до срабатывания блока контроля, который срабатывает один раз на несколько циклов контро- 50 ля, при этом во внешние цепи выдается ложный сигнал отклонения, что снижает достоверность контроля.

Цель изобретения — повышение достоверности контроля.,55j

Поставленная цель достигается тем, что в устройство для многоканального контроля введены блок подтверждения сигналов отклонения и элемент ИЛИ,выход и первый вход элемента

ИЛИ подключены соттветственно между входом блока записи информации и первым выходом первого блока сравнения, между вторым выходом которого и третьим входом анализатора подключены соответственно первый вход и первый выход блока подтверждения сигналов отклонения, второй вход и второй выход которого подключены соответственно к второму выходу распределителя и второму входу элемента

ИЛИ.

Кроме того, блок подтверждения

I сигналов отклонения выполнен иа триггерах и элементе И, прямой выход первого триггера соединен сЭ -входом второго триггера, прямой выход которого соединен с объединенными

3,- и 5 -входами третьего триггера, инверсный выход которого соединен с первым входомэлемента И, В-вход первого триггера подключен кшине нулевого потенциала, объединенные С-входы первого и третьего триггеров и второй вход элемента И, и С-вход второго триггера являются соответственно первым и вторым входами блока подтверждения сигналов отклонения, выход элемента И и объединенные инверсный выход второго триггера и S-вход первого триггера являются соответственно первым и вторым выходами блока подтверждения сигналов отклонения.

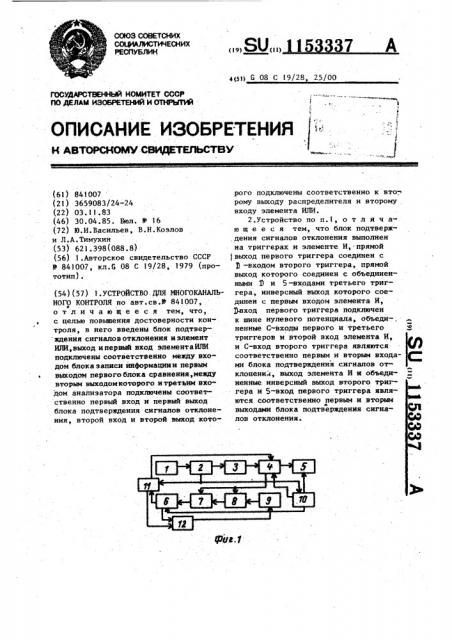

На фиг.l изображена структурная схема устройства для многоканального контроля; на фиг.2 — схема блока подтверждения сигналов отклонения; на фиг.3 — временная диаграмма работы блока подтверждения информации; на фиг.4 — схема анализатора.

Устройство для многоканального контроля (фиг.1) содержит тактовый генератор 1, распределитель 2, коммутатор 3, анализатор 4, блок 5 выдачи сигналов, первый блок 6 сравнения, второй блок 7 сравнения, блок 8 памяти, блок 9 записи информации, блок 10 контроля, блок 11 подтверждения сигналов отклонения и элемент

ИЛИ 12

Блок 11 подтверждения сигналов отклонения (фиг.2) содержит первый триггер 13, второй триггер 14, третий триггер 15 и элемент И lб. На временной диаграмме (фиг. 3 ) обозначены. а импульсы конца обхода с. выхода рас3 I l 53 пределителя 2; б — импульсы сигналов отклонения с выхода первого блока б,сравнения; в — сигнал на прямом выходе первого триггера 13; г — сигнал на прямом выходе второго триггеI .ра 14; д — сигнал на инверсном выходе третьего триггера 15; е — выходные импульсы.

Анализатор 4 (фиг.4) содержит формирователь 17, частотный дискримина- 10 тор 18, преобразователь 19 частотакад,элемент ИЛИ 20, триггер 21 одиноч-! ного отклонения, счетчик 22 группового отклонения, элемент И 23, генера тор 24 сигналов имитации и триггер !

25.

На фиг.3 цифрой обозначен случай, когда сигналы.отклонения повторяются в соседних циклах, т.е. сигнал действйтелен; цифрой П вЂ” когда сигнал отклонения не повторяется, т.е. сигнал является ложным.

Устройство работает следующим образом.

Тактовый генератор I задает скорость работы распределителя 2, код которого определяет адрес датчика,, подключенного через коммутатор 3 к входу анализатора 4, который осуществляет измерение сигнала датчика, и код измерения поступает на вход второго блока 7 сравнения, где происходит его сравнение с кодом, записанным в блоке 8 памяти иа предыдущем датчике. Результат сравнения 55 поступает sÜ первый блок 6 сравнения, где происходит еще одно сравнение с жестко заданной уставкой для разности. В случае, если разность меньme уставки, т.е. датчик имеет номи- 40 нальный сигнал, выдается сигнал на блок -9 записи информации для выделения импульса записи в блок 8 памяти, куда записывается код анализатора на этом датчике. Если же полученная 45 разность больше заданной уставки для разности, т.е. датчик имеет аномальный сигнал, то на блок 9 записи информации поступает запрет на запись в блок 8 памяти и в нем ос- 50 тается ранее записанное значение, при этом с первого блока 6 сравнения выдается сигнал на вход блока 11 подтверждения сигналов отклонения и запоминается в нем. Последующий им- 55 пульс конца обхода с распределителя

Я вызывает выдачу сигнала с выхода блока 11 подтверждения сигналов от337 4 клонения через элемент ИЛИ 12 на вход блока 9 записи для записи в блок 8 памяти кода сигнала первого датчика, который в этот момент подключен коммутатором 3 на вход анализатора 4 (после импульса конца об- хода коммутатор 3 подключает первый датчик к анализатору 4). В следующем цикле контроля сравнение сигналов датчиков осуществляется относйтельно первого датчика и в случае, если вновь формируется сигнал отклонения с выхода первого блока 6 сравнения, он проходит через блок 11 подтверждения сигналов отклонения на вход анализатора 4, который формирует по ним одиночные и групповые сигналы отклонения,и выцает их на блок 5 выдачи сигналов отклонения для выдачи во внешние цепи; групповые сигналы

no n отклонениям формируются после двух циклов контроля. Кроме того, в анализаторе 4 имеется абсолютный порог по частоте, ниже которого формируется сигнал отклбнения, даже если с первого блока 6 сравнения сигнала не поступает. Это сделано для того, чтобы, если все датчики начинают уменьшать частоту одновременно, например, при снятии напряжения питания, то сигнал с первого блока 6 сравнения не поступает,,но сигналы отклонения в анализаторе 4 формируются по абсолютному порогу. Выходной импульс конца обхода с распределителя поступает также на вход блока 10 контроля, который после прихода определенного числа таких импульсов осуществляет автоматический контроль работоспособности устройства. Для этого с выхода блока 10 контроля на вход анализатора 4 поступают сигналы, имитирующие аномальные сигналы датчиков, и выдается сигнал запрета на вход блока 5 выдачи сигналов отклонения на выдачу сигналов во внешние цепи. Анализатор 4 по сигналам с блока IO формирует сигналы отклонения и после выбора всех сигналов прекращает автоконтроль. При отсутствии контроля всех сигналов отклонения блок 5 выдачи сигналов отклонения выдает во внешние цепи сигнал неисправности работы устройства.

Анализатор 4 работает следующим образом. Сигнал датчика, подключенного на контроль коммутатором 3, поступает на вход формирователя !7, сигнал в, который, поступая на 3— вход второго триггера 14, подготавли». вает его к срабатыванию. Третий триггер 15 сохраняет исходное состояние. При приходе следующего импульса а конца обхода на вход. второго триггера !4 последний срабатывает и выдает с прямого выхода нулевой сигнал г, который поступает на 3 -вход третьего триггера 15, подготавливая его к срабатыванию, С инверсного выхода второго триггера 14 при этом выдается сигнал "1" на установочный

S -- вход первого триггера,,возвращая его в исходное состояние, и на вход элемента ИЛИ 12 для передачи на вход блока 9 записи для осуществления записи в блок 8 памяти кода первого датчика. В следующем цикле. контроля происходит сравнение кодов всех контролируемых датчиков с кодом первого датчика и в случае, если с выхода первого блока 6 сравнения поступает повторно сигнал б отклонения (случай 1, фиг.З), происходит срабатывание третьего триггера !5, который выдает с инверсного выхода сигнал д на вход элемента И 16, который разрешает прохождение сигналов отклонения на выход элемента; И 16 е и на вход анализатора. Следующим импульсом а конца обхода триггер 14 возвращается в исходное состояние; и устанавливает триггер 15 также в исходное состояние по 5 -входу.

Ксли подтверждения сигнала отклонения с выхода первого блока сравнения во втором цикле контроля не поступает (случай П, фнг.З ), то срабатывания третьего триггера не происходит и ложный сигнал отклонения исключается, а следящим импульсом а конца обхода устанавливаются в исходное состояние триггер 14 и блок 1! подтверждения информации, Таким образом, в случае формирования сигнала отклонения частоты осуществляется проверка этого сигнала в следующем цикле контроля всех датчиков, но в качестве опорного значения записывается значение частоты первого датчика, при этом ложный сиг.т вал об отклонении частоты в следующем цикле ие подтверждается, а истинный подтверждается, чем н достигается повышение достоверности контроля.

Технико-экономическая эффективность предлагаемого технического решения

В !!5ЗЗЗ7 где происходит формирование. прямоугольных импульсов постоянной амплитуды из синусоидального .сигнала датчика. Сформированный сигнал поступает на вход частотного дискриминато- 5 ра 18 и на вход преобразователя 19 частота — код. Частотный дискримина- . тор имеет постоянно установленный порог по частоте, по достижении .которого частотой датчика выцаются сигна->о. лы с выхода частотного дискриминатора 18 через элемент ИЛИ 20 на вход триггера 21 одиночного отклонения и . на вход счетчика 22 групповых отклонений. При срабатывании триггер 21 и 15 счетчик 22 выдают сигналы по одному разделенному каналу на вход блока 5 выдачи сигналов отклонения. С выхода преобразователя 19 частота код закодированный частотный сигнал выдает-36 ся на вход второго блока У сравнения и на вход блока 8 памяти. Импульсный сигнал с выхода блока 10 контроля поступает на вход триггера 25 и устанавливает его в состояние, при кото- 25 ром триггер 25 выдает сигнал, запрещающий прохождение сигналов датчиков через Формирователь 17 и разрешающий сигнал на генератор 24 сигналов имитации для формирования сигналов, З0 имитирующих сигналы отклонения, и выдачи их на входы частотного дискриминатора 18 и преобразователя 19 частота — код. После набора сигналов отклонения с выхода триггера 21 оди- у ночного отклонения и выхода счетчика 22 групповых отклонений через элемент И 23 на вход триггера 25 поступает сигнал, возвращающий его в исходное состояние, при котором îè 4а выдает сигнал, разрешающий прохождение сигнала датчика через формирователь 17, и сигнал., запрещающий выдачу сигналов имитации с генератора 24 сигналов имитации. 45

Работа блока 11 нодтверждеиия сигналов отклонения иллюстрируется временной диаграммой на фиг.З.

В исходном состоянии на прямых выходах. всех триггеров — сигнал "1" на счетный С-вход второго триггера

14 поступают импульсы а конца обхода с выхода распределителя. Сигнал б отклонения с выхода первого блока сравнения поступает на счетные C-вхо- ды первого и третьего триггеров. Первый триггер срабатывает, на его прямом выходе устанавливается нулевой

115ЗЗЗ

ЮИ а

Рие. 4

Составитель И.Бочарова

Редактор И. Рыбченко . Техред И.Асталоа Корректор В. Г ц ня®.

Заказ 2508/41 Тираж 611 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035,Москва,Ж-35,Раушская наб.,д.4/5

Филиап ППП "Патент",г.ужгород,ул.Проектная,4 заключается в сокращении ложных сигналов отклонения частоты, которые вызывают срабатывание системы защиты оборудования, на котором установлены датчики. Это приводит к сокращению простоя, остановок и пусков оборудо. вания, отрицательно сказывающихся на производительности, качестве и ресурсе эксплуатации оборудова5 ния.