Устройство стабилизации сигнала цветного изображения

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО СТАБИЛИЗАЦИИ СИГНАЛА ЦВЕТНОГО ИЗОБРАЖЕНИЯ, содержащее последовательно соединенные аналого-цифровой преобразователь (АЦП), вход которого подключен к выходу формирователя сигнала цветного изображения, блок памяти, цифроаналоговый преобразователь (ЦАП), первую линию задержки и первый коммутатор , второй вход которого подключён к выходу 1ДА11, а также последовательно соединенные блок вьщеления синхронизирующего сигнала, вход которого подключен к выходу форми- . рователя сигналацветного изображения , первьй формирователь синхронизирующих сигналов и блок управления., к второму входу которого подключен второй выход блока вьщеления синхронизирующего сигнала, а первый и второй выходы формирователя эталонного синхронизирующего сигнала подХЛючены соответственно к третьему входу блока управления и четвертому входу блока управлений через второй формирователь синхронизирующих сигналов , при этом выход блока управления подключен к второму входу блока памяти, а выходы первого и второго формирователей синхронизирующих сигналов подключены к вторым входам соответственно АЦП и ЦАП, при этом третий и четвертый выходы блока выделения синхронизирующего сигнала подключены к первому и второму входам блока сравнения через соответствующие первьй и второй фазовые детекторы, третий и четвертьй выходы формирователя эталонного синхронизирующего сигнала подключены к третьему и четвертому входам блока сравнения через соответствующие третий и четвертый фазовые детекторы, а выход третьего фазового детектора и первый выход блока сравнения соот§ ветственно подключены к первому и (Л второму входам элемента И, выход которого подключен к управляющему входу первого коммутатора, при этом пятый выход формирователя эталонного 1 синхронизирующего сигнала подключен к первому входу первого сумматора, а выход первого коммутатора подключен к входу блока разделения сигналов СП яркбсти и цветности, отличаю00 СХ) щееся тем, что, с целью повыщения точности стабилизации сигнала, СП N9 введены последовательно соединенные вторая линия задержки, второй сумматор и второй коммутатор, выход которого подключен к второму входу первого сумматора, а также введены последовательно соединенные третья линия задержки, третий сумматор и третий коммутатор, выход которого подключен к третьему входу первого сумматора через введенный четвертый коммутатор, при этом первый и второй выходы блока разделения сигналов яркости и цветности подключены к входам второй

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИ Н

1(51) Н 04 N 5/76

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H flATEHTY

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

f10 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЦТИЙ (21) 2754148/24-09 (22) 06.04.79 (31) 41421/78 (32) 07.04.78 (33) Япония (46) 30.04.85. Бюл. N - 16 (72) Иицусиге Татами (Япония) (71) Сони Корпорейшен (Япония) (53) 621.39?(088.8) (56) 1. Колин К.Т. Основы телевидения. M. "Связь", 1972, с. 321-322 (прототип). (54)(57) УСТРОЙСТВО СТАБИЛИЗАЦИИ

СИГНАЛА ЦВЕТНОГО ИЗОБРАЖЕНИЯ, содержащее последовательно соединенные аналого-цифровой преобразователь (АЦП), вход которого подключен к выходу формирователя сигнала цветного иэображения, блок памяти, цифроаналоговый преобразователь (ЦАП), первую линию задержки и первый коммутатор, второй вход которого подключен к выходу ЦАП, а также последовательно соединенные блок вьщеления синхрониэирующего сигнала, вход которого подключен к выходу формирователя сигнала цветного изображения, первый формирователь синхрони- зирующих сигналов и блок управления, к второму входу которого подключен второй выход блока выделения синхронизирующего сигнала, а первый и второй выходы формирователя эталон- ного синхронизирующего сигнала подКлючены соответственно к третьему входу блока управления и четвертому входу блока управленйя через второй формирователь синхронизирующих сигналов, при этом выход блока управления подключен к второму входу блока памяти, а выходы первого и второго

„„SU „„1153852 A формирователей синхронизирующих сигналов подключены к вторым входам соответственно АЦП и ЦАП, при этом третий и четвертый выходы блока выделения синхронизирующего сигнала подключены к первому и второму входам блока сравнения через соответствующие первый и второй фазовые детекторы, третий и четвертый выходы формирователя эталонного синхронизирующего сигнала подключены к третьему и четвертому входам блока сравнения через соответствующие третий и четвертый фазовые детекторы, а выход третьего фазового детектора и первый выход блока сравнения соо1ветственно подключены к первому и второму входам элемента И, выход которого подключен к управляющему входу первого коммутатора, при этом пятый выход формирователя эталонного

1синхронизирующего сигнала подключен к первому входу первого сумматора, а выход первого коммутатора подключе к входу блока разделения сигналов яркЬсти и цветности, о т л и ч а ющ е е с я тем, что, с целью повышения точности стабилизации сигнала, введены последовательно соединенные вторая линия задержки, второй сумматор и второй коммутатор, выход которого подключен к второму входу перво

ro сумматора, а также введены последовательно соединенные третья линия задержки, третий сумматор и третий коммутатор, выход которого подключен к третьему входу первого сумматора через введенный четвертый коммутатор при этом первый и второй выходы блока разделения сигналов яркости и цветности подключены к входам второй

1153852 и третьей линии задержки и к вторым входам соответственно второго и третьего сумматоров и второго и третьего коммутаторов, к управляющим

Изобретение относится к области телевидения, преимущественно при кор-. рекции цветовых телевизионных сигналов при воспроизведении их с видеомагнитофона с последующей передачей на видеоконтрольное устройство.

Известно устройство стабилизации сигнала цветного изображения, содержащее последовательно соединенные аналого-цифровой преобразователь (ЛЦ!!) rð вход которого подключен к выходу формирователя сигнала цветного изображения, блок памяти, цифроаналоговый преобразователь (!(ЛП), первую линию задержки и первый коммутатор, второй вход которого подкпючен к выходу ЦЛП, а также последовательно соединенные блок выдеш ния синхронизирующе го сигнала, вход которого подключен к выходу формирователя сигнала цветного изображения, первый формирователь синхронизирующих сигналов и блок управления, к второму входу которого подключен второй выход блока выдепе— пия синхронизирующего сигнала, а 25 первый и второй выходы формирователя эталонного синхронизирующего сигнала подключены соответственно к третьему входу блока управления и четвертому входу блока управления через второй

ЗС формирователь синхронизирующих сигналов, при этом выход блока управления подключен к второму входу блока памяти, а выходы первого и второго формирователей синхронизирующих сигналов подключены к вторым входам соответственно АЦП и ЦАП, при этом третий и четвертый выходы блока выделения синхронизирующего сигнала подключены к первому и второму входам блока сравнения через соответствующие первый и второй фазовые детекторы, а третий и четвертый выходы формирователя эталонного синхронизирующего сигнала подключены к третьему и четвертому входам блока сравнения

45 входам которых подключен первый выход блока сравнения, второй выход которого подключен к управляющему входу четвертого коммутатора. через соответствующие третий и четвертый фазовые детекторы, а выход третьего фазового детектора и первый выход блока сравнения соответственно подключены к первому и второму входам элемента И, выход которого подключен к управляющему входу первого коммутатора, при этом пятый выход формирователя эталонного синхронизирующего сигнала подключен к первому входу первого сумматора, а выход первого коммутатора подключен к входу блока разделения сигналов яркости и цветности (1!.

Однако в известном устройстве использование квазикадрового синхронизирующего видеосигнала приводит к тому, что изображение «а экране монитора смещается вверх или вниз при выпадении сигнала цветного изображения.

Цель изобретения — повышение точности стабилизации сигнала.

Для достижения цели в устройство стабилизации сигнала цветного изображения, содержащее последовательно соединенные аналого-цифровой преобразователь, вход которого подключен к выходу формирователя сигнала цветного изображения, блок памяти, цифроаналоговый преобразователь, первую линию задержки и первый коммутатор, второй вход которого подключен к выходу ЦАП, а также последовательно соединенные блок выделения синхронизирующего сигнала, вход которого подключен к выходу формирователя сигнала цветного изображения, первый формирователь синхронизирующих сигналов и блок управления, к второму входу которого подключен второй выход блока выделения синхронизирующего сигнала, а первый и второй выходы формирователя эталонного синхронизирующего сигнала подключены соответственно к третьему входу блока

1153852 управления и четвертому входу блока управления через второй формирователь синхронизирующих сигналов, при этом выход блока управления подключен к второму входу блока памяти, а выходы первого и второго формирователей синхронизирующих сигналов подключены к вторым входам соответственно АЦП и ЦАП, при этом третий и четвертый выходы блока вьщеления сии в 10 хронизирующего сигнала подключены к первому и второму входам блока сравнения через соответств-ющие первый и второй фазовые детекторы, третий и четвертый выходы формирова— теля эталонного синхронизирующего сигнала подключейы к третьему и четвертому входам блока сравнения через соответствующие третий и четвертый фазовые детекторы, а выход третьего 20 фазового детектора и первый выход блока сравнения подключены к первому и второму входам элемента И, выход которого подключен к управляющему входу первого коммутатора, при этом пятый выход формирователя эталонного синхронизирующего сигнала подключен к первому входу первого сумматора, а выход первого коммутатора подключен к входу блока разделения сигналов ЗО яркости и цветности, введены последовательно соединенные вторая линия задержки, второй сумматор и второй коммутатор, выход которого подключен к второму входу первого сумматора, 35 а также введены последовательно соединенные третья линия задержки, третий сумматор и третий коммутатор, выход которого подключен к третьему входу первого сумматора через введен-4р ный четвертый коммутатор, при этом первый и второй выходы блока разделения сигналов яркости и цветности подключены к входам второй и третьей линии задержки и к вторым входам соот- 45 ветственно второго и третьего сумматоров и второго и третьего коммутаторов, к управляющим входам которых подключен первый выход блока сравнения, второй выход которого подключен к управляющему входу четвертого коммутатора.

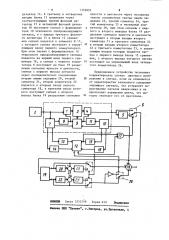

На чертеже изображена структурная электрическая схема устройства стабилизации сигнала цветного изображе- 55 ния.

Предложенное устройство содержит

АЦП 1, формирователь 2 сигнала цветного изображения, блок 3 памяти, ЦАП 4, первую линию задержки 5, первый коммутатор 6, блок 7 выделения синхронизирующего сигнала, первый формирователь 8 синхронизирующих сигналов, блок 9 управления, формирователь 10 эталонного синхронизирующего сигнала, второй формирователь 11 синхронизирующих сигналов, блок 12 сравнения, первый фазовый детектор

13, второй фазовый детектор 14, третий фазовый детектор 15, четвертый фазовый детектор 16, элемент И 17, первый сумматор 18, блок 19 разделения сигналов яркости и цветности, вторая линия задержки 20, второй сумматор 21, второй коммутатор 22, третья линия задержки 23, третий сумматор 24, третий коммутатор 25, четвертый коммутатор 26.

Устройство работает следующим образом.

fla ЛЦП 1 с формирователя 2 сигнала ,цветного изображения поступает демодулированный по частоте сигнал системы НТСК. Такой сигнал содержит сигналы кадровой и строчной синхрониl зации и в дополнение к видеосигналурадиоимпульс. Однако указанный сигнал цветного изображения поступает от формирователя 2 сигнала цветного изображения искаженным. С выхода

АЦП 1 цифровой сигнал цветного изображения подается в блок 3 памяти, с выхода которого этот сигнал через

ЦАП 4 и первую линию задержки 5 поступает на первый коммутатор 6.

Одновременно сигнал цветного изображения с формирователя 2 сигнала цветного изображения поступает на блок 7 вьщеления синхронизирующего сигнала, с выхода которого сигнал поступает через первый формирователь

8 синхронизирующих сигналов на блок

9 управления, на второй вход которого поступает сигнал с формирователя

10 эталонного синхройизирующего сигнала через второй формирователь

11 синхронизирующих сигналов. Полученный в результате сравнения сигнал с блока 9 управления поступает на соответствующий вход блока 3 памяти.

При этом сигналы с соответствующих выходов блока 7 вьщеления синхронизирующего сигнала поступают на первый и второй входы блока 12 сравнения через соответствующие первый фазовый детектор 13 и второй фазовый

1153852

ВНИИПИ Заказ 2552/46 Тираж 659 Подписное

Фндиап ППП "Патент", г.Узгород, ул.Проектная, 4 детектор 14. К третьему и четвертому входам блока 12 сравнения через соответствующие третий фазовый детектор 15 и четвертый фазовый детектор 16 поступает сигнал с формирователя 10 эталонного синхронизирующего сигнала, и с выхода третьего фазового детектора 15 и блока 12 сравнения сигнал подается к элементу И 17, с которого сигнал поступает к управляющему входу первого коммутатора 6.

Цри этом сигнал с формирователя 10 эталонного синхронизирующего сигнала подается на первый вход первого сумматора 18, а сигнал с первого коммутатора 6 поступает на блок 19 разделения сигналов яркости и цветности, сигнал с первого выхода которого через последовательно соединенные вторую линию задержки 20, второй сумматор 21, второй коммутатор 22 подается к второму входу первого сумматора 18, к третьему входу которого поступает сигнал с второго выхода блока 19 разделения сигналов яркости и цветности через последова тельно соединенные третью линию задержки 23, третий сумматор 24, третий коммутатор 25 и четвертый коммутатор 26, при этом сигналы с первого и второго выходов блока 19 разделения сигналов яркости и цветности поступают к вторым входам второго сумматора 21 и третьего сумматора 24

10 и вторым входам второго коммутатора

22 и третьего коммутатора 23, к управляющим входам которых подается сигнал с первого выхода блока 12 сравнения, с второго выхода которого сигнал

15 поступает на управляющий вход четвертого коммутагора 26.

Предложенное устройство позволяет корректировать сигнал цветного изоб20 ражения в случае, .если он отличается от характеристик эталонного синхронизирующего сигнала, что устраняет подергивание сигнала вверх-вниз и не происходит нарушения цвета, что вы25 годно отличает его от прототипа.