Преобразователь двоичного кода в код системы остаточных классов

Иллюстрации

Показать всеРеферат

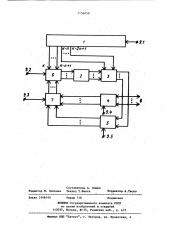

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В КОД СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ , содержащий первый и второй регистры , блок умножения на константу по модулю Р; ( 1,2, .. ., Р ) , сумматор по модулю Р; и (k + O-paa-рядный входовой регистр, причем выходы старших разрядов входного регист ра, где (n-t-1) г lopj Р , соединены с информационными входами первой группы коммутатора, информационные входы второй группы которого соединены с соответствующими выходами второго коммутатора, информационные входы первой и второй групп которого соединены соответственно с выходами первого и второго регистров, информационные входы которых являются выходом преобразователя и соединены с соответствующими выходами сумматора по модулю Р; , входы первого слагаемого которого соединены с выходами блока умножения на константу по модулю Р, , входы которого соединены с соответствующими выходами первого коммутатора , выход (V-n)-ro разряда входного регистра соединен с первым входом второго слагаемого сумматора по модулю Р; , вход сдвига входного регистра, входы приема информации первого и второго регистров, управляющие входы первого и второго коммутаторов соединены с тактовым вхо дом преобразователя, отличающийся тем, что, с целью повышения быстродействия, выходы разрядов с (k-rt-l)-ro по (k-2 О-й входного регистра соединены соответственно с входами с второго по второго слагаемого сумматора C7I по модулю . ф о СП 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

4(51) С 06 F 5 00 авала ц

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

{ 21) 3? 11969/24-24 (22) 11.03.84 (46) 15.05..85. Бюл. N- 18 (72) В.А.Иванченко и П.Л.Прокопьев (53) 681.3(088.8) (56) Авторское свидетельство СССР

Р 983701, кл. G 06 F 5/00, 1981.

Авторское свидетельство СССР

Я 1001079, кл. С 06 F 5/00, 1981. (54) (57) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО

КОДА В. КОД СИСТЕМЫ ОСТАТОЧНЫХ КЛАСС08, содержащий первый и второй регистры, блок умножения на константу по модулю Р; (i f,?, ..., Р ), сумматор по модулю Р; и (1+1)-разрядный входовой регистр, причем выко. ды старших разрядов входного регист ра, где (и+1) 3 1оя Р„, соединены с информационными входами первой группы коммутатора, информационные входы второй группы которого соединены с соответствующими выходами второго коммутатора, информационные входы первой и второй групп которого соединены соответственно с выходами пер„„SU„„1156058 A вого н второго регистров, информационные входы которых являются выходом преобразователя и соединены с соответствующими выходами сумматора по модулю P;, входы первого слагаемого которого соединены с выходами блока умножения на константу но модулю Р;, входы которого соединены с соответствующими выходами первого коммутатора, выход (k -п)-го разряда входного регистра соединен с первым входом второго слагаемого сумматора по модулю Р„, вход сдвига входного регистра, входы приема информации первого и второго регистров, управляющие входы первого и второго коммутаторов соединены с тактовым входом преобразователя, о т л и ч аю шийся тем, что, с целью повышения быстродействия, выходы разрядов с (k-n-1)-го по (k-2 +1 -й входного регистра соединены соответственно с входами с второго по

11-й второго слагаемого сумматора по модулю Р;

1156058

Составитель А. Клюев

Редактор И. Циткина Техред Т.Фанта Корректор А.Тяско

Закаэ 3146/45 ир 71О Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и откритий

113035, Москва, Ж-35, Рауаская наб., д. 4/5

Филиал ППП "Патент", r. Уагород, ул. Проектная, 4