Устройство для умножения

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО Гщя , содержащее матрицу элементов И и матрицу одноразрядных сумматоров, причем первые входы элементов и; -го столбца матридь

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСтИЧЕСНИХ

РЕСПУБЛИН

4(<1) G Об F 7/52

-Ъ .- ЫаБМа а;.,ц

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНЯТИЙ (2i) 3528778/24-24 (22) 24. 12.82 (46) 15.05.85. Вюп. Ф 18 (72) Л,В.Дербунапич и В. В.И:ат: и:.а (71) Харьковский ардена 1енn!!à политехнический институт им, В. 1. Лап !п (53) 681.325(088.8) (56) A.*-зтарскае свидетельства СГ(,Р

Ф 817705, кл С 06 F 7/52, 19 9,.

Папернов А.A. Л; гическпе аснань;

ЦВТ. И., Советское радио. i9; 2, с. 218-219, рис. 9. (54) (57} УСТРОЙСТВО ДЛЯ У 111ОЯЕ)1:*,.Я, содержащее матрицу =,nåìåíòoâ И;л матрицу одноразрядных cóììàòopoâ причем первые входы элементов И:, -га

i толбца матрицы (i =-1, ..., п

П вЂ” количество разрядан первого операнда) соединены с входам саот— ветствующега разряда пернагс операнда устройства, нтарые входы элементов И ) -A строки матрицы (1

2р; Р— произвольное целое число) соединены с ссстветств ющим входом задания второго операнда устройства, выходы элементов И < -й строки матрицы соединены с первы;и информационными вхацами саатвеTствующих однаразрядны сумма. 1-.;ан соответствующей строки матрицы, выход переноса каждого однар"-.ã:ðÿäíîão сумматора -га столбца мат HU!:; соединен с вторым информационным входам последующего одноразряцнсгo сумматора того же. столбца матрицы, выход суммы % -го одноразрядного сумматора 1 -й строки матрицы соединен с третьим информационным входам

В (<-1)-го одноразрядного сумматора

„„SU„„ iЫ ВЫ A (1+1) -й строки матрицы, выходы суммы одноразрядных сумматоров первого столбца матрицы являются выходами устройства, о т л и ч а ю щ е е с я тем, чта, с целью упрощения устройства, каждый одноразрядный сумматор р-й и 2р-й строк матрицы содержит девять злементов И, два элемента

ИЛИ, четыре элемента HF. и элемент задержки, при-ем выходы элементов И с первого по пятый соединены с входами первого злемента ИЛИ, выход катарага соединен с выходом суммы адпаразрялнага сумматора, выходы элементов И с шестого по девятыи саединепь. с входами второго элемента .РЛИ, выход,атсрога соединен с выходам переноса одноразрядного сумматора, вход гервага элемента HE coe— дин-"н с первым информационным вхсдам одноразрядного сумматора и первыми вхадамн первсга, четвертого, седьмого

H васьмагo элемен ион И, выход первого элемента НЕ соединен с первыми входами второго и третьего элементов И, вход второго элемента НЕ соединен с вторым информационным входом одноразряднога сумматора, вторыми входами первого, третьего и восьмого элементов И и первым входам шестого элемента И, выход второго элемента HE соединен " вторыми входами второго и четвертого элементов И, вход третьего элемента НЕ соединен с третьим инфармацианньвл входом одноразрядного .сумматора, вторыми входами шестого и седьмого элемен;os И и с третьими входами первого и второго элементов

И, выход, третьего элемента HF. соеди нен с третьими входами третьего и

1156064

> где величина временной задержки сигнала в элементе задержки; четвертого элементов И, вход элемента задержки соединен с первым управляющим входом одноразрядного сумматора и первыми входами пятого и девятого элементов И, выход элемента задержки подключен к входу четвертого элемента

НЕ, выход которого соединен с четвертыми входами элементов И с первого по четвертый и с третьими входами элементов И с шестого по восьмой, вторые входы пятого и девятого элементов И соединены с вторым управляющим входом одноразрядного сумматора, третьи входы пятого и девятого элементов И соединены с выходами соответственно первого и второго элементов ИЛИ, первые управляющие входы!

Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных цифровых вычислительных устройствах.

Цель изобретения — сокращение аппаратурных затрат при реализации матричного умножителя.

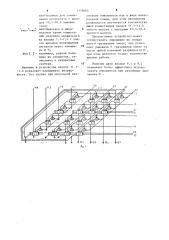

На фиг. 1 представлена функциональная схема предлагаемого устройства для умножения (для р=2); на фиг. 2 — то же, одноразрядного сумматора первой и третьей строк матрицы; на фиг. 3 — то же, одноразрядного сумматора второй и четвертой срок матрицы; на фиг. 4 — временная диаграмма работы устройства.

Устройство содержит матрицу одноразрядных сумматоров 1.1-1.h,.

2. 1-2. и, 3. 1-3.п, 4, 1-4.п, матрицу элементов И 5, входы 6.1-б.п разрядов первого операнда А, входы

7.1-7.4 разрядов второго операнда В, тактовые входы 8.1-8.2, входы 9.1 и 9.2 сброса, выходы 10.1-10.4 про25 изведения С, дополнительные входы

11.1-11.4. Сумматор 1, < (3.1) содержит элементы НЕ 12, И 13 и ИЛИ 14.

Сумматор 2. (4.1) содержит элементы

НЕ 15, И 16, ИЛИ 17 и задержки 18.

Устройство работает в конвейерном режиме,,суть которого заключается в следующем. одноразрядных сумматоров р-й и Zp-й строк матрицы соединены соответственно с первым и вторым тактовыми входами устройства, вторые управляющие входы одноразрядных сумматоров р-й и 2р-й строк матрицы соединены соответственно с первым и вторым входами сброса устройства, выходы переноса одноразрядных сумматоров 2р-й строки матрицы соединены с вторыми информационными входами соответствующих од" норазрядных сумматоров первой строки матрицы, выходы одноразрядных сумматоров с второго по и -й и 2р"й строки матрицы соединены с третьими входами одноразрядных сумматоровсоответственно с первого по(-1) -й первой строки матрицы.

В исходном состоянии на входах

8. 1, 8. 2, 9. 1 и 9. 2 установлен сигнал "1". Перед началом работы умножителя на вход 9.2 подается отрицательный импульс, который сбрасывает одноразрядные сумматоры 4. 1-4. и в нулевое состояние, при этом на четырех выходах суммы и переноса устанавливается сигнал "0".

Процесс вычисления начинается с подачи на входы 6.1, ..., 6.Й. -разрядного двоичного множнмого А и двух младших разрядов В, В п — разрядного множителя В на входы 7.1 и

7.2, Через время Т на вход 8.1 подается сигнал "О", по которому производится суммирование на сумматорах

2. 1-2. И где 1,„ „ И вЂ” максимальное время переходного процесса в логическом элементе И;

Величина 1 определяется неравенством

1156064 х1

С с выходов 10. 1 и 10. 2, а также подача разрядов Rg и В - множителя В на входы 7.1, 7.2.

1-О

Ряах и т яя ME пя1п И)

Зюххх

Оrhallrс 3 m x х вакх кт1я " я n > "Ри к яа х " Э тххх не меньших,чехх(Т„„„„ ь „„)

1 1ох Тъаъхя (Т" яяах-Т,Д, я)и Tq яя1,хх хиьо Tq „меньше(Т„;„ „„-„) яхин Р яя о я- (Р 1 "хяяс х (h+ „xä ) > где t ;„„минимальное время переходного процесса в логическом элементе И; — максимальное время; х-с О-я

1 — максимальное о1ахие я max NF время переходного процесса в логическом элементе НЕ при пе- 5 После подачи в момент времени реходе соответ- (1,ях „ + 2Pq ) на вход 8.2 сигнаственно из 1 ла "1", которыи осуществляет за1томив "0и и из 0, нание промежуточного результата .-на выходах сумматоров 4.1-4.п, а также ь,я,;я,,1.,ях — минимальное и 16 запрет отработки сумматорами 4. 1-4.п максимальное вре — поступающей информации, вычисление мя задержки сигна- продолжается в сумматорах 1.1-1. и и ла в одноразряд- 2.1-2.п. В течение времени, пока будут ном полном идти вычисления, осуществляется счисУмматоРе пРи 15 тывание разрядов С>, С произведения пРохождении сиг С с выходов умножителя 10.3 и 10.4 налов от входов и подача разрядов Вя и В множителя В до выходов (во на входы 7.3 и 7.4. всех полных одноpB3pHDHblx c MBTo

Через время ($ » „ + Pi » ), пос- навливается сигнал "0", а процесс кольку вычисления в первых двух линей- вычисления не прекращается до получеках закончилось, на вход 8.1 подается25 ния всех 2 и разрядов проиэведения С сигнал "1", который осуществляет запо- с выходов 10.1 — 10.4. При необходиминание информации, установившейся мости ускорения получения результата на выходах сумматоров 2.1-2.И, и зап- можно закончить вычисление разу же рещает отработку сумматорами 2.1-2 " после ввода разрядов В -s и Вд множисигналов, которые будут появляться ЗО теля В и суммирования их частичных на их информационных входах. произведений. Тогда на выходах

В течение времени, пока проходит суммы и переноса сумматоров 4.1вычисление ha сумматорах 1.1 — 1.и и 4.И получится двухраэрядный код

2.1 2. 0 я на сумматорах 3.1-3. и и старших разрядов произведения С, 4.1-4.п идет подготовка к вычислению который после суммирования на

35 на входы 7.3-7.4 подаются разряды В сумматоре с ускоренным переносом и В множителя В. К моменту времени даст значение старших разрядов

Ф л (1щч„и + У " x ) заканчивается пода- произведения С. ча В и Вх, вычисление продолжается Для обеспечения правильной работы на сумматорах 3.1-3.а а затем после умножителя, максимального быстродейл,40 подачи через время (1 „, „„+ „ххх + 1 i ствия, а также для обеспечения воэна вход 8. 2 сигнала "0" и на суммато- можности считывания промежуточной рах 4.1-4.)). информации и коммутации разрядов

В то же время на сумматорах 1. 1-1 ° я1 H множителя В величина P должна опреде, 2, 1-2..q осуществляется считывание двух ляться исходя из следующей системы

X младших разрядов Сх и Ся произведения неравенства

1156064

2 .2 необходимое для считывания результата с выходов 10.1-10.4 умножителя;

T ° - максимальное и миниkans Кмiq мальное время коммутации разрядов множителя В на входах 7.1-7.4 с учетом времени прохождения сигналов через элементы И 5;

Мау (1 — величина, равная большему из элементов, записанных в квадратных скобках.

Наличие в устройстве входов 11.1i1.4 позволяет наращивать разрядность. Это удобно при модульно" реанизации умножителя или в виде интегральной схемы, при этом увеличение разрядности достигается соответству. ющей коммутацией входов 11,1-11.4 одного модуля с выходами 10.1 — 10.4 другого модуля.

Предлагаемое устройство может осуществлять умножение не только двух П -разрядных чисел, оно позволяет умножать н -разрядное число на число любой конечной разрядности в при этом меняется только количество циклов работы.

15 Наличие двух входов 9.1 и 9.2 позволяет более эффективно использовать умножитель при различных значениях Ф

i156064

1156064

ЗВЮШИ З.акаэ 31 (11ll