Сумматор @ частотно-импульсных сигналов

Иллюстрации

Показать всеРеферат

СУМММОР N ЧАСТОТНО-ИМПУЛЬ CHbfX СИГНАЛОВ, содержащий первую группу элементов И, регистр режима работы, регистр коэффициента деления, выходной делитель частоты, первый элемент ИЛИ и Nблоков привязки, каждый из которых содержит элемент И, управляемый делитель частоты , регистр и RS-триггер, вход установки в 1 которого соединен с соответствующим информационным входом сумматора, прямой выход RS-триггера соединен с первым входом элемента И, выходы регистра соответственно соединены с управляющими входами управляемого делителя частоты, выход которого соединен с входом установки в О RS-трштера, информационный вход управляемого делителя частоты соединен с вьгходом элемента И, выходы элементов И нервой грутты соединены соответственно с входами разрешения записи регистров соответствующих блоков привязки, выход последнего элемента И перкой группы соединен с входом раэрешениг записи регистра коэффициента деления, выходы которого соответственно соединены с управляющими входами выходного делителя частоты, информационный вход которого соединен с выходом первого элемента ПЛИ, а выход является первым выходом сумматора. выходы элементов И блоков привязки соединены с входами первого элемента ИЛИ, выход которого является вторым выходом сумматора, вход синхронизации регистра режима работы является входом синхронизации сумматора, ч тличающийся тем, что, с целью упрощения сумматора в него введены блок памяти, формирователи коротких импульсов, первый, второй и третий триггеры, вторая группа элементов И, элемент 2И-ИЛИ, элемйгг И, второй элемент ИЛИ, блок форкшровзния импульса сброса, выход которого среди11ен с входами установки в О регистра режима работы и первого триггера,, вход установки в 1 которого соединен с выходом последнего формирова (Л теля коротких импульсов , инверсный выход первого триггера соединен с первыми входами элементов И первой группы, а прямой . его выход - с nepHbiMH входами элементов И второй грутшы, выходы которых соединены соответственно с вторыми входами элементов И блоков привязки, вторые входы элементов И первш и второй групп соединены ел соответственно с выходами формирователей О5 коротких импульсов, входы формирователей о коротких импульсов, кроме последнего, соеGb динены соответственно с выходами регистра Оо режима работы, входы всех формирователей коротких импульсов соединены с адресными входами блока памяти, входы двух последних формирователей коротких импульсов соединены с входами второго элемента ИЛИ, первый вход элемента 2И-Ш1И соединен с прямым выходом первого триггера, второй вход элемента 2И-ИЛИ соединен с выходом второго элемента ИЛИ, третий вход элемента 2И-ИЛИ соединен с инве{кным выходом первого триггера , четвертый вход элемента 2И-ИЛИ соединен с прямым выходом второго триггера, выход элемента 2И-ИЛИ соединен с информа

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1156068

Ф(59 G 06 F 762

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВЪ/

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3459924/24 — 24 (22) 29.06.82 (46) 15.05.85. Бюл. II 18 (72) А. А. Столяров и Я. T. Явный (7)) Тернопольский финансово-экономический институт (53) 681.325 (088.8) (56) Авторское свидетельство СССР Н 817709, кл. G 06 F 7/62, 1980.

Авторское свидетельство СССР N 982000, кл. G 06 F 7/62, 1981 (лрототип). (54) (57) СУММ А1 ОР N ЧАСТОТНΠ— ИМПУЛЬ

СНЫХ СИГНАЛОВ, содержащий первую группу элементов И, регистр режима работы, регистр коэффициента деления, выходной делитель частоты, первый элемент ИЛИ и Nблоков привязки, каждый из которых содержит элемент И, управляемый делитель частоты, регистр и RS-триггер, вход установки в

"1" которого соединен с соответствующим информационным входом сумматора, прямой выход RS-триггера соединен с первым входом элемента И, выходы регистра соответственно соединены с управляющими входами управляемого делителя частоты, выход которого соединен с входом установки в "0"

RS-триггера, информационный вход управляемого делителя частоты соединен с выходом элемента И, выходы элементов И первой группы соединены соответственно с входами разрешения записи регистров соответствующих блоков привязки, выход лоследнего элемента

И первой группы соединен с входом раэрешениг. записи регистра коэффициента деления, выходы которого соответственно соединены .с управляющими входами выходного делителя частоты, информационный вход когорого соединен с выходом первого элемента IISIII, а выход является первым выходом сумматора, выходы элементов И блоков привязки соединены с входами первого элемента ИЛИ, выход которого является вторым выходом сумматора, вход синхронизации регистра режима работы является входом синхронизации сумматора, отличающийся тем, что, с целью упрощения сумматора в него введены блок памяти, формирователи коротких импульсов, первый, второй и третий триггеры, вторая группа элементов И, элемент 2И-ИЛИ, элемент И,.второй элемент

ИЛИ, блок формирования импульса сброса, выход которого соединен с входами установки в "0" регистра режима работы и первого триггера;, вход установки в "Г которого соединен с выходом последнего формирователя коротких импульсов, инверсный выход первого триггера соединен с первыми входами элементов И первой группы, а прямой . его выход — с первыми входами элементов

И второй группы, выходы которых соединены соответственно с вторыми входами элементов И блоков привязки, вторые входы элементов И первой и второй групп соединены соответственно с выходами формирователей коротких импульсов, входы формирователей коротких импульсов, кроме последнего, соединены соответственно с выходами регистра режима работы, входы всех формирователей коротких импульсов соединены с адресными входами блока памяти, входы двух последних формирователей коротких импульсов соединены с входами второго элемента ИЛИ, первый вход элемента 2И-ИЛИ соединен с прямым выходом первого триггера, второй вход элемента 2И-ИЛИ соединен с выходом второго элемента ИЛИ, третий вход элемента 2И-ИЛИ соединен с инверсным выходом первого триггера, четвертый вход элемента 2И-ИЛИ соединен с прямым выходом второго триггера, выход элемента 2И-ИЛИ соединен с информа! 156068 пйонным входом регистра режима работы, выход первого разряда которого соединен с входом установки в "0" второго триггера, а выход последнего разряда соединен с первым входом элемента И, второй вход которого соединен с инверсным выходом первого триггера, а выход — с информационным входом третьего триггера, вход синхронизации которого соединен с входом синхронизации сумматора, вход установки в "0" тре- тьего триггера соединен с входом установки в "Й" регистра режима работы и с входом установки в "1" второго триггера, выход третьего триггера соединен с последним адресным входом блока памяти, выходы которого соответственно соединены с установочными; входами регистра коэффициента деления и с установочными входами регистров блоков привязки.

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств обработки и передачи частотно-импульсных сигналов.

Цель изобретения — упрощение устройства.

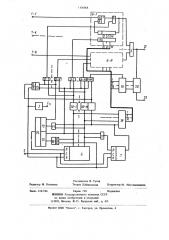

На чертеже представлена функциональная схема сумматора N частотно-импульсных сигналов, Сумматор содержит информационные входы 1 — I,...,I-N, синхронизирующий вход 2, блок 3 формирования импульса сброса, блоки

4 — 1,...,4-N привязки, первый элемент ИЛИ5 й- разрядный регистр 6 режима работы, 0-триггер 7, группу элементов И 8 — 1,... 8-N, группу элементов И 9 — 1,,9-N+1, формирователи 10 — 1,...,10-8+1, коротких импульсов, второй элемент ИЛИ ll, элемент 2И-ИЛИ 12, . 13 и 14, RS-триггер 15, RS-триггер 16, эле-. мент И 17, блок 18 памяти, регистр 19 коэффициента деления, выходной делитель 20 частоты, выходы 21 и 22 сумматора.

Сумматор работает следутощим образом.

При включении напряжения питания ситнал с блока 3 формирования импульса сброса устанавливает регистр 6 режима рабо-, ты и триггеры 7 и 15 в нулевое состояние, а триггер 16 — в единичное состояние, обеспечивающие установку сумматора в режим

"Настройка". С выхода элемента, 2И-ИЛИ 12,, 13 и 14 сигнал логической "1" (как сумма сигналов с инверсного выхода триггера 15 и с прямого выхода триггера 16) поступает на информационный вход N-разрядного регистра 6 режима работы. С приходом после-. дующего за этим первого тактового импульса на выходе первого разряда N-разрядного регистра 6 режима работы установится единичный сигнал, который сбрасывает RS-триггер

16 в нулевое состояние. С появлением этого сигнала первый формирователь 10-1 коротких импульсов формирует короткий импульс, блок 18 памяти осуществляет вывод кода режима работы первого канала. Сформированный формирователем 10 — 1 короткий импульс, пройдя через первый элемент И 9 — 1 группы осуществляет запись кода из блока

18 памяти в регистр первого блока 4 — 1 при( вязки. С приходом последующих N-l тактовых импульсов на тактовый вход й-разрядного регистра 6 режима работы аналогично происходит запйсь кодов режимов работы в регистры последующих блоков 4 — 2,... 4-й привязки.

С появлением единичного потенциала на последнем N-м триггере регистра 6 режима работы он подается через открытый единичным сигналом с инверсного входа управляющего триггера 15 элемент И 17 на информационный вход 0-триггера 7 и записывается в этот триггер с приходом гюследующего за этим (N+I)-го тактового импульса, что обеспечивает вывод из блока 18 памяти кода режима работы выходного делителя 20 частоты, который записывается в регистр 19 коэффициента деления импульсом с выхода формирователя 10-И+1, коротких импульсов через . открытый элемент И 9-N+1. Этот же импульс переключает управляющий триггер 15 в единичное состояние, заканчивая процесс настройки сумматора на требуемый режим.

Таким образом, как и в устройстве-прототипе, регистр 6 режима работы в режиме . настроики обеспечивает автоматический вывод требуемых кодов иэ блока 18 памяти и их запись в соответствующие регистры

4 — 1,...,4-N привязки и в регистр 19 коэффициента деления.

С окончанием процесса настройки сумматотора на требуемый режим работы элементы

И 9, 2И-ИЛИ 13 и 17 закрываются нулевым сигналом с инверсного выхода управляющего триггера IS, и на первые входы элементов

И 8, 2И-ИЛИ поступает единичнь|й сигнал с прямого выхода этого триггера, обеспечивающий

3 !156068 4 установку сумматора в режим "Работа". На 4 — 1,...,4-N привязки, к несовпадающим во ape вход элемента ИЛИ 1! поступает нулевой сиг- мени импульсам с частотой (1), подаваемым нал с N-rn выхода регистра 6 режима работы на синхронизующие входы блоков 4-1,...,4-N npu. и единичный. сигнал с выхода 0-триггера 7, вязки. При этом должно соблюдаться условие поэтому сумма единичных сигналов с прямого (сФ- = f (H (2) ах.

1 Ill 1 выхода управляющего триггера 15 и с выхода где 1,. — частота повторения входного сиг8Х. 1 второго элемента ИЛИ 11 через элемент нала на i-м входе.

2И-ИЛИ 12, 13 и 14 поступает на информа- На выходах блоков привязки выделяются ционный вход регистра 6 режима работы. С не совпадающие во времени пачки коротких приходом первого за этим моментом тактово- fo импульсов, число которых может изменяться го импульса происходит запись логической в пределах от 1 до к, где к . вЂ, мак.и ° °

1I1aII ma х

1 в первыи разряд регистра 6 режима. рабо- симальный коэффициент деления делителя ты, а О-триггер 7 устанавливается в нулевое частоты, входящих в состав блоков 4-1,...,4-М состояние, обеспечивая через элементы ИЛИ 11 привязки, причем пропорциональный коду, и 2И-ИЛИ 12, 13 и 14 установку логического f> записанному в регистры блоков 4-1,...,4-11!

"0". на информационном входе регистра 6 ре- привязки. Частота повторения пачек импульжима работы. С приходом последующих так- сов равна частотам входных сигналов Г

Sr i товых импульсов происходит сдвиг записанной . Полученные не совпадающие во времени в первый разряд регистра 6 режимов работы . пачки коротких импульсов просуммируются . логической "1" вплоть до ее появления на элементом ИЛИ 5, что обеспечивает получеN-триггере. регистра 6 режимов работы, что ние неравномерной последовательности имвыэывает появление этого же сигнала на его . пульсов на выходе 21, средняя частота котоинформационном входе через элементы ИЛИ 11 рых равна и 2И-ИЛИ 12, 13 и !4. В дальнейшем процесс f = k f + k f + ...+k f (3)

CP 1 1 2 2 " ЦМ . повторяется, причем с каждым тактовым им25 где Е,,...,К вЂ” коэффициенты деления соотпульсом логическая "1" возникает на одном иэ ветствующих делителей часN-триггеров регистра 6 режима работы, т.е. тоты блоков 4 — 1 4-М прион работает как N-разрядный регистр сдвига вязки; логической "1". Формирователи 10 — 1,...,10-N+1 — частоты входных сигналов. коротких импульсов выделяют короткий импульс из каждого поло нтельного перепада и Зц Равномерные импульсы на выходе 22 полу(так как регистр 6 режима работы работает, чают с частотой как кольцевой регистр сдвига логической "l") . k, f, + k f + ...+ k,„Е,„ их выходные импульсы не совпадают во времени

l а часть этих импульсов определяется выражением

Г З5, где k — коэффициент деления выходного

Itl ; =ч делителя частоты. где f. — частота повторения импульсов на выходе i-ro формирователя корот- Таким образом, предлагаемый сумматор ких импудьсов i=1 — N; выполняет. функции устройства — прототипа, f — частота повторения тактовых сигна- - так как производит автоматическую настройку

40 лов; требуемого режима работы при включении и — число разрядов регистра 6 режима напряжения питания в режиме "Настройка" и работы или суммируемых сигналов, подачу не совпадающих во времени последоИз этого следует, что в режиме "Работа" вательностей коротких импульсов на синхрорегистр 6 режима работы обеспечивает подачу 45 низируюшие входы блоков привязки в ре- на синхронизируюшие входы блоков 4-1,....4-!ч жиме "Работа"(1)т что обеспечивает выполнепривязки не совпадающих во времени корот- ние функций пропорционального и непроких импульсов с одинаковыми частотами(1), порционального суммирования частот входных т.е. выполняет функции многофазного генсра- импульсов последовательностей в соответсттора коротких импульсов, имеющегося в иэ- 5 вии с выражениями (3) и (4). При этом алговестном устроистве, выбранном в качестве ритм управления предлагаемого сумматора прототипа. упрощен, так как для его управления требуетСуммирование !ч частот осуществляется как ся лишь один сигнал — тактовый, подаваемый и в устройстве — прототипе путем привязки на вход 2. Кроме того, предлагаемое устройимпульсов каждой из входных последователь- - ство проще устройства — прототипа, так как

55 ностей, поступающих с входов 1 — 1,...,1-N сум- для его реализации требуется лишь олин рематора на информационные входы блоков гистр сдвига.

1)56068

Составитель В. Гусев

Техред Л.Мартяшова

Корректор M Максимишинец

Редактор М. Келемеш

Заказ 3147/46

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Тираж 710, Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5