Устройство для вычисления отношения периодов импульсных напряжений

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЬМИСЛЕНИЯ ОТНОШЕНИЯ ПЕРИОДОВ ИМПУЛЬСНЫХ НАПРЯЖЕНИЙ , содержащее два интегратора, два запоминающих блока, блок управления , переключатель, блок сравнения, масштабный усилитель и источник опорного напряжения, выход которого подключен к первому информационному входу переключателя, выход которого через первый интегратор подключен к информационному входу первого запоминающего блока, выход второго запоминающего блока является выходом устройства , отличающееся тем, что, с целью расширения области применения за счет вычисления отношения вида T4№.T,.( )| где 1| Т - периоды следования импульсов; С1 - коэффициент передачи масштабного усилителя; Т - длительность импульса напряжения; tn - масштабный коэффициент, в него введены гиперболический преобразователь , олок дифференцирования, элемент ИЛИ, выпрямитель, причем выход первого интегратора через выпрямитель подключен к первому входу блока сравнения, выход которого подключен к первому входу элемента ИЛИ, выход первого запоминающего блока через последовательно включенные второй интегратор и гиперболический преобразователь подключен к второму входу блока сравнения, выход источника опорного напряжения через масштабный усилитель подключен к второму информационному входу переключателя, вход запуска устройства соединен с вторьм входом элемента ИЛИ, выход (Л которого подключен к информационному . входу второго запоминающего блока, с блок управления содержит шесть триггеров , два элемента И и инвертор, причем вход запуска устройства соединен с единичным входом первого триггера , тактовый вход которого соединен с тактовыми входами пятого, шестого ел триггеров и первым информационным б входом устройства, прямой выход первоо со го триггера подключен к единичному входу второго триггера, входам уста sj новки в нуль третьего, четвертого, пятого и шестого триггеров и к управляющему входу первого интегратора, второй информационный вход устройства соединен с тактовыми входами третьего и четвертого триггеров, прямой выход третьего триггера соединен с первым входом первого элемента И и с управляющим входом четвертого триггера, прямой и инверсный выходы которого подключенысоответственно к управпяняцему входу пятого триггера и второму

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„Я0„„11

97 А

4(5!) С 06 G 7/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ Я

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (2i) 3673764/24-24 (22) 1 3. 12 . 83 (46) 15.05.85. Вюл. е 18 (72) В.А.Медников и А.H.Ïîpûíîâ (71) Куйбышевский ордена Трудового

Красного Знамени авиационный институт им.акад.С.П.Королева (53) 681.335(088.8) (56) Авторское свидетельство СССР

Р 773640, кл. G Об G 7/16, 1980.

Авторское свидетельство СССР

Н - 754436, кл. G 06 G 7/16, 1980. (54)(57) УСТРОЙСТВО ДЛЯ ВЬИИСЛЕНИЯ

ОТНОШЕНИЯ ПЕРИОДОВ ИМПУЛЬСНЫХ НАПРЯЖЕНИЙ, содержашее два интегратора, два запоминающих блока, блок управления, переключатель, блок сравнения, масштабный усилитель и источник опорного напряжения, выход которого подключен к первому информационному входу переключателя, выход которого через первый интегратор подключен к информационному входу первого sanoминающего блока, выход второго sanoминающего блока является выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет вычисления отношения вида

Т = iи Т„ т / (a 11+ Т,) j где Т вЂ” периоды следования импульсов;

С вЂ” коэффициент передачи масштабного усилителя;

1 — длительность импульса напряжения;

rn — - масштабный коэффициент, в него введены гиперболический преобразователь, блок дифференцирования, элемент ИЛИ, выпрямитель, причем выход первого интегратора через выпрямитель подключен к первому входу блока сравнения, выход которого подключен к первому входу элемента 1ШИ, выход первого запоминающего блока через последовательно включенные второй интегратор и гиперболический преобразователь подключен к второму входу блока сравнения, выход источника опорного напряжения через масштабный усилитель подключен к второму информационному входу переключателя, вход запуска устройства соединен с вторым входом элемента ИЛИ, выход которого подключен к информационному входу второго запоминающего блока, блок управления содержит шесть триггеров, два элемента И и инвертор, причем вход запуска устройства соединен с единичным входом первого триггера, тактовый вход которого соединен с тактовыми входами пятого, шестого триггеров и первым информационным входом устройства, прямой выход первого триггера подключен к единичному входу второго триггера, входам установки в нуль третьего, четвертого, пятого и шестого триггеров и к управляющему входу первого интегратора, второй информационный вход устройства соединен с тактовыми входами третьего и четвертого триггеров, прямой выход третьего триггера соединен с первым входом первого элемента И и с управляющим входом четвертого триггера, прямой и инверсный выходы которого подключены соответственно к управляющему входу пятого триггера и нторому

1156097 входу первого элемента И, выход кото- равляющему входу переключателя, и через рого подключен к первому управляющему инвертор — к управляющему входу второго входу переключателя и к управляющему интегратора, соединенному с входом входу первого запоминающего блока, блока дифференцирования, выход котопрямой выход пятого триггера подклю- рого подключен к управляющему входу чен к первому входу второго элемента второго запоминающего блока, пряИ и к управляющему входу шестого мой и инверсный выходы второго триггера, прямой и инверсный выходы триггера подключены соответственкоторого подключены соответственно но к управляющему входу третьек тактовому входу второго триггера го триггера и к управляющему и второму входу второго элемента И, входу гиперболического преобразовыход которого подключен к второму уп- вателя.

Изобретение относится к аналоговой вычислительной технике и может быть использовано в анализаторах спектров. сигналов вибраций многовальных турбоагрегатов. 5

Цель изобретения — расширение области применения за счет вычисления отношения вида где Г т — периоды следования им"1 2 пульсов;

G — - коэффициент передачи масштабного усилителя; 15

Т вЂ” длительность импульса . напряжения;

Ф вЂ” масштабный коэффициент.

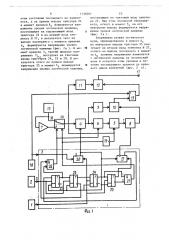

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 20 временные диаграммы, поясняющие работу устройства.

Устройство для вычисления отношения периодов импульсных напряжений содержит первый 1 и второй 2 инфор- 25 мационные входы, блок управления 3, первый 4 и второй 5 интеграторы, первый запоминающий блок 6, масштабный усилитель 7, гиперболический преобразователь 8, выпрямитель 9, 30 блок сравнения 10, блок дифференцирования 11, второй запоминающий блок (триггер) 12, элемент ИЛИ 13, переключатель 14, источник опорного напряжения 15, первый 16 информационный вход переключателя 14, выход

17 устройства, вход запуска 18 устройства.

В одном из вариантов исполнения блок управления 3 содержит, например,. инвертор 19, триггеры 20-25, элементы И 26 и 27.

Устройство работает следующим образом.

В исходном состоянии (до поступления на информационные входы 1 и 2 устройства сигналов, периоды следования которых подлежат преобразованию) на входе запуска устройства 18 присутствует напряжение нулевого уровня.

При этом на выходах триггера 20 н элементов И 26 и 27 присутствуют напряжения нулевого уровня (уровня логического нуля), фиг..2ъ, b,,а, а на инверсном выходе триггера 21 и на выходе логического инвертора 19 установлено напряжение уровня логической единицы (фиг. 2 л, ). В результате этого цепь сброса интегратора 4 разомкнута, а цепь сброса интегратора 5 замкнута, переключатель 14 находится в нейтральном состоянии, при котором его выход не скоммутирован ни с одним из его информационных входов, а запоминающий блок 6 находится в режиме хранения напряжения от предыдущего цикла преобразования.

Запуск устройства в работу производится сигналом "Пуск" — коротким импульсом, поступающим в момент времени C с входа запуска устройстН ва 18 на первый вход элемента ИЛИ 13 и на единичный вход триггера 20.

При этом короткий импульс напряжения уровня логической единицы, 1156097 сформированный на выходе элемента

ИЛИ 13 в момент- „(фиг. 2р ), поступает на информационный вход триггера 12 и дублирует (подтверждает) состояние его сброса, которому отвечает нулевой уровень напряжения на выходе триггера 12 и на выходе 17 устройства.

С момента н на прямом выходе триггера 20 формируется напряжение 10 уровня логической единицы (фиг. 2С ), поступающее на управляющий вход интегратора 4, а на инверсном выходе триггера 21 с момента t величина напряжения изменяется с уровня ло- 15 гической единицы на уровень логического нуля (фиг. 2я ) и поступает на управляющий вход гиперболического преобразователя 8.

Разрядная цепь интегратора 4 20 в момент С замыкается, в результате чего йа выходе интегратора 4 устанавливается напряжение нулевого уровня (фиг. 2 ), а на гиперболический преобразователь 8 переходит 25 в режим подготовки, при котором производится отслеживание на выходе гиперболического преобразователя 8 .выходного напряжения интегратора 5.

В момент времени 1 первый импульсЗО

7. поступает с первого информацион1 ного входа 1 на тактовые входы триггеров 20, 24 и 25, в результате чего в момент 1„ напряжение на прямом выходе триггера 20 устанавливается нулевым уровнем (фиг. 2 г ).

На тактовые входы триггеров 22 и 23 в момент времени 1 поступает со второго информационного входа 2 щ первый. импульс,, в результате . чего с момента t на выходе элемента

2.

И 26 формируется напряжение уровня логической единицы, которое поступает на первый управляющий вход переключателя 14 и на первый управляющий вход запоминающего блока 6.

При этом в момент t переключатель

14 переводится в первое рабочее состояние (при котором его выход 5О смонтирован с его первым информационным входом), подключая выход источника опорного напряжения 15 к первому входу интегратора 4, а запоминающий блок 6 с момента 1 переводится в 55 режим слежения, при котором выходное напряжение блока 6 повторяет напряжение на его первом входе до момента окончания управляющего импульса на

его втором входе.

С момента .2 напряжение на выходе интегратора 4 изменяется согласно

< +С t on

1

-t+ о

Ue= 1 Y11 (3) Второй импульс . приходит с второго информационного входа устройства на тактовые входы триггеров

22 и 23 в момент времени 1з = 1 + Т, где Т вЂ” период следования импульсов с второго информационного входа устройства 2, в результате чего в момент 1 напряжение на выходе элемента И 26 устанавливается нулевым уровнем. При этом переключатель 14 переводится в нейтральное состояние. а запоминающий блок 6 с момента 1 находится в режиме хранения, при котором его выходное напряжение остается неизменным во времени.

Напряжение V на выходе интегратора 4 в момент 1 равно величине интеграла опорного напряжения-sa период

2 г.

С -С

Y =- — u

1 к 1,1 оп оп 1 (4 о

1 где К,= — — коэффициент пропорциональности.

С момента времени т, напряжение на выходе интегратора ч сохраняется неизменным (фиг ° 2 з):

„t„, =V%„ (5)

Также неизменным сохраняется с момента 1 и выходное напряжение запоминающего блока 6 (фиг. 2 и ), определяемое величиной ц у (6} ь >

В момент т. второй импульс 1, поступает с первого информационного где Ч вЂ” постоянная интегрирования ,интегратора 4 °

"1„П- величина напряжения источника опорного напряжения 15;

t — время,. отсчитанное от момента 1 и поступает на первый (аналоговый) вход запоминающего блока 6 и на вход выпрямителя 9, выходное напряжение которого изменяется соответственно выражению

1156097

10 этом состояние последнего не изменяется, а на прямом выходе триггера 24 в момент времени формируется напряжение уровня логической единицы, поступающее на управляющий вход триггера 25 и на первый вход элемента И 27, в результате чего на выходе последнего с момента времени

Ь формируется напряжение уровня логической единицы (фиг. 2а ). В момент времени третий импульс напряжения Т1, поступает на тактовые входы триггеров 24, 25 и 20 ° В результате этого на прямом выходе триггера 25 в момент 1 формируется напряжение уровня логической единицы поступающее на тактовый вход триггера 21. При этом последний сбрасывается, отчего в момент на его инверсном выходе формируется напряжение уровня логической единицы (фиг. 2л ).

Напряжение уровня логического нуля, сформированное в момент 1 на инверсном выходе триггера 25 поступает на второй вход элемента И 27, отчего на выходе последнего в моменте 6 уровень напряжения изменяется с логической единицы на логический нуль и остается этим уровнем в течение последующего времени до нулевого цикла измерений (фиг, 2 е).

115á097

7i i1

Ую

0(18 ПЦек

0(6) алых.

U(u) алых

У(У)Вых. 4 с

Фи .2 Н 1 2 t3 elk

0(3)алых.д

У(з) Рыб.1

1/(з)Й/х, 2

U(6)8blX

Ц(5)Вых.

V(21) 8ь7х.

0(8) ЮБ/У

Ц(®алых 11)Вью

U(10) дь(х

У(1З) 8ьи

lJ(12)8bix

ВНИИПИ Заказ 3148/47 Тираж 710 Подписное

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4

SU 1156098A

Batch : N0034912

Date : 03/01/2001

Number of pages : 4

Previous document : SU 1156097A

Next document : SU 1156099A