Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

I. БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ; УСТРОЙСТВО, содержащее накопитель , адресный блок и блок управления, причем первый вход и выход накопителя являются информационными входом и выходом устройства, входы адресного блока соединены с вторым и третьим входами накопителя, а первый выход - с соответствующими входами блока управления, выходы которого и входы адресного блока являются соответственно управляющими выходами и входами устройства, отличающееся тем, что, с целью повыщения быстродействия устройства, оно содержит коммутатор , первый и второй входы которого соединены соответственно с вторым и третьим выходами адресного блока, а первый и второй выходы - с вторым и третьим входами блока управления, причем четвертый и пятый выходы адресного блока соединены с соответствующими входами накопителя . 2.Устройство по п. 1, отличающееся тем, что коммутатор содержит элемент И-НЕ, первый и второй элементы И, выходы кото . рых являются соответствующими выходами, коммутатора, первые входы соединены с выходом элемента И-НЕ, входы которого и вторые входы элементов И соединены соответственно с первым и вторым входами коммутатора. 3.Устройство по п. 1, отличающееся тем, что адресный блок содержит дещифратор , счетчики, элементы задержки и элемент И, примем входы первого и второго V элементов задержки являются входами блока , а выходы соединены с входами соответствующих счетчиков и являются вторым и третьим выходами блока, выходы первого и второго счетчиков соединены с входами соответствующих дешифраторов и входами элемента И, выход которого является первым выходом блока, а выходы первого и второго дешифратора - соответственно четвертым и пятым выходами блока. сд Ot)

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ госудАРственный комитет сссР

Ilo делАм изоБРетений и ОткРытий (21) 3711942/24-24 (22) 14.05.84 (46) 15.05.85. Бюл. № 18 (72) В. П. Лачугин, А. Ю. Веревкин и Л. В. Гуляева (53) 681.327.6 (088.8) (56) Патент Великобритании № 2009983, кл. G4С,,опублик. !979.

Авторское свидетельство СССР № 964731, кл. G 11 С 11/00, 1982. (54) (57) 1. БУФЕРНОЕ ЗАПОМИНАЮIII EE УСТРОЛСТВО, содержащее накопитель, адресный блок и блок управления, причем первый вход и выход накопителя являются информационными входом и выходом устройства, входы адресного блока соединены с вторым и третьим входами накопителя, а первый выход — с соответствующими входами блока управления, выходы которого и входы адресного блока являются соответственно управляющими выходами и входами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит коммутатор, первый и второй входы которого соединены соответственно с вторым и третьим выходами адресного блока, а первый

„S0„„1156140 A

4uO G 11 С 19/00 и второй выходы — с вторым и третьим входами блока управления, причем четвертый и пятый выходы адресного блока соединены с соответствующими входами накопителя.

2. Устройство по п. 1, отличающееся тем, что коммутатор содержит элемент И-НЕ, первый и второй элементы И, выходы кото. рых являются соответствующими выходами. коммутатора, первые входы соединены с выходом элемента И-НЕ, входы которого и вторые входы элементов И соединены соответственно с первым и вторым входами коммутатора.

3. Устройство по п. 1, отличающееся тем, что адресный блок содержит дешифратор, счетчики, элементы задержки и элемент И, причем входы первого и второго элементов задержки являются входами блока, а выходы соединены с входами соответствующих счетчиков и являются вторым и третьим выходами блока, выходы первого и второго счетчиков соединены с входами соответствующих дешифраторов и входами элемента И, выход которого является первым выходом блока, а выходы первого и второго дешифратора — соответственно четвертым и пятым выходами блока.

1156140

Изобретение относится к запоминающим устройствам.

Цель изобретения — повышение быстродействия устройства.

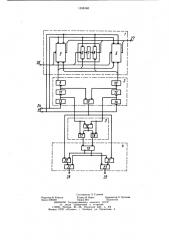

На чертеже приведена структурная схема устройства.

Устройство содержит накопитель 1, адресный блок 2, коммутатор 3 и блок управления 4.

Каждая из ячеек 5 накопителя 1 содержит клапаны записи 6, регистр 7 и клапаны чтения 8.

Адресный блок содержит дешифраторы адресов записи 9 и чтения 10, счетчики адресов записи 11 и чтения 12, элементы задержки 13 и 14, а также элемент И 15.

Коммутатор содержит элемент И-HE 16 и элементы И 17 и 18.

Блок управления содержит триггеры 19, 22, 23 и элементы И 20 и 21.

Предложенное устройство работает следующим образом.

В исходном состоянии все регистры накопителя 1 свободны. Триггер 19 находится в единичном состоянии и сигнал с его прямого выхода устанавливает триггер 22 в единичное состояние, на выходе 28 устройства появляется единичный сигнал, что соответствует разрешению записи.

Содержимое счетчиков 11 и 12 равно нулю. Элемент И 15 вырабатывает сигнал совпадения, который через элемент И 21 устанавливает триггер 23 в нулевое состояние, при этом на выходе 29 устройства появляется нулевой сигнал, что соответствует запросу чтения. Таким образом, в исходном состоянии разрешена только запись данных в накопитель 1.

При подаче управляющего сигнала записи на вход 24 устройства он поступает в накопитель 1 на один из входов всех клапанов записи 6, данные с информационных входов 26 устройства также подаются в накопитель 1 на другие входы всех клапанов записи 6.

Так как содержимое счетчика 11 адреса записи равно нулю, то сигнал с нулевого выхода дешифратора 9 откроет клапаны записи 6 нулевой ячейки памяти и будет произведена запись слова данных в регистр 7 этой ячейки.

Задержанный управляющий сигнал записи с выхода элемента задержки 13 увеличивает содержимое счетчика 11 на единицу, т. е, формирует следующий адрес . . я записи данных. Этим же задержанным ,. ",гпалом через элемент И 17 коммутатора 3 . с анавливает в нулевое состояние тригр 9, сигнал с инверсного выхода которо,ттановнт в единичное состояние триг: :, снимая сигнал запрета чтения.

Таким образом, чтение данных из накопителя 1 возможно только в том случае, если произошла запись в него хотя бы одного слова.

Работа устройства при чтении данных аналогична рассмотренной выше. При этом

m-й адрес чтения формируется в счетчике

12 и через дешифратор 10 передается в накопитель 1, где происходит открытие клапанов чтения - 8 m-ой ячейки памяти 5.

1О Данные снимаются с выхода 27 устройства.

При чтении данных триггер 19 через элемент И 18 коммутатора 3 устанавливается в единичное состояние и снимает сигнал запрета записи, если он установлен.

При одновременном поступлении сигналов записи и чтения на управляющие входы 24 и 25 устройства соответственно производится одновременно запись данных по

1му адресу и чтение данных по m-му адресу. Задержанные сигналы с элемен о тов задержки 13 и 14 формируют следующие вдреса в счетчиках 11 и 12, а также одновременно поступают на входы элемента И вЂ” НЕ 16 коммутатора, сигнал с выхода которого закроет элементы И 17 и 18. В результате этого никаких изменений в состоянии блока управления 4 не происходит и на выходах 28 и 29 устройства остаются сигналы разрешения и записи и чтения.

В устройстве вырабатываются сигналы запрета записи данных в полностью заня30 тый накопитель 1, а также запрета чтения данных из пустого накопителя 1. 8 этих случаях содержимое счетчиков 11 и 12 равно между собой, что приводит к срабатыванию элемента И 15, сигнал с выхода которого через элементы И 20 или 21 приЗ5 водит к установке в нулевое состояние триггеров 22 или 23, что соответствует сигналам запрета записи или чтения.

Например, происходит запись данных в накопитель 1 до полного его заполнения, 4О причем чтение данных не производится. В этом случае после записи последнего слова данных в накопитель 1 сигнал, задержанный элементом задержки 13, вызывает переполнение (обнуление) счетчика 11, а так как содержимое счетчика 12 также равно

45 нулю, то срабатывает элемент И 15, сигнал с выхода которого через элемент И 20 устанавливает в нулевое состояние триггер 22, тем самым вырабатывая сигнал запрета записи данных в накопитель.

Аналогичным образом происходит выработка сигнала запрета чтения данных из пустого накопителя.

Таким образом, в устройстве достигается повышение быстродействия за счет одновременного выполнения операций запи си по t-му адресу и чтения по m-му адресу, что позволяет увеличить быстродействие вычислительных машин и систем.

28

Составитель Л. Гуляева

Реда кто р В. Ко вту н Техред И. Верес Корректор О. Луговая

Заказ 3!83 49 Тираж 584 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и оч крытий

I 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4