Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопительный элемент на конденсаторе, первый усилитель, вход которого является входом устройства, выход первого усилителя соединен с первым входом ключа, второй вход которого соединен с первым входом блока управления и с шиной управления, первый. П второй и третий компараторы, выходы которых соединены соответственно с вторым, третьим и четвертым входами блока управления , выход блока управления соединен с первым входом коммутатора, второй, третий и четвертый входы которого соединены соответственно с первой, второй и третьей шинами опорных напряжений, первые входы компараторов соединены с входами первого усилителя, вторые входы компараторов соединены соответственно с шинами опорных напряжений, второй усилитель, выход которого является выходом устройства , отличающееся тем, что, с целью упрощения устройства, в нем выход ключа соединен с входом второго усилителя и с первой § обкладкой конденсатора, вторая обкладка которого соединена с выходом коммутатора. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„1156142 д

4(5ц б 11 С 27/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ од

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3708396/24-24 (22) 04.01.84 (46) 15.05. 85. Бюл. № 18 (72) В. К. Чепалов, Н. P. Карлов, А. Д. Паламарчук и Ю. Е. Болдицкий (53) 681.327.66 (088.8) (56) Авторское свидетельство СССР № 1019496, кл. G 1! С 27/00, 1981.

Авторское свидетельство СССР № 1010658, кл. G 11 С 27/00, 1981. (54) (57) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОИСТВО, содержащее накопительный элемент на конденсаторе, первый усилитель, вход которого является входом устройства, выход первого усилителя соединен с первым входом ключа, второй вход которого соединен с первым входом блока управления и с шиной управления, первый, второй и третий компараторы, выходы которых соединены соответственно с вторым, третьим и четвертым входами блока управления, выход блока управления соединен с первым входом коммутатора, второй, третий и четвертый входы которого соединены соответственно с первой, второй и третьей шинами опорных напряжений, первые входы компараторов соединены с входами первого усилителя, вторые входы компараторов соединены соответственно с шинами опорных напряжений, второй усилитель, выход которого является выходом устройства, отличающееся тем, что, с целью упрощения устройства, в нем выход ключа соединен с входом второго усилителя и с первой обкладкой конденсатора, вторая обкладка Е которого соединена с выходом коммутатора.

56142

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано, например, в контрольно-измерительной аппаратуре для временной дискретизации аналоговых сигналов.

Цель изобретения — упрощение устройства.

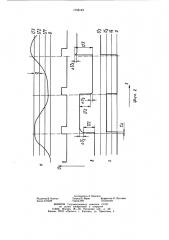

На фиг. 1 изображена функциональная схема предложенного устройства; на фиг. 2— временные диаграммы, поясняющие его работу.

Предложенное устройство (фиг. 1) содержит усилители 1 и 2, ключ 3, накопительный элемент на конденсаторе 4, шину 5 управления, компараторы 6, 7 и 8, блок 9 управления, коммутатор 10, шины 11, 12 и 13 опорных напряжений.

Значения опорных напряжений Uz ...U> (фиг. 2а) выбираются лежащими внутри динамического диапазона входных сигналов аналогового запоминающего устройства. Разность между двумя соседними опорными напряжениями равна q. Величина q выбирается из условия с! = — где Umax—

V пах динамический диапазон запоминаемых сигналов; К вЂ” требуемый показатель увеличения быстродействия, К = N+ 1 (N — число опорных напряжений).

Предложенное устройство работает следующим образом.

В момент поступления импульса запоминания на шину 5 управления (фиг. 2б), определяющего момент запоминания уровня входного сигнала, замыкается ключ 3 и разрешается переключение выходных сигналов блока 9 управления. Напряжение входного сигнала на фиг. 2а сравнивается по амплитуде с опорными напряжениями с помощью компараторов 6, 7 и 8, вследствие чего в каждый момент времени на входах блока 9 управления присутствует комбинация сигналов, определяемая амплитудой входного сигнала.

Каждой комбинации сигналов на входе блока 9 управления соответствует выходная совокупность логических сигналов, которые при наличии импульса запоминания

1О

40 (фиг. 2б) переключают коммутатор 10 таким образом, что к обкладке накопительного конденсатора 4 подключается опорное напряжение, которое соответствует компаратору, сработавшему последним, т. е. ближайшее к напряжению сигнала и меньшее его по величине (фиг. 2г). Включение напряжения (фиг. 2г) осуществляется с задержкой з, определяемой задержками блока 9 управления и коммутатора 10. Таким образом, к одной обкладке конденсатора 4 прикладывается через замкнутый ключ 3 напряжение входного сигнала (фиг. 2а), а к другой — опорное напряжение (фиг. 2г).

В результате происходит заряд накопительной емкости 4 до величины разности опорного напряжения и входного сигнала (Uz, < Uy на фиг. 2в) . Величина на этой разности не может превышать величины < (фиг.2 а).

По окончании импульса запоминания (фиг.2 б) устройство переходит в режим хранения, ключ 3 размыкается, запрещается переключение коммутатора 10 выходными сигналами блока 9 управления (остается включенным выбранное опорное напряжение) и на входе усилителя 2 фиксируется напряжение, равное сумме соответствующего опорного напряжения на одной из шин 11, 12, 13 и напряжения на конденсаторе 4 (фиг. 2в). Это суммарное напряжение, равное напряжению входного сигнала в момент действия импульса выборки (фиг. 2б), передается на выход усилителем 2.

Таким образом, в предложенном устройстве, как и в прототипе, который принят за базовый объект, в режиме запоминания конденсатор 4 заряжается до величины, не превышающей величины разности между соседними опорными напряжениями о, но при этом повышается надежность, упрощается схема, увеличивается технологичность и повышается точность, так как для коммутации сигнала используется меньшее число ключей и уменьшается погрешность, вызванная прохождением сигналов управляющих ключами, на конденсатор 4.

1156142

Составитель А. Воронин

Редактор В. Ковтун Техред И. Верес Корректор О. Луговая

Заказ 3183 49 Тираж 584 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП <Патент», г. Ужгород, ул. Проектная, 4