Оперативное запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ , содержаще накопитель, первый и второй регистры числа, блок управления, входы которого соединены с одними из выходов регистра адреса, управляющие выходы подключены к управляющим входам регистра адреса и регистров числа, а одни из управляющих входов являются управляющими входами устройства, причем входы первого регистра числа и выходы второго регистра числа являются соответственно информационными входами и выходами устройства, отличающееся тем, что, с целью повыщения надежности устройства, в него введены формирователь управляющих сигналов, формирователь тестовых сигналов, блок сравнения , третий регистр числа и коммутаторы, причем выходы первого коммутатора подключены к входам накопителя, входы первой группы блока сравнения соединены с одними из выходов регистра адреса, другие выходы которого подключены к входам первой группы первого коммутатора и входам второй группы блока сравнения, входы третьей группы и выходы которого соединены с одними из выходов и с входами первой группы формирователя тестовых сигналов, другие выходы и входы второй группы которого подключены к одним из входов и к выходам первой группы формирователя управляющих сигналов, другие входы которого соединены с одними из выходов блока управления, другие выходы которого подключены к входам третьей группы формирователя тестовых сигналов и входам четвертой группы блока сравнения, входы пятой группы которого соединены с выходами второй группы формирователя управляющих сигналов, управляющий в .ход и одни из управляющих выходов которого подключены соответственно к первому управляющему выходу блока сравнения и к управляющим входам накопиI теля, выходы которого соединены с одними из входов второго и третьего коммутаторов, (Л входы второй группы первого коммутатора подключены к выходам первого регистра числа и другим входам второго коммутатора, управляющие входы которого соединены с выходами третьей группы формирователя управляющих сигналов, выходы четвертой и пятой групп которого подключены соответственно к входам третьей группы первого коммутатора и к управляющим входам треСП тьего коммутатора, другие входы которого и входы четвертой группы первого коммута05 тора соединены с выходами третьего регистра числа, управляющий вход которого под4 СЛ ключен к другому управляющему выходу формирователя управляющих сигналов, а входы соединены с вы.ходами второго коммутатора и входами щестой группы блока сравнения, другой управляющий выход которого подключен к другому управляющему входу блока управления, выходы третьего коммутатора соединены с входами второго регистра числа.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Ъ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

llO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3696346/24-24 (22) 30.01.84 (46) 15.05.85. Бюл. № 18 (72) Ю. В. Сычев и Г. А. Бородин (71) Московский ордена Ленина и ордена

Октябрьской Революции энергетический институт (53) 681.327 (088.8) (56) 1. «Электроника», 1979, № 24, с. 75-76.

2. Полупроводниковые запоминающие устройства и их применение. Под ред.

А. Ю. Гордонова. М., «Радио и связь», 1981, с. 91, рис. 3.1 (прототип). (54) (57) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТР0ЛЕМ, содержащее накопитель, первый и второй регистры числа, блок управления, входы которого соединены с одними из выходов регистра адреса, управляющие выходы подключены к управляющим входам регистра адреса и регистров числа, а одни из управляющих входов являются управляющими входами устройства, причем входы первого регистра числа и выходы второго регистра числа являются соответственно информационными входами и выходами устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены формирователь управляющих сигналов, формирователь тестовых сигналов, блок сравнения, третий регистр числа и коммутаторы, причем выходы первого коммутатора подключены к входам накопителя, входы первой группы блока сравнения соединены с одними из выходов регистра адреса, другие выходы которого подключены к входам первой группы первого коммутатора и входам второй группы блока сравнения, входы третьей группы и выходы которого соединены с одними из выходов и с входами первой груп„,SUÄÄ 1156145 А

4(5D G 1! С 2900 пы формирователя тестовых сигналов, другие выходы и входы второй группы которого подключены к одним из входов и к выходам первой группы формирователя управляющих сигналов, другие входы которого соединены с одними из выходов блока управления, другие выходы которого подключены к входам третьей группы формирователя тестовых сигналов и входам четвертой группы блока сравнения, входы пятой группы которого соединены с выходами второй группы формирователя управляющих сигналов, управляющий вход и одни из управляющих выходов которого подключены соответственно к первому управляющему выходу блока сравнения и к управляющим входам накопителя, выходы которого соединены с одними из входов второго и третьего коммутаторов, входы второй группы первого коммутатора подключены к выходам первого регистра числа и другим входам второго коммутатора, управляющие входы которого соединены с выходами третьей группы формирователя управляющих сигналов, выходы четвертой и пятой групп которого подключены соответственно к входам третьей группы первого коммутатора и к управляющим входам третьего коммутатора, другие входы которого и входы четвертой группы первого коммутатора соединены с выходами третьего регистра числа, управляющий вход которого подключен к другому управляющему выходу формирователя управляющих сигналов, а входы соединены с выходами второго коммутатора и входами шестой группы блока сравнения, другой управляющий выход которого подключен к другому управляющему входу блока управления, выходы третьего коммутатора соединены с входами второго регистра числа.

1156145

Изобретение относится к вычислительной технике и может быть использовано для проведения функционального контроля оперативных запоминающих устройств в процессе их работы.

Известно оперативное запоминающее устройство с самоконтролем, в котором используется метод контрольного суммирования для контроля работы устройства (1J

Недостатками этого устройства являются низкие быстродействие и достоверность контроля.

Наиболее близким к предлагаемому является оперативное запоминающее усТройство, содержащее накопитель, регистр числа, выходы которого являются выходами устройства, дешифратор адреса, входы которого соединены с выходами регистра адреса, выходы дешифратора адреса и регистра адреса подключены к адресным входам накопителя через схемы согласования, другие схемы согласования, выходы которых подключены к информационным и к управляющим входам накопителя (2).

Недостатком прототипа является низкая надежность, так как в нем отсутствуют встроенные средства функционального контроля в процессе работы устройства.

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что в оперативное запоминающее устройство с самоконтролем, содержащее накопитель, первый и второй регистры числа, блок управления, входы которого соединены с одними из выходов регистра адреса, управляющие выходы подключены к управляющим входам регистра адреса и регистров числа, а одни из управляющих входов являются управляющими входами устройства, причем входы первого регистра числа и выходы второго регистра числа являются соответственно информационными входами и выходами устройства, введены формирователь управляющих сигналов, формирователь тестовых сигналов, блок сравнения, третий регистр числа и коммутаторы, причем выходы первого коммутатора подключены к входам накопителя, входы первой группы блока сравнения соединены с одними из выходов регистра адреса, другие выходы которого подключены к входам первой группы первого коммутатора и входам второй группы блока сравнения, входы третьей группы и выходы которого соединены с одними из выходов и с входами первой группы формирователя тестовых сигналов, другие выходы и входы второй группы которого подключены к одним из входов и к выходам первой группы формирователя управляющих сигналов, другие входы которого соединены с одними из выходов блока управления, другие выходы которого подключены к входам третьей груп5

10 !

55 пы формирователя тестовых сигналов и входам четвертой группы блока сравнения, входы пятой группы которого соединены с выходами второй группы формирователя управляющих сигналов, управляющий вход и одни из управляющих выходов которого подключены соответственно к первому управляющему выходу блока сравнения и к управляющим входам накопителя, выходы которого соединены с одними из входов второго и третьего коммутаторов, входы второй группы первого коммутатора подключены к выходам первого регистра числа и другим входам второго коммутатора, управляющие входы которого соединены с выходами третьей группы формирователя управляющих сигналов, выходы четвертой и пятой групп которого подключены соответственно к входам третьей группы первого коммутатора и к управляющим входам третьего коммутатора, другие входы которого и входы четвертой группы первого коммутатора соединены с выходами третьего регистра числа, управляющий вход которого подключен к другому управляющему выходу формирователя управляющих сигналов, а входы соединены с выходами второго коммутатора и входами шестой группы блока сравнения, другой управляющий выход которого подключен к другому управляющему входу блока управления, выходы третьего коммутатора соединены с входами второго регистра числа.

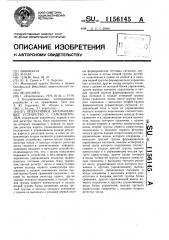

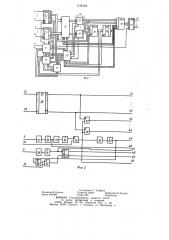

На фиг. 1 представлена функциональная схема предложенного устройства; на фиг. 2функциональная схема наиболее предпочтительного варианта выполнения блока управления.

Устройство содержит входы 1 — 6, регистр

7 адреса, первый регистр 8 числа, блок 9 управления, блок 10 сравнения, формирователь 11 тестовых сигналов, первый коммутатор 12, формирователь 13 управляющих сигналов, накопитель 14, разделенный на части 15, второй коммутатор 16, второй регистр

17 числа, третий коммутатор 18 и третий регистр 19 числа.

Устройство содержит выходы 20 и 21.

Блок 9 управления (фиг. 2} имеет входы 2225 и содержит дешифратор 26, элементы задержки 27 и 28, элемент ИЛИ-НЕ 29, формирователи 30, 31 одиночного импульса, элемент И 32, элемент задержки 33, формирователь 34 одиночного импульса, триггер

35, элементы И 36-38, элемент задержки 39, формирователь 40 одиночного импульса.

Блок 9управления содержит выходы 41—

50.

Г1редложенное устройство работает следующим образом.

Необходимым условием правильной работы устройства является требование разбиения объема накопителя !4 на некоторое количество частей 15. В то время, как в од1156145 ной из частей 15 осуществляется обращение, в другой части 15 происходит контроль функционирования. Проверка прекращается на моменты времени, когда происходит обращение.к проверяемой части 15. После контроля одной части 15 переходят к контролю другой части 15 и так до тех пор, пока не будет проверен весь накопитель 14.

Дешифрацию частей 15 накопителя 14 целесообразно выполнять младшими разрядами адреса.

Перед началом работы устройства сигналом «Сброс» отрицательной полярности все триггеры и счетчики устройства устанавливаются в исходное состояние.

Счетчики в формирователе 13 определяют количество проверяемых ячеек памяти в каждой части 15 и количество проверяемых частей 15 накопителя 14. Первоначально на счетчиках формирователя 13 установлен адрес первой ячейки памяти первой части 15 накопителя 14.

По первому сигналу обращения на входе 5 (фиг. 1 и 3) к накопителю 14 происходит перезапись информации из этой ячейки памяти накопителя 14 в регистр 19. Коммутатор 16 осуществляет подключение к информационным входам регистра 19 или выходов части 15 накопителя 14, или выходов регистра 8. Управляющие сигналы для коммутатора 16 вырабатываются в формирователе 13.

По второму сигналу обращения осуществляется запись «О» в проверяемую ячейку накопителя 14.

По третьему импульсу обращения происходит сравнение правильности хранения этой ячейкой «О» с блока 10. Если происходит несовпадение записанной и считываемой из ячейки информации, то триггер в блоке 10 устанавливается в единичное состояние, тем самым фиксируя наличие слоя или отказа. Счетчик в формирователе 11 определяет количество тактов проверки одной ячейки памяти. Всего необходимо шесть тактов для проверки одной ячейки (считывание и запоминание на регистре 19 содержимого

Зо

40 яейки, проверка хранения ячейкой «О», проверка хранения ячейкой «1», запись первоначального содержимого в ячейку) . Блок

10 вырабатывает сигналы, необходимые для контроля накопителя 14 «Вход», «Записьсчитывание». Примем, что запись осуществляется сигналом отрицательной полярности, а считывание — сигналом положительной полярности. Каждой части 15 соответствует триггер в формирователе 13, который устанавливается в единичное состояние, когда происходит обращение к определенной части 15 накопителя 14. При совпадении адреса ячейки, выбранного формирователем 13, с адресом на входах накопителя 14, блок 10 вырабатывает сигнал, который запоминается на триггере в блоке 10. Это говорит о том, что необходимо производить обращение к регистру 17.

Коммутатор 18 определяет, какую информацию подключить к информационным входам регистра 17. Управляющие сигналы для коммутатора 19 вырабатываются формирователем 13.

Коммутатор 12 определяет, какие адресные и информационные входы подключить к определенной части 15.

В зависимости от состояния триггеров в формирователе 13 и такта работы формирователя 11 по проверке какой-либо ячейки накопителя 14 осуществляется коммутация или адреса, поступающего с регистра, или адреса, вырабатываемого формирователем

13. На коммутатор 12 поступает число или с формирователя 11, или число с регистра

19, или число с регистра 8.

Концом проверки функционирования устройства является наличие импульса переполнения счетчика в формирователе 13.

Таким образом, в предложенном устройстве повышается надежность работы и уменьшается время, затрачиваемое на его профилактический контроль.

Технико-экономическое преимущество предложенного устройства заключается в более высокой надежности по сравнению с прототипом.

ФО2 г

47

48

4У

Составитель Т. Зайцева

Реда кто р В. Ковтун Техред И. Верес Корректор В. Бутяга

Заказ 3) 84/50 Тираж 584 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5 филиал ППП «Патент», г. Ужгород, ул. Проектная, 4