Способ демодуляции двухфазных трехуровневых сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике передачи цифровых данных через проводные линии связи с транформаторной развязкой и может использоваться непосредственно для демодуляции сигналов , модулированных кодом с расщепленной фазой. изобретения является повышение помехоустойчивости . Устройство, реализующее способ демодуляции биполярного фазоманипулированного сигнала, содержит сумматор 1 и детектор 2 переходов, входы которых соединены с входной шиной 3, интегрирующий фильтр 4, соединенный с выходом сумматора 1, компараторы положительного 5 и отрицательного 6 уровня, соединенные с выходом интегрирующего фильтра 4, элементы И 7 и 8, первые входы которых соединены соответственно с выходами компараторов положительного 5 и отрицательного 6 уровня, а вторые - с соответствующими выходами детектора 2 переходов , триггеры 9,10, входы установки которых соединены с выходами соответствующих элементов И 7 и 8, а выходы - с выходными информационными шинами единиц 11 и нулей 12, I дифференциальный усилитель 13, выход которого соединен с вторым входом (Л сумматора 1, а входы - с соответствующими выходными информационными шинами и входами элемента ИЛИ 14, выход которого через элемент 15 задержки соединен со входами обнуления триггеров 9 и 10. 1 з.п. ф-лы, 2 ил. ел 4 05

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

7 -

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ к Я

Ф к

1 l

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3503413/24-21 (22) 15. 10.82 (46) 30.03.88. Бюл. Ф 12 (72) Ю.Г. Байков (53),621.376,4 (088.8) (56) Патент США У 3820031, кл. 340-166, 1974.

Авторское свидетельство СССР

В 951690, кл. Н 03 К 9/04, 1980. (54) СПОСОБ ДЕМОДУЛЯЦИИ БИПОЛЯРНОГО

ФАЗОМАНИПУЛИРОВАННОГО СИГНАЛА (57) Изобретение относится к технике передачи цифровых данных через проводные линии связи с транформаторной развязкой и может использоваться непосредственно для демодуляции сиг- налов, модулированных кодом с расщепленной фазой. Целью изобретения является повышение помехоустойчивости. Устройство, реализующее способ демодуляции биполярного фазоманипулированного сигналя, содержит сумматор 1 и детектор 2 переходов, входы

Взамен ранее изданного

115 246 (51) 4 Н 03 И 5/00 Н 04 L 17/00 которых соединены с входной шиной 3, интегрирующий фильтр 4, соединенный с выходом сумматора 1, компараторы положительного 5 и отрицательного 6 уровня, соединенные с выходом интегрирующего фильтра 4, элементы И 7 и 8, первые входы которых соединены соответственно с выходами компараторов положительного 5 и отрицательного 6 уровня, а вторые — с соответствующими выходами детектора 2 переходов, триггеры 9,10, входы установки которых соединены с выходами соответствующих элементов И 7 и 8, а выходы — с выходными информационными шинами "единиц" 11 и "нулей" 12, дифференциальный усилитель 13, выход которого соединен с вторым входом сумматора 1, а входы — с соответствующими выходными информационными шинами и входами элемента ИЛИ 14, выход которого через элемент 15 задержки соединен со входами обнуления триггеров 9 и 10. 1 з.п. ф-лы, 2 ил, 1156246

Изобретение относится к технике передачи цифровых данных через приводные линии связи с трансформаторной развязкой и может исполь5 зоваться непосредственно для демодуляции сигналов, модулированных кодом с расщепленной фазой, а при выполнении дополнительной операции декодирования — и других разновидностей двухфазных самосинхронизирующихся кодов, имеющих переходы в центре каждого разрядного интервала (центральные переходы).

Целью изобретения является повы- 15 шение помехоустойчивости.

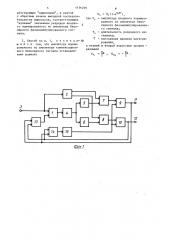

На фиг. 1 представлен пример устройства, реализующего способ демодуляции биполярного фазоманипулированного сигнала, ma фигуре 2 — времен- 20 ные диаграммы работы устройства.

Устройство, реализующее способ демодуляции биполярного фазоманипулированного сигнала, содержит сумматор 1 и детектор 2 переходов, входы которых соединены с входной шиной 3,. интегрирующий фильтр 4 (интегратор), соединенный с выходом сумматора 1, компараторы положительного (первого порогового) 5 и отрицательного (вто- 30 рого порогового) 6 уровня, соединенные с выходом интегрирующего фильтра, элементы И 7 и 8, первые входы которых соединены соответственно с выходами компаратора положительного

5 и отрицательного 6 уровня, а вторые»- с соответствующими выходами детектора 2 переходов, триггеры 9, 10, входы установки которых соединены с выходами соответствующих элемен- 40 тов И 7 и .8, а выходы — с выходными информационными шинами "единиц" t1 и "нулей" 12, дифференциальный усилитель 13, выход которого соединен с вторым входом сумматора 1, а входы " 45 с соответствующими выходными информационными шинами и входами элемента

ИЛИ 14, выход которого через элемент

15 задержки соединен с входами обнуления триггеров 9 и 10.

Работает устройство следующим образом.

Пусть на вход поступает сигнал, соответствующий кодовой последовательности 11001 (см. фиг. 2,а) ° В ка-55 честве интегрирующего фильтра 4 используется интегратор, а в качестве детектора 2 переходов — компаратор нулевого уровня.

Исходное состояние схемы характеризуется нулевыми значениями сигналов на входе устройства и на выходах всех его элементов, кроме детектора

2 переходов (компаратора нулевого уровня) (см. фиг..2,е; 2,f), которые не могут повлиять на состояние других элементов.

При поступлении кодового сигнала (см. фиг. 2,а) на входную шину 3 устройства, состояния выходов детектора 2 переходов (компаратора нулевого уровня) принимают определенные значения, соответствующие прямой (см. фиг. 2,е) и инверсной (см. фиг. 2,f) формам входного сигнала. Однако это не может изменить состояние других элементов устройства. Одновременно с этим входной сигнал, воздействуя через сумматор 1 на вход интегрирующего фильтра 4, начинает изменять состояние его выхода (см. фиг. 2,в), увеличивая уровень сигнала при " 1" и уменьшая при "0" значения первого разряда.

В момент времени t (см. фиг. 2,в) выходное напряжение интегрирующего фильтра 4 достигает пороговый уровень одного из компараторов и вызывает изменение состояния компаратора 5 положительного уровня (см. фиг. 2,с) при "единичном" значении разряда или компаратора .6 отрицательного. уровня (см. фиг. 2,d) при его "нулевом" значении, Однако это также не может изменить состояние других элементов устройства.

Работа логической части устройства происходит по жесткой программе и начинается в момент времени t соответствующий поступлению центрального перехода кодового сигнала (см. фиг. 2,а), который изменяет состояние выходов (см. фиг, 2,е,f) детектора 2 переходов. Это приводит к совпадению сигналов (см. фиг. 2. с,f) и срабатыванию элемента И 7 при "единичном" или к совпадению сигналов (см. фиг. 2,d,е) и срабатыванию элемента И 8 при "нулевом" значении первого разряда. Срабатывание элементов

И 7 или 8, в свою очередь, приводит к срабатыванию триггера 9 или 10 и возбуждению информационных шин "единиц" 11 или "нулей" 12 и возбуждению соответствующих входов дифференциального усилителя 13 и элемента ИЛИ 14 (cM фиг. 2h,i). Импульсы, прошедшие

1 1 56246

То

Uñ (1 е 2 ) где 0

40 через элемент ИЛИ 14 (см фиг, 2„p) поступают на вход элементов 15 за- . держки с запаздыванием, номинальное

То 5 значение которого равно -о — на вхо2 ды обнуления триггеров 9,10, возвращая триггеры и все связанные с ними цепи в исходное состояние (см. фиг ° 2g, 10

h,i,j). На этом процесс формирования выходного импульса, соответствующего информационному значению первого разряда входного сигнала, заканчивается. .15

Выходные информационные импульсы, воздействуя на входы дифференциального усилителя 13, преобразовываются

/ в энакопеременный, нормированный по амплитуде сигнал компенсации 20 (см. фиг. 2,j), который поступает на второй вход сумматора 1.

При этом амплитуда нормированного по амплитуде компенсационного биполярного сигнала устанавливается равной амплитуда входного нормированного по амплитуде бипо-. лярного фазоманипулированного сигнала; длительность разрядного интервала, — постоянная времени интегри35 рирования (интегратора), а первый и второй пороговые

J уровни — равными

Uñ 0с

U U п

Для устранения критичности к уровням выходных "нулевого" и "единич1I

45 ного импульсов и уменьшения ошибок целесообразно использовать в устройстве дифференциальный усилитель с нелинейной передаточной характеристикой, который содержит два логических элемента (схемы) с открытым коллекто- 50 ром, образующих входы дифференциального усилителя, выходы которых через иагрузочные резисторы соединены с источником питания, а также прямой и инвертирующий усилители тока, входы которых через масштабные резисторы соединены с выходами схем с открытым коллектором, а их выходы образуют выход дифференциального усилителя и через резистор соединены с общей шиной

Формула. изобретения

1. Способ демодуляции биполярного фазоманипулированного сигнала, включающий суммирование нормированных по амплитуде входного биполярного фазоманипулированного и компенсационного биполярного сигналов, интегрирование суммарного сигнала, формирование двух основных и двух выходных последовательностей импульсов, соответствующих "единичным" и "нулевым" значениям разрядов входного нормированного по амплитуде биполярного фазоманипулированного сигнала, при этом длительности импульсов первой и второй основных последовательностей импульсов равны интервалам времени выхода величиной проинтегрированного суммарного сигнала за пределы области, ограниченной первым и вторым пороговым уровнями соответственно, и формирование компенсационного биполярного сигнала, о т л и ч а ющ.и и с я тем, что, с целью повышения помехоустойчивости, из входного нормированного по амплитуде биполярного фазоманипулированного сигнала формируют первую дополнительную последовательность импульсов, соответствующих переходу входного биполярного фазоманипулированного сигнала через ноль от положительного уровня к отрицательному, и вторую дополнительную последовательность импульсов, соответствующих переходу через ноль входного биполярного фазоманипулированного сигнала от отрицательного уровня к положительному, при этом фор. мирование выходных последовательностей импульсов, соответствующих "единичным и "нулевым значениям разрядов входного нормированного по амплитуде биполярного фазоманипулированного сигнала осуществляют при совпадении во времени импульсов соответствующих основных и дополнительных последовательностей импульсов, длительность каждого выходного импульса устанавливают постоянной и равной половине разрядного интервала, а компенсационный биполярный сигнал получают путем суммирования выходной последовательности импульсов, соот115624б т.

- о

10 а первый равными:

0с

Uc

2 ветствующих "единичным", и взятой с обратным знаком выходной последовательности импульсов, соответствующих

"нулевым" значениям разрядов входного нормированного по амплитуде биполярного фазоманипулированного сигнала.

2. Способпоп. 1, отличаюшийся тем, что амплитуду нормированного по амплитуде компенсационного биполярного сигнала устанавливают равной:

U = U- (g е -) к с где U — амплитуда входного нормированного по амплитуде биполярного фазоманипулированного сигнала; длительность разрядного интервала, постоянная времени интегрирования, и второй пороговые уровни—

1156246

Составитель Б.Ефанов

Техред Л.Сердюкова

Редактор П.Горькова

Корректор В.Гирняк

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 1431

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4