Селектор импульсов по длительности

Иллюстрации

Показать всеРеферат

СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ , содержащий первый экспоненциальный квазиселектор, вход которого соединен с входной шиной, а выход - с первой выходной шиной, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения селекции импульсов заданной длительности при сохранении длительности входных импульсов, в него введены вторая выходная шина, второй и третий экспоненциальные квазиселекторы, первый и второй инверторы и элемент совпадения , выход которого соединен с второй выходной шиной, первый вход с первой выходной шиной, второй вход - через цепочку, состоящую из последовательно соединенных первого инвертора, второго экспоненциального квазиселектора, второго инвертора и третьего экспоненциального квазиселектора , с входной шиной.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК ((9) () l) 4(5!) Н 03 К 5/19

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

%ИЬИН:. i !.,» . .

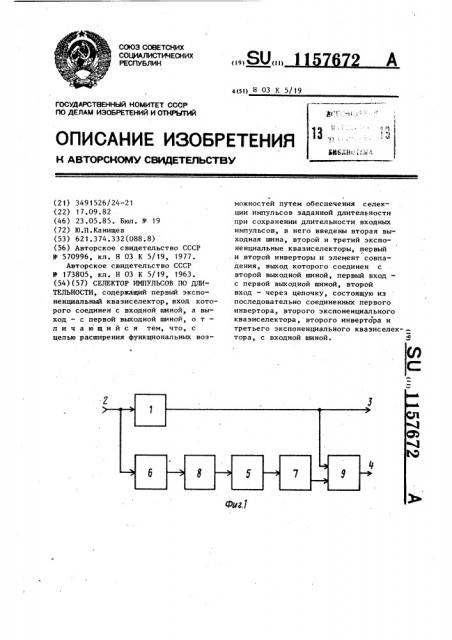

Фиг.1

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

f10 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3491526/24-21 (22) 17.09,82 (46) 23.05.85. Бюл. N - 19 (72) Ю.П.Канищев (53) 62 1.374.332(088.8) (56) Авторское свидетельство СССР

У 570996, кл. Н 03 К 5/19, 1977

Авторское свидетельство СССР

В 173805, кл. Н 03 К 5/19, 1963. (54) (57) СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ, содержащий первый экспоненциальный квазиселектор, вход которого соединен с входной шиной, а выход — с первой выходной шиной, о т— л и ч а ю шийся тем, что, с целью расширения функциональных воз/ можностей путем обеспечения селекции импульсов заданной длительности при сохранении длительности входных импульсов, в него введены вторая выходная шина, второй и третий экспоненциальные квазиселекторы, первый и второй инверторы и элемент совпадения, выход которого соединен с второй выходной шиной, первый вход— с первой выходной шиной, второй вход — через цепочку, состоящую из последовательно соединенных первого инвертора, второго экспоненциального квазиселектора, второго инвертора и третьего экспоненциального кваэиселектора, с входной шиной.

1157672

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и в системах обработки импульсных сигналов.

Цель изобретения — расширение функ-5 циональных возможностей путем обеспечения селекции импульсов заданной длительности при сохранении длительности входных импульсов.

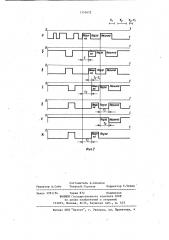

На фиг. 1 приведена электрическая структурная схема селектора, на фиг. 2. - диаграмма импульсов по длительности

Селектор импульсов по длительности содержит первый экспоненциальный 15 квазиселектор 1, вход которого соединен с входной шиной 2, выход — с первой выходной шиной 3, вторую выходную шину 4, второй 5 и третий 6 экспоненциальный квазиселекторы, первый 20

7 и второй 8 инверторы и элемент 9 совпадения, выход которого соединен со второй выходной шиной 4, первый вход - с первой выходной шиной 3,,второй вход через цепочку, состоя- 25 щую из последовательно .соединенных первого инвертора 7, второго квазиселектора 5, второго инвертора 8 и третьего квазиселектора 6 — с входной шиной 2.

ЗО

Селектор импульсов по длительности работает следующим образом.

Квазиселектор 1 выпеляет импульсную последовательность с длительностью импульсов., превышающей ."

35 верхнюю заданную границу, квазиселектор 6 выделяет импульсную последовательность с длительностью импульсов, превышающей à — нижнюю заданную границу. Для выравнивания по длительности образующихся на выходах квазиселекторов 1 и 6 импульсных по" сылок к выходу квазиселектора 6 через инвертор 8 подключен квазиселектор 5, Если !.". С„ — г то с помощью кваэиселектора 5, настроенного на выделение импульсных посылок с длительностью, превышающей 6 - осуществляется выравнивание задержек на выходах квазиселекторов 1 и 5.

Если 4 — -,, то выравнивание задержек должно осуществляться не одним, а- несколькими последовательно соединенными через инверторы квазиселекторами. Для каждого дополнительного квазиселектора устанавливается задержка (порог селекции импульсов) по времени меньше, чем Я., Однако сумма задержек за счет подключения дополнительных квазиселекторов устаг навливается равной величине 1. В результате этого соответствующие посылки на выходе квазиселектора 1 и после всех последовательно соединенных квазиселекторов оказываются выравненными во времени.

На шину 2 поступают сигналы в виде потенциальных импульсных посылок и пауз между ними. Поступившие сигналы преобразуются квазиселекторами

1 и 6 в инверсные сигналы, задержанные относительно поступивших соответственно на время Е и L . Кроме того, на выходах квазиселекторов 1 и 6 не воспроизводятся импульсные посылки, длительность которых меньше величин и У, соответственно.

Выравнивание во времени сигналов с выходов квазиселекторов 1 и 6 осуществляется квазиселектором 5. Импульсные посылки длительностью от до L выделяются элементом 9, на первый вход которого поступают сигналы с выхода квазиселектора 1, а на второй вход — сигналы с выхода инвертора 7. Импульсные посылки с длительностью, превышающей -, поступают также на шину 3, а посылки с длительностью от Г, до Х„ воспроизводятся на шине 4.

Импульсные посылки, длительность которых превышает 2, на шине 4 не воспроизводятся, поскольку в эти моменты времени на входах элемента

9 действуют импульсы противоположной полярности. Возможные на шине 4 кратковременные помехи по причине несовпадения конфигурации фронтов импульсов на входах элемента 9 могут быть устранены путем подключения к выходу элемента 9 относительно общей шины конденсатора или путем подключения к шине 4 дополнительного квазиселектора.

1157672

Составитель А. Соколов

Редактор А.Сабо ТехредМ.Гергель Корректор С.Черни

Заказ 3391/54 Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4