Устройство для выполнения быстрого преобразования фурье

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ по авт.св. 913392; о тли ч а ю щ ее с я тем, что, с целью повышения точйости вычислений, в него введены второй блок памяти, третий и четвертый коммутаторы, второй и третий сумматор1 1-вь1читат1вли, восьмой регистр , сдвиговый регистр, три счетчика , два генератора точек импульсов, три группы элементов ИЛИ, четыре группы элементов И, два элемента ИЛИ и д ешифратор, причем рнформационньй вход второго блока памяти соединен с выходом первого сумматора-вычитателя , вьЬсод второго блока памяти подключен к информационному входу третьего ко 1мутатора, первый выход которого соединен с информационным входом четвёртого коммутатора, вьпсод которого подключен к первому информационному входу второго суммгторавычитатёля , выход которого соединен с информационным входом восьмого регистра, информационньй выход которого подключен к втЬрому входу второго сумматора-вьмитателя и первьи входам элементов ИЛИ первой группы, вторые входы которых соединены с вторым выходом третьего коммутатора, выходы разрядов первого счетчика соединены соответственно с первыми входами элементов И первой и второй групп, выходы которых подключены соответственно к первым и вторым входам элементов ИЛИ второй группы, выходы которых подключень к первым входам элементов И третьей группы, первому информационному входу третьего сумматора-вычитателя и информационному входу сдвигового регистра, выход которого соединен с вторм информационным входом третьего сумматора-вычитателя , выход которого под (Л ключен к первым входам элементов ИЛИ третьей группы, выходы которых соединены с адресным входом второго блока памяти, выход переполнения второго (счетчика соединен с вторыми входами эле,ментов И первой группы, первыми входами первого элемента ШШ и дешифратора и входом запуска первого генератора пачек импульсов, выход коел торого подключен к первому входу ч тоQD О рого элемента ИЛИ, выход которого соединен с тактовьм входом восьмого САЭ регистра и счетным входом третьего | счетчика, выход первого разряда которого подключен к управляющим входам третьего и второго сумматоров-вычитателей, выход второго разряда третьего счетчика соединен с управляющим входом сдвигового регистра, вторыми входами элементов И третьей группы и вторым входом дешифратора, выход которого подключен к управляющему входу четвертого коммутатора, выход третье

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕ ОНИ Х

РЕСА УБЛИН (19) (11!

4(5l) G 06 F 15 332

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (:, 1;, 1 (А

ОПИСАНИЕ ИЗОБРЕТЕНИЯ . ц

И АВТОРСКОМУ СВИДЕ ГЕЛЬСТВУ I Л (61) 913392 (2 1) 3652966/24-24 (22) 14.09.83 (46) 30.05.85. Бюл. N - 20 (72) А.Н. Баранов, 10.Г. Древс и А.В. Казанский (71) Московский ордена Трудового

Красного Знамени инженерно-физический институт (53) 681.32(088.8) (56) Авторское свидетельство СССР

В 913392, кл. G 06 Р 15/332, 1980. (54)(57) УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ

БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ по авт.св. В 913392, о т л и ч а ю щ ее с я тем, что, с целью повышения точности вычислений, в него введены второй блок памяти, третий и четвертый коммутаторы, второй и третий сумматоры-вычитатели, восьмой регистр, сдвиговый регистр, три счетчика, два генератора точек импульсов, три группы элементов ИЛИ, четыре группы элементов И, два элемента

ИЛИ и дешифратор, причем информационный вход второго блока памяти соединен с выходом первого сумматора-вычитателя, выход второго блока памяти подключен к информационному входу третьего коммутатора, первый выход которого соединен с информационным входом четвертого коммутатора, выход которого подключен к первому информационному входу второго сумматоравычитателя, выход которого соединен с информационным входом восьмого

:регистра, информационный выкод которого подключен к второму входу второго сумматора-вычитателя и первьм входам элементов ИЛИ первой группы, вторые входы которых соединены с вторым выходоМ третьего коммутатора, выходы разрядов первого счетчика соединены соответственно с первыми входами элементов И первой и второй групп, выходы которых подключены соответственно к первым и вторым входам элементов ИЛИ второй группы, выходы которых подключены к первым входам элементов И третьей группы, первому информационному входу третьего сумматора-вычитателя и информационному входу сдвнгового регистра, .выход которого соединен с вторым информационным входом третьего сумматора-вйчитателя, выход которого подключен к первым входам элементов ИЛИ третьей группы, выходы которых соединены с адресным входом второго блока памяти, выход. переполнения второго счетчика соединен с вторыми входами элементов И первой группы, первыми входами первого элемента ИЛИ и дешифратора и входом запуска первого генератора пачек импульсов, выход которого подкпючен к первому входу торого элемента ИЛИ, выход которого соединен с тактовым входом восьмого регистра и счетным входом третьего счетчика, выход первого разряда которого подключен к управляющим входам третьего и второго сумматоров-вычитателей, выход второго разряда третье го счетчика соединен с ynpàâëÿþùaè входом сдвигового регистра, вторыми входами элементов И третьей группы и вторым входом дешифратора, выход которого подключен к управляющему входу четвертого коммутатора, выход третье115903

ro разряда третьего счетчика соединен с третьим входом дешифратора и третьими входами элементов И третьей группы, выход которых подключены к вторым входам соответствующих элементов

ИЛИ третьей группы, выход первого щ разряда второго счетчика соединен с вторыми входами элементов И второй группы, вторым входом первого элемента ИЛИ и входом запуска второго генератора пачек импульсов, выход которого подключен к второму входу вто.рого элемента ИЛИ, выход riepaoro эле1 мента ИЛИ соединен с управляющим входом третьего коммутатора, выходы элементов ИЛИ первой группы являются информационным выходом устройства, тактовые входы первого и второго счетчиков объединены и являются тактовым входом устройства, выходы разрядов первого счетчика соединены с первыми входами соответствующих элементов И четвертой группы, первый и второй инверсные входы которых соединены соответственно с выходом первого разряда второго Счетчика.

Изобретение относится к вычислительной технике, в частности-к цифровой обработке сигналов, и может быть использовано при создании устройств, . 1 выполняющих спектральный и корреляционный анализ сигналов °

Предлагаемое. устройство является усовершенствованием устройства по авт.св. 9. 913392, кл.. G 06 F 15/332, 1980 r. 10

Цель изобретения — увеличение точности вычисления БПФ.

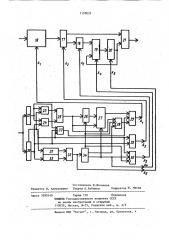

На чертеже представлена функциональная схема предлагаемого устройства. 15

Устройство содержит регистры 1 -4, сумматор-вычитатель 5, коммутатор 6, блок 7 умножения, коммутатор 8, регистры 9, 10 и 11, блок 12 памяти, блок 13 вычисления целой части, сос- >О тоящий из регистра 14 сдвига сумматор 15„, счетчик 1б, коммутаторы 17 и 18, сумматор»вычитатель 19, регистр 20 группу элементов ИЛИ 21, I счетчик 22, группы элементов И 23 и

24 ° группу элементов ИЛИ 25, сдвиговый регистр 26 сумматор-вычитатель

27, группу элементов И 28; группу элементов ИЛИ 29, счетчик ЗО, гене- раторы 3.1 и 32 пачек импульсов, элемент ИЛИ 33, счетчик 34, элемент

ИЛИ 35, дешифратор Зб, группу элементов И 37.

Генераторы 31;и 32 пачек импульсов выдают пачку из трех импульсов и пачку из пяти импульсов. Счетчики

30 и 34 — соответственно двух- и трехразрядный, разрядность счетчика

22 определяется размером выполняелого БПФ.

Устройство работает следующим образом.

Синхроимпульсы поступают на тактовый вход устройства.и подсчитываются в счетчиках 22 и 30. В счетчике 22 определяется двоичный код обрабатываемой гармоники, а счетчик 30 является управляющим, причем для того, чтобы не пропустить невосстаиовленной гармонику с номером два логика счетчика 30 организована так, чтобы сигнал переполнения формировался .в случае появления в нем кода "01".

Это, например, осуществляется путем формирования, сигнала непереполнения на выходе элемента И, один вход которого соединен с прямым. выходом второго разряда, а другой — с инверсным выходом первого. Если код восстанавливаемой гармоники не является не-. четным или кратным 2 + 48, то эле-, .менты .И 28 и 24 групп закрыты нулевыми сигналами с выходов первого разряда и переполнения счетчика 30 и код гармоники через открытую группу элементов И 37 и группу элементов ИЛИ 29 поступает на адресный вход блока памяти, На выходе элемента ИГЛ 35 присутствует нулевой потенциал, который определяет адрес коммутатора 17 . Вход коммутатора

17 подключается к его второму выходу, и информация, считанная из блоз 11590 ка памяти пд указанному адресу через коммутатор 17 и группу элементов ИЛИ 21 поступает на выход устройства без обработки. .Если код счетчика 22 нечетный, т.е. в младшем разряде счетчика 30единица, то содержимое счетчика через открытые элементы И 24 группы поступает на входы элементов ИЛИ 25 группы и далее на вход сдвигового 1р регистра 26, один из входов сумматора-вычитателя и входы элементов

И 28 группы. Одновременно. этот же сигнал с выхода иервого разряда счетчика ЗО закрывает-элементы И 37 группы:, устанавла@ает единичное значение на выходе .эдеиента ИЛИ 35 (коммутатор 17 подключает свой вход к своему первому выкоду) и запускает генератор 32, которв@. выцает пачку щ

as пяти импульсов на своем выходе.

Эти импульсы через элемент ИЛИ 33 поступают на вход счетчика.-34. По приходе первого импульса от генера.тора 32 в счетчике 34 устанавливаетсяд код 100. Нулевые потенциалы с выходов второго.и третьего разрядов счетчика 34 поступают на инверсные вхо- ды элементов И 28 группы, разрешая прохождение кода с выходов элементов

ИЛИ 25 группы через элементы ИЛИ 29 группы на адресный вход блока памяти. Происходит вЫборка значения .Х„ и запись его в регистр 20 (установлен в ноль) через коммутаторы 17 и 18 (35 и сумматор-вычитатель 19. При этом сдвига 1ц коммутатором 18 не происходит. При поступлении второго импульса элементы И 28 группы закрываются, и информация записывается в

31 4 сдкнговый регистр 26, где осуществляется сдвиг на три разряда;: более, передача этого кода в сумматор-вычитатель 27, в котором находится код адреса К + 8К следующего отсчета, необходимого для восстановления.

Полученный код через группу элементов ИЛИ 29 передается на адресный вход блока памяти.. Управляющий сигнал с выхода дешифратора 36, поступая на адресный вход коммутатора 18, осуществляет в последнем сдвиг на 3 разряда (деление на 8). Результат вычитания заносится в регистр 20.

Аналогичные действия происходят при поступлении третьего импульса в счетчик 34. В случае подачи четвертого и пятого импульсов в счетчик

34 основное отличи в работе устройства состоит в том, что в сдвиговом регистре 26 и коммутаторе 18 сдвиг происходит на 4 разряда, а не на 3.

После накопления пяти импульсов .в счетчике 34 он сбрасывается в ноль (для этого логика счетчика. организована, например, подключением выхода элемента Ц к входу обнуления, а его входов — к соответствующим выходам разрядов).

Если же номер обрабатываемой гармоники удовлетворяет условию 2+48, то работа устройства полностью аналогична описанной с той лишь разницей, что генератор 31 запускается сигналом .с выхода переполнения счетчика 30 и выдает три импульса по своему первому выходу. Результат вычислений с выхода регистра 20 поступает через группу элементов ИЛИ 21

l на выход устройства.

115903!

Составитель И.Логачева

Редактор Л. Алексеенко Техред А.Бабинец Корректор И. Иуска

Заказ 3590/49 Тираж 710 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4