Программируемая логическая матрица

Иллюстрации

Показать всеРеферат

ГГРОГРАМ№ РУЕМАЯ ЛОГИЧЕСКАЯ МАТРИЦА, содержащая первую матрицу 2 ti-f элементов связи, где 2 cL - число строк данной матрицы, а - число термов программируемой логической матрицы, вторую матрицу yjу элементов свяэи, где дчисло строк Д9ННОЙ матрицы,

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (11) raCyl ma ИО@ИТ Т ССС1

ГВ ДЯЛМЮ ИЭОБ КТаНИй И ото Итий

ОПИСАНИЕ ИЗОБРЕТ н аЬтжжом с кткльствм (21) 3604622/24-24 (22) 13.06.83 (46) 30.05.85 ° Вюп. Ф 20 (72) АЛ.Плахтеев и А.В.Брезгунов (53) 681.327.16(088.8) (56) Авторское свидетельство СССР

Ф 139651, кл. 6 11 С 15/04, 1980.

Авторское свидетельство СССР .IP 935945, кл. С 06: Р 7/00, 1980.

/ (54),(S7) ПРОГРАИИИРУЕИАЯ ЛОГИЧЕСКАЯ

ИАТРИЦА, содержащая первую матрицу

2 е у элементов связи,. где 2 с — чис,ло строк данной матрицы, а т — число териов программируемой логической матрицы, вторую матрицу у элементов связи, где p — - число строк данной матрицы, (2 at + /Ъ ). у элементов памяти, выходы которых соединены с управляющими входами соответ. ствующих элементов связи, g инверторов, входы которых соединены с нечетнмюи, а выходы — с четными горизонтальными шинами первой матрицы, о т л и .ч а ю щ а я с я тем, что, с целью повышения надежности программируемой логической матрицы, она содержит первый регистр, входы которого являются информационными входами программируемой логической иатрицы, а выходы соединены с входаии соответствуняаих инверторов, второй регистр, 2о(+ p коммутаторов, первые входы которых соединены с соответствующими выходаии второго регистра,.выход каждо го нэ коммутаторов соединен с входои первого элемента памяти нэ соединенных последовательно в каждой строке первой и второй матриц, а второй вход - с выходом последне- го элемента памяти данной строки, блок управления, первый выход когорого соединен с вторыии входами элементов памяти, третий регистр, блок сравнения, четвертый регистр, выходы которого являются информационными выходами программируемой логической матрицы, а входы соедимены с одноименными входами первой ° группы входов блока сравнения и вьиодами третьего регистра, входы которого соединены с соответствующими горизонтальными шинами второй матрицы и входами второй группы входов блока сравнения, выход кото- .

-рого соединен с первым входом блока управления, второй вход которого является выходом сигнала ошибки программируемой логической матрицы, третий выход соединен с управляющими входами первого и четвертого регистров, четвертый выход соединен с управляющим входом третьего регистра, второй вход, блока управления соединен с управляющим входом второго регистра и является сннхровходом программируемой логической матрицы, третий вход соединен с установочными входами регистров и с управляющими входами коимутаторов и является управляющим входои програимируемой логической . матрицы, четвертый вход блока .управления является входом установки режима самопроверки.

6 2 дов на выходах второй матрицы, получаемых при сдвиге на К (2 (К (э- и определяется сигналом на входе 19) разрядов. В ПЛИ без дефектов сравниваемые коды должны быть одинаковыми. Режимы работы ПЛИ следующие: режим настройки (ввода настроечной информации) и режим обработки вход-. ной информации.

В исходном состоянии на входах 16, 17, 18, 14, выходах 15 и 20 — нулевые сигналы.

Соответственно в регистре 5 хранятся нулевые коды, элементы памяти 2 „ - 2(Zg 1.p ) в исходном состоянии.

В режиме настройки на вход 18 поступает единичный сигнал, устанавливающий регистры 8 и 10 в нупевое состояние. При этом в (2 о + P ) разрядный регистр 5 разрешается прием настроечной информации со входа 16 под воздействием сигналов синхронизации на входе 17. Коммутаторы 6„ - 6(, +э)подключают (в режиме настройки) выходы регистра 5 к

1 f входам элементов памяти 2„ — ?(p), являющихся первыми разрядами (2d, +

+ pj) регистров сдвига. !

Настроечная ирформация, определяющая функции- ПЛИ, представляется в виде кодов разрядностью (2ш + p), таким образом после записи кодов

Ф в элементы памяти 2, — 2(+ процесс настройки заканчивается..

Настроечная информация поразрядно поступает на вход 16 синхронно с сигналами со входа 17. После ввода. (2о(+ ) разрядов кода настройки в ре истр 5 блок 7 выдает сигнал, разрешающий перезапись информации

I иэ регистра 5 в элементы памяти 2

I I

2(„ !,. предварительно информация из элементов 2, = 1 ъ 1 ) переписывается в элемен0 (1" 1 (,.1! ты 2, — 2 (+ (происходит синхронный сдвиг информации в (2в(+ p ) регистрах сдвига). В течение (2 а(, + /5 ) Э тактов . вводится - кодов настройки.

В режиме обработки входной информации на вход 18 поступает нулевой сигнал, коммутаторы 6, — 6(,, отключают входы элементов памя.ти 2 q — 2(, разрядов регист-! ров сдвига от соответствующих выхо-, дов регистра 5 и соединяют эти. входы с выходами соответствующих 2,—

2 „ + элементов памяти (старших

l 115906

Изобретение относится к вычислительной технике и может быть использовано в устройствах управпения и специализированных вычислителях, в которых предусмотрен режим самопро5 верки.

Целью изобретения являе1ся повышение надежности программируемой логической матрицы (ПЛИ) путем введения средстч самопроверки. t0

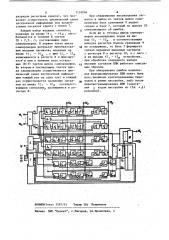

На чертеже представлена схема предлагаемого устройства.

ПЛИ содержит элементы связи перaoA М H второй 1г, . !ZAN, (г 1 .у матриц, (2d + p ) элементов памяти 2, * инверторов 3, первый (входной) регистр 4, второй регистр 5, предназначенный для ввода настроечной информации, коммутаторы Ь, блок управления 7, третий (буферный) регистр 8, блок сравнения 9, четвертый (выходной) регистр .10. Элементы связи первой матрицы подключены к 2 -горизонтальным шинам 11, а элементы сВязи BtopoH матрицы — к р- Горизон тальным шинам 12, г-вертикальных шин 13 являются общими для первой и второй матриц. Информационные входы первбго регистра 4 и выходы четвертого регистра !О являются

30 соответственно информационными входами 14 и выходами 15 IIJIN, вход вто,рого регистра 5 является входом 16 настроечной информации ПЛИ. Блок управления 7 имеет четыре вхбда и четыре выхода: первый вход соеди- Зэ нен с выходом блока сравнения 9, второй 17, третий 18 и четвертый 19 входы являютсч соответственно синхровходом 11ЛИ, управляющим входом ПЛМ и входом установки режима самопроверки, первый выход соединен со вторыми входами элементов памяти 2, второй выход является выходом 20 сигнала ошибки, третий выход соединен с управляющими входами первого 4

45 и четвертого 10 регистров, а четвертый выход — с управляющим входом третьего регистра 8.

Информация, записанная в элементах памяти 2, фиксируется в соответствующих элементах . вязи 1, каждый иэ которых выполнен, например, на двух ИДП транзисторах. Каждая строка элементов памяти представляет собой кольцевой регистр сдвига, уп- И равляемый сигналами с первого выхода блока управления 7. В основе принципа самопроверки лежит сравнение ко15

77

t9

ВНИИПИ Заказ 3597/51 Тираж 584 Подписное

Филиал ПНП "Патент", r .Óëòîðîä, ул.Проектная, 4

3 11590 разрядов регистров. сдвига), что позволяет осуществлять циклический сдвиг настроечной информации под воздействием сигналов сдвига с блока 7.

Каждый набор входных сигналов, поданных на входы 14 — 14, обрзбатывается в течение К тактов (К = 2,3...), составляющих цикл самопроверки. В первом такте цикла самопроверки результат преобразования входных сигналов; поданных на входь, 14, — 14, с шин 12„. — 12 записывается в регистр 8 и фиксируется в нем в течении всех осталь\ ныл (К-1) тактов цикла самопроверки.

Во втором и последующих тактах цикла самопроверки осуществляется циклический сдвиг настроечной информации каждый раз на один такт и каждый раз осуществляется сравнение сигналов на шинах 12 z — 12 > соответствующими сигналами хранящимися в реУ гистре 8.

66 4

При обнаружении несовпадения сигналов в любом ич тактов цикла самопроверки блок сравнения 9 выдает сигнал в блок 7, который по выходу 20 сигнализирует об ошибке °

Если же в течении цикла самопроверки несовпадение кодов на шинах 12„ - 12> и соответствующих выходах. регистра блоком сравнения. 9 не оонаружено, то блок 7 формирует.. сигнал передачи выходных сигналов с регистра 8 в регистр 10, à с него— и на вьгходы 15 „ — 15 устройства.

Дри обработке очередного набора входных c:òíàëîâ ПЛИ работает описанным образом.

При обнаружении ошибки нормальное функционирование ПЛИ может быть восс.ановлено кратковременным переходом в режим настройки, либо после перепрограммирования ПЛИ (занесения кодов. настройки по (2с + ) разрядов).