Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

ПОСТОЯННОЕ ЗАПОШНАЮЩЕТ: УСТРОЙСТВО, содержащее первый накопитель , выходы которого соединены со входами первой группы коммутатора , выходы которого являются информационными выходами устройства, входы, первой и второй групп накопителя являются адресньми входами ййЫШОГВй. первой и второй групп устройства, второй, третий и четвертый накопители , входы которых объединены, выходы второго накопителя соединены со входами второй группы коммутатора , выходы третьего накопителя соединены со входами первой группы блока сравнения, входы второй группы которого соединены со входами первой группы первого накопителя , о т.л ичающеёся тем, чта, с целью повышения информационной емкости запоминающего устройства , оно содержит дешифратор, выходы которого соединены со входами третьей группы коммутатора, а вход| первой и второй групп - с выходами соответственно блока сравнения и четвертого накопителя, входы второго , третьего и четвертого накопителей соединены со входами второй группы первого накопителя.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (И), С 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ,КОМИТЕТ. СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3624149/24-24 (22) 15.07.83 (46) 30.05.85. Бюл. Ф 20 (72) И.A.Äè÷êà, В.И.Корнейчук и В.Я.Юрчишнн (71) Киевский ордена Ленина политехнический институт им. 50-летия

Великой Октябрьской социалистической революции (53) 621.327.6(088.8) (56) Патент США В 3588830, кл. 340/122, опублик. 1971.

Патент С!ИА В 3665426, кл. 340/173, опублик. 1972. (54)(52) ПОСТОЯННОЕ ЗАПОИИНА)0ЩЕ ;

УСТРОЙСТВО, содержашее первый накопитель, выходы которого соединены со входами первой группы .коммутатора, выходы. которого являются информационными выходами устройства, входы первой и второй групп накопи- . теля являются адресными входами первой и второй групп устройства, второй, третий и четвертый накопители, входы которых объединены, выходы второго накопителя соединены со входами второй группы коммутатора, выходы третьего накопителя соединены со входами первой группы блока сравнения, входы второй группы которого соединены со входами первой группы первого накопителя, о.т.л и ч а ю щ е е с я тем, что„. с целью повышения чнформационной емкости запоминающего устройФ ства, оно содержит дешифратор, выходы которого соединены со входами третьей группы коммутатора, а входй первой и второй групп — с выходами соответственно блока сравнения и. четвертого накопителя, входы второго, третьего и четвертого накопителей соединены со входами второй группы первого накопителя.

1159067

Изобретение относится к запоминающим устройствам, н частности к электрически программируемым постоянным запоминающим устройствам, и может быть использовано н автоматике и вычислительной технике.

Целью изобретения является повышение информационной емкости запоминающего устройства.

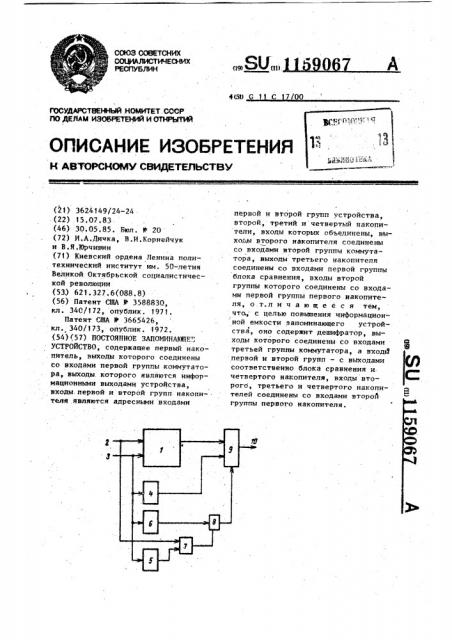

На чертеже представлена структур- 1О ная схема предлагаемого устройстна, Устройство содержит первый накопитель 1, имеющий входы первой группы 2 (входы старших разрядов адреса) и нходы второй группы 3 (входг» младших разрядов адреса), второй накопитель 4, третий накопитель 5, четвертый накопитель 6, блок сравнения 7, ко входам. первой группы которого подключены ныходы третьего накопителя 5. а ко вхолам Второй группы — входы первой группы 2 первого накопителя 1, дешифратор 8, входы первой группы которого соединены с.выходами блока сравнения 7, а входы второй гругнты — с выходами четвертого накопителя 6, и коммутатор 9, к входам перной группы которого подключены выходы первого накопителя 1, к входам второй группы — выходы втoporo накопителя 4 и ко вхо— дам третьей группы — вьгходы дешифратора 8. Выходы 10 коммутатора 9 являются информационными выходами устройства. КО входам второго третьего 5 и четвертого 6 накопителей подключены нходы первой группы 2 первого накопителя

Первый накопитель 1 состоит из

И -разрядных ячеек и условно раз- О с бит на — равных блоков, содержа5 щих по .З ячеек. Каждое слово условно разбивается на †" r -разрядных слогов. Обращение к первому накопителю 1 производится таким образом, что старшие разряды адреса, поступающие на входы первой группы 2 нако:. Ителя 1., указывают номер блока, а младшие разряды адреса, поступающие на входы второй группы 2 — номер ячейки в блоке, Для старших

ll разрядов адреса î-водится а =3ag — г э разрядов адреса, а для млад- ших 1= о : разрядов. Второй накопитель 4 состоит из 5 г -разрядных ячеек, третий накопитель 5 — иэ щ-разрядных ячеек, четвертый 6 накопитель . — иэ 5 Ь -" вЂ,. -разрядньгх ячеек.

Слог длиной г разрядон называется дефектным, если он содержит, хотя бы один Отказавший разряд, Лефектные слоги слОВ пернОГО накопителя 1 г1од меняются истинньгми слогами, хранимыми во втором накопителе 4, а третий 5 и Четвертый 6 накопители хранят информацию необходимую для Определе1 ния места подмены. Для этогс в третий накопитель 5 по адресу, Образованному иэ младших раэрядон адреса ячейки первого накопителя 1, записывают старшие разряды адреса ячейки, в которой необходимо осуществить подмену, а в четвертый 6 накопитель аналогичным образом эалисынают номер лодменяемого слога и слове. Другими словами, в третьем накопителе 5 хранятся коды номеров блоков, в четвертом 6 накопителе — номера слогов (каждое слово состоит иэ слогов с номерами От 0 до (",„ — - 1)-го, содержащих дефекты.

Обращение ко всем четырем накопителям производится одновременно.

При чтении информации из дефектной ячейки первого накопителя 1 номср слога, считанный из четвер" îãî 6 накопителя дешифрируется дешифратором 8 н„ если старшие разряды адреса ячейки первого накопителя 1 совпадают с кодом, считанным иэ третьего накопителя 5 (это Определяется блоком сравнения 7), то с помощью коммутатора 9 осуществляется подмена дефектного слога ячейки первого накопителя 1 кодом, считанным иэ второго накопителя 4, Таким Образом, в устройстве возможна подмена дефектных слогов первого накопителя i причем слово, хранимое в накопителе 1, может содержать не более Одного дефектного слога.

Кроме того, первый накопитепь 1 не допжен содержать и более одноименных слон (слов, принадлежащих различным блокам, у которых младшие разряды адреса.совпадают), содержащих отказы. Если В считанных иэ накопителя 1 словах необходимо подменить более одного слога, то зто легко осуществить путем увеличения разрядности накопителей 4 и 6 (накопитель 5 при этом остается беэ изменений). При подмене слогов в считанном слоне ВО втором 4 нако-3 11 пителе необходимо хранить чч -разрядные коды, а в четвертом б накопителе — ч о — -разрядные. Кроме

2 г того, необходимо иметь либо ч дешифраторов 8, либо считанные из накопителя 6 слова разбивать на

Составитель Г.Бородин

Техреду.Мартяшова Корректор И.Эрдейи

Редактор С.Тимохина

Заказ 3597/51 Тираж 584 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб,, д, 4/5

Филиал ППП "Патент", r.Ужгород, ул.Проектная, 4 ч о 2 †„ -разрядные группы и дешифh рировать их последовательно, Если накопитель 1 построен на полупроводниковых микросхемах-, то подмену удобно осуществлять слогами, длина которых равна длине ячейки микросхем, а накопитель 1 разбивать йа блоки так, чтобы количест во слов, входящих в блок, равнялось количеству ячеек микросхемы. Тогда накопитель 1 не должен содержать две и более микросхем, имеющих дефекты в одноименных ячейках. Подбор микросхем, удовлетворяющих последнему условию, легко осуществить с прИвлечением ЭВИ.

В качестве накопителей 4-6 можно использовать такие же элементы памяти, как и в первом накопителе 1, т.е, содержащие дефекты. Но если . какая-то ячейка одного из накопителей 4-6 содержит дефект, то одно- . именные ячейки двух других накопителей не могут быть испбльзованы для записи в них информации, а, следовательно, и одноименные ячейки всех блоков первого накопителя (по отношению к рассматриваемой ячейке) не должны содержать дефекты:

Пример. Пусть первый нако питель 1 имеет емкость 4К 32-разряд|ных слов и условно разбит на блоки по 256 ячеек в каждом, а ячейка

59067 4 состоит из восьми 4-разрядных слогов

При этом накопители 4 и 5 имеют емкость 256 4-разрядных слов каждый, а накопитель б — 256 3-разрядных

5, слов °

Предположим, что в ячейках nepsoro накопителя 1 с адресами

A 10011001-11 f А = 101100110110

А = 110110100110 А = 001011010010

У ф имеются дефектные слоги, номера которых t 3,4,7 соответственно (каждая отмеченная ячейка накопителя 1 содержит по одному дефектному слогу). Тогда во второй накопитель 4

15 по адресам а 10011111;: a = 00110110 а = 10100110 а = 11010010, образованными из младших разрядов адресов соответствующих ячеек первого накопителя 1, записывают информацию, используемую для подмены, в четвертый накопитель 6 по тем же адресам записывают коды 001, Off„

100 111 а в третий 5 накопитель— коды 1001 1011, 1101, 0010 соответственно. При обращении к адресам А»

А, Л и А первого наконнтеля 1 происходит обращение к адресам а„, а а и а накопителей 4-6. Накопи2. тель 5 выдает старшие разряды адреса, блок сравнения 7 разрешает дешифрованные номера слога, подлежащего подмене, а коммутатор 9 подменяет дефектный слог слогом, считанным

35 из второго 4 накопителя. Таким образом, в рассмотренном примере можно подменить 256 4-разрядных слогов первого накопителя 1, содержащих дефекты.