Двухступенчатый аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ДВУХСТУПЕНЧАТЫЙ АНАЛОГОЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий параллельный аналого-цифровой преобразователь, выходы которого через первый цифроаналоговый преобразователь соединены с первым входом блдка аналогового вычитания, второй вход которого соединен с входом параллельного .аналого-цифрового преобразователя , а - с входом последовательного аналого-цифрового преобразователя, выходы которого соединены с первыми адресными входами блока памяти, отличающийс я тем, что, с целью повышения точ ности преобразования, в него введены аналоговый переключатель и второй цифроаналоговый преобразователь, входы которого подключены к шинам эталонного кода и входам записи блока памяти, а выход - к первому входу аналогового переключателя, второй вход которого соединен с шиной входного сигнала, а выход - с входом параллельного аналого-цифрового.преобразователя , приэтом вторые адрес (Л ные входы блока памяти подключены к выходам параллельного аналого-цифрового преобразователя, а выходы - с шинами выходного кода.

(l9) (l I) СОЮЗ СОВЕТСНИХ

СО1.1ИАЛИСТИЧЕСН ИХ . РЕСПУБЛИН

4(5»1 Н 03 И 1/1О

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ll0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНЯТИЙ (21) 3643150/24 24 (22) 16.09.83 (46) 30.05,85, Бюл. 11» 20 (72) Г. В. Зайцев и И. В. Ложкин (53) 681.325(088.8) (56> 1. Патент Франции 9 2310036, кл. H 03 К .13/12, опублик. 1977.

2, Авторское свидетельство СССР

Р 809543, кл. Н 03 К 13/02, 1977 (прототип). (54)(57) ДВУХСТУПЕНЧАТЫЙ АНАЛОГОЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий параплельный аналого-цифровой преобразователь, выходы которого через первый цифроаналоговый преоб.разователь соединены с первым входом блока аналогового вычитания, второй вход которого соединен с входом параллельного аналого-цифрового преобразователя, а вых» д — с входом последовательного аналого-цифрового преобразователя, выходы которого соединены с первыми адресными входами блока памяти, о т л и ч а ю щ и й— с я тем, что, с целью повышения точ.ности преобразования, в него введены аналоговый переключатель и второй цифроаналоговый преобразователь, входы которого подключены к шинам эталонного кода и входам записи блока памяти, а выход — к первому входу . аналогового переключателя, второй вход которого соединен с шиной входного сигнала, а выход — с входом параллельного аналого-цифрового преобразователя, при этом вторые адресные входы блока памяти подключены к выходам параллельного аналого-цифрового преобразователя, а выходы — с шинами выходного кода.

1159161

Изобретение относится к аналогоцифровым преобразователям и может быть использовано в технике физического эксперимента, в частности в ядер ной электронике, а также в вычислительной технике, гидралокации, радиолокации и технике связи.

Известно устройство аналого-цифрового п« еобразования, содержащее два параллельных аналого-цифровых преоб- !О разователя (ALQI), цифроаналоговый преобразователь (ЦАП1 и блок аналогового вычитания Щ .

Недостаток:. такого устройства— малая точность преобразования.

Наиболее близким па технической сущности к предлагаемому является двухступенчатый аналого-цифровой преобразователь, содержащий параллельный АЦП, блок аналогового вычи- р0 тания, последовательный АЦП, коммутатор, блок памяти и сумматор, выходы . которого соединены с выходной шиной, первые входы — с выходом блока памяти, а вторые входы †. с выходами последа- 5 нательного АЦП и первыми входами блока памяти, вторые входы которого соединены с первыми выходами коммутатора, вторые выходы которого соединены с первыми входами цифроаналаговагс коммутатора и первымвходам последовательного AIUI второй вход которого соединен с выходам аналогового вычитателя, первый вход которого соединен с входнойшиной ивходом параллельного ЛЦ11,а второй вход — с выходом ЦАП, 35 .вторые входы которого соединены с выходами параллельного АЦП и первыми входами коммутатора, вторые входы котарога соединены с шинами эталонного

40 кода 12).

Недостаток этого устройства — невысокая точность коррекции погрешностей двухступенчатого АЦП в целом, так как коррекции подвергаются только погрешности ЦАП. Погрешности параллельного АЦП, блока аналогового вычитания и последовательнага АЦП в этом устройстве не могут быть скорректированы и проявляются на выходе

50 устройства.

Целью изобретения является повьгшение точности преобразования.

Ф

Поставленная цель достигается тем, что в двухступенчатый анапого-цифра- "5 вой преобразователь,содержащий параллельный АЦП,выходы которого через первый ЦА«1соединены спервым входамблака аналогового вычитания, второй вход которого подключен к входу параллельно го AIUI, а выход — к входу последовательного АЦП, выходы которого соединены с первыми адресными входами блока памяти„ введены аналоговый переключатель и второй ЦАП, входы которого подключены к шинам эталонного кода и входам записи блока памяти, а выход - к первому входу аналогового переключателя, второй вход которого соединен с шиной входного сигнала, а выход — с входом параллельного АЦП, при этом вторые адресные входы блока памяти подключены к выходам параллельного ДЦП, а выходы — к шинам выходного када.

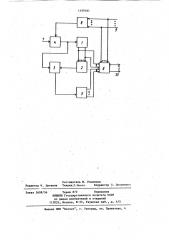

На чертеже представлена функциональная схема двухступенчатого. АЦП.

Устройство содержит параллельный

AIIII 1, первый ЦАП 2, блок 3 аналогоного вычитания, аналоговый переключатель 4, последовательный АЦП 5, блок

6 памяти, шина 7 входного сигнала, второй ЦАН 8, шины 9 эталонного кода, шины 10 выходного кода.

Выходы АЦП 1 с разрядностью.Nl через первый ЦАП 2, разрядность которого также равна Nl соединены с входом блока 3 аналогового вычитания, второй вход которого подключен к входу параллельного АЦП 1 и одновременно к выходу аналогового переключателя

4, выход блока 3 аналогового вычитания соединен с входом паследовательнога АЦП 5 разрядностью 1«2, выходы которого соединены с первыми адресными входами блока 6 памяти, его вторые адресные входы соединены с выходами параллельного АЦП l, первый вход аналогового переключателя

4 соединен с шиной 7 входного сигнала, а второй его, вход - с выходом второго ЦАП 8, имеющего разрядность 03

= Nl + N2 + 1, причем его входы соединены с шинами 9 эталонного кода и входами записи блока 6 памяти, выходы которого подключены к шинам 10 выходного кода двухступенчатого АЦП.

Двухступенчатый АЦП работает следующим образом, В режиме калибровки с шин 9 эталонного кода кодовые слова па".тупают на входы .второго IIAII 8, выходное напряжение которого через аналоговый переключатель 4 поступает на вход параллельного ALIII и одновременно

1159161

3 на вход блока 3 аналогового Ъычитания, в котором выделяется разность выходных напряжений второго ЦАП 8 и первого ЦАП 2, причем выходное напряжение первого ЦАП 2 является аналоговым эквивалентом цифрового слова, поступившего на него с параллельного

АЦП 1.

Разность выходных напряжений второго GAG 8 и первого ЦАП 2 кодируется 10 последовательным АЦП 5 и в качестве кодов младших разрядов поступает на первые адресные входы блока 6 памяти.

На вторые адресные входы блока 6 па- мяти в качестве кодов старших раэря- 15 дов поступает цифровое слово с выходов параллельного АЦП

Одновременно на входы записи блока

6 памяти поступают кодовые слова эталонного кода. Запись .этих кодовых 2б слов по установленному адресу происходит сразу же после изменения состояния младшего разряда последовательного АЦП 5.

Таким образом, двухступенчатый АЦП25 в целом калибруется точным ЦАП 8. Такая калибровка проводится периодически so время работы, чтобы учесть не только неточность отдельных элементов, но и их температурную нестабильность, причем быстродействие вто-,. рого ЦАП 8 может бить существенно ниже быстродействия преобразователя в целом, что значительно облегчает его разработку.

В рабочем режиме сигнал с шины 7

35 входного сигнала через. аналоговый переключатель 4 поступает одновременно на вход параллельного АЦП 1 и на е второй вход блока 3 аналогового вьгчитания, в котором выделяется разность входного сигнала и выходного напряжения первого ЦАП 2, Это выходное нагряжение является аналоговым эквивалентом цифрового слова, поступа- . вшего на первый ЦАП 2 с параллельного

АЦП l.

Сигнал с выхода блока 3 аналогового вычитания кодируется последовательным АЦП 5 и поступает на первый адресный вход блока 6 памяти в качестве кодов младших разрядов. На вторые адресные входы блока 6 памяти в качестве кодов старших .разрядов поступает цифровое слово с выходов параллельного АЦП l. Цифровое слово с выходов считывания. блока б памяти является выходным сигналом двухступенчатого АЦП и поступает на шины выходно-., го кода 10.

Технико-экономический эффект заключается в том, что в рабочем режи" ме в качестве выходного кода используется его более точный эквивалент. определенный в режиме калибровки.

Это позволяет уменьшить нелинейность преобразователя до уровня младшего разряда второго ЦАП 8, т,е. до половины младшего разряда АЦП в целом.

Например, если разрядность. двухступенчатого АЦП равна 12, второй ЦАП 8 должен иметь 13 разрядов, нелинейность

АЦП в целом в этом случае не превышает 0,012Х, в то время как двухступенчатый АЦП той же разрядности с корректировкой "только .характеристики,ЦАП имеет нелинейность 37.

1159161

Составитель И. Романова

Редактор М. Циткина Техред Л.Микег Корректор Л. Пилипенко

Заказ 3608/56

Тираж 872 Подписное

ВНИИПИ Государственного комитета СССР ло делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4